The DENX U-Boot and Linux Guide (DULG) for Canyonlands

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Variable-Length Encoding (VLE) Extension Programming Interface Manual

UM0438 User manual Variable-Length Encoding (VLE) extension programming interface manual Introduction This user manual defines a programming model for use with the variable-length encoding (VLE) instruction set extension. Three types of programming interfaces are described herein: ■ An application binary interface (ABI) defining low-level coding conventions ■ An assembly language interface ■ A simplified mnemonic assembly language interface July 2007 Rev 1 1/50 www.st.com Contents UM0438 Contents Preface . 7 About this book . 7 Audience. 7 Organization . 7 Suggested reading . 7 Related documentation. 8 General information . 8 Conventions . 8 Terminology conventions . 9 Acronyms and abbreviations. 9 1 Overview . 11 1.1 Application Binary Interface (ABI) . 11 1.2 Assembly language interface . 11 1.3 Simplified mnemonics assembly language interface . 11 2 Application Binary Interface (ABI) . 12 2.1 Instruction and data representation . 12 2.2 Executable and Linking Format (ELF) object files . 12 2.2.1 VLE information section . 13 2.2.2 VLE identification . 14 2.2.3 Relocation types . 15 3 Instruction set . 20 Appendix A Simplified mnemonics for VLE instructions . 22 A.1 Overview . 22 A.2 Subtract simplified mnemonics . 22 A.2.1 Subtract immediate. 22 A.2.2 Subtract . 23 A.3 Rotate and shift simplified mnemonics . 23 A.3.1 Operations on words. 24 A.4 Branch instruction simplified mnemonics . 24 2/50 UM0438 Contents A.4.1 Key facts about simplified branch mnemonics . 26 A.4.2 Eliminating the BO32 and BO16 operands. 26 A.4.3 The BI32 and BI16 operand—CR Bit and field representations . 27 A.4.4 BI32 and BI16 operand instruction encoding . -

Dot / Faa /Ar-11/5

DOT/FAA/AR-11/5 Microprocessor Evaluations for Air Traffic Organization NextGen & Operations Planning Safety-Critical, Real-Time Office of Research and Technology Development Applications: Authority for Washington, DC 20591 Expenditure No. 43 Phase 5 Report May 2011 Final Report This document is available to the U.S. public through the National Technical Information Services (NTIS), Springfield, Virginia 22161. This document is also available from the Federal Aviation Administration William J. Hughes Technical Center at actlibrary.tc.faa.gov. U.S. Department of Transportation Federal Aviation Administration NOTICE This document is disseminated under the sponsorship of the U.S. Department of Transportation in the interest of information exchange. The United States Government assumes no liability for the contents or use thereof. The United States Government does not endorse products or manufacturers. Trade or manufacturer's names appear herein solely because they are considered essential to the objective of this report. The findings and conclusions in this report are those of the author(s) and do not necessarily represent the views of the funding agency. This document does not constitute FAA policy. Consult the FAA sponsoring organization listed on the Technical Documentation page as to its use. This report is available at the Federal Aviation Administration William J. Hughes Technical Center’s Full-Text Technical Reports page: actlibrary.tc.faa.gov in Adobe Acrobat portable document format (PDF). Technical Report Documentation Page 1. Report No. 2. Government Accession No. 3. Recipient's Catalog No. DOT/FAA/AR-11/5 4. Title and Subtitle 5. Report Date MICROPROCESSOR EVALUATIONS FOR SAFETY-CRITICAL, REAL-TIME May 2011 APPLICATIONS: AUTHORITY FOR EXPENDITURE NO. -

DSP56303 Product Brief, Rev

Freescale Semiconductor DSP56303PB Product Brief Rev. 2, 2/2005 DSP56303 24-Bit Digital Signal Processor 16 6 6 3 Memory Expansion Area The DSP56303 is intended Triple X Data HI08 ESSI SCI PrograM Y Data for use in telecommunication Timer RAM RAM RAM 4096 × 24 2048 × 24 2048 × 24 applications, such as multi- bits bits bits line voice/data/ fax (default) (default) (default) processing, video Peripheral Expansion Area conferencing, audio PM_EB XM_EB PIO_EB YAB YM_EB applications, control, and Address External 18 Generation XAB Address general digital signal Unit PAB Bus Address Six-Channel DAB Switch processing. DMA Unit External 24-Bit Bus 13 Bootstrap DSP56300 Interface ROM and Inst. Core Cache Control Control DDB 24 Internal YDB External Data XDB Data Bus Bus PDB Switch Data Switch GDB EXTAL Power Clock Management Data ALU 5 Generator Program Program Program × + → XTAL Interrupt Decode Address 24 24 56 56-bit MAC JTAG PLL Two 56-bit Accumulators Controller Controller Generator 56-bit Barrel Shifter OnCE™ DE 2 MODA/IRQA MODB/IRQB RESET MODC/IRQC PINIT/NMI MODD/IRQD Figure 1. DSP56303 Block Diagram The DSP56303 is a member of the DSP56300 core family of programmable CMOS DSPs. Significant architectural features of the DSP56300 core family include a barrel shifter, 24-bit addressing, instruction cache, and DMA. The DSP56303 offers 100 million multiply-accumulates per second (MMACS) using an internal 100 MHz clock at 3.0–3.6 volts. The DSP56300 core family offers a rich instruction set and low power dissipation, as well as increasing levels of speed and power to enable wireless, telecommunications, and multimedia products. -

Low Power Asynchronous Digital Signal Processing

LOW POWER ASYNCHRONOUS DIGITAL SIGNAL PROCESSING A thesis submitted to the University of Manchester for the degree of Doctor of Philosophy in the Faculty of Science & Engineering October 2000 Michael John George Lewis Department of Computer Science 1 Contents Chapter 1: Introduction ....................................................................................14 Digital Signal Processing ...............................................................................15 Evolution of digital signal processors ....................................................17 Architectural features of modern DSPs .........................................................19 High performance multiplier circuits .....................................................20 Memory architecture ..............................................................................21 Data address generation .........................................................................21 Loop management ..................................................................................23 Numerical precision, overflows and rounding .......................................24 Architecture of the GSM Mobile Phone System ...........................................25 Channel equalization ..............................................................................28 Error correction and Viterbi decoding ...................................................29 Speech transcoding ................................................................................31 Half-rate and enhanced -

Rlsc & DSP Advanced Microprocessor System Design

Purdue University Purdue e-Pubs ECE Technical Reports Electrical and Computer Engineering 3-1-1992 RlSC & DSP Advanced Microprocessor System Design; Sample Projects, Fall 1991 John E. Fredine Purdue University, School of Electrical Engineering Dennis L. Goeckel Purdue University, School of Electrical Engineering David G. Meyer Purdue University, School of Electrical Engineering Stuart E. Sailer Purdue University, School of Electrical Engineering Glenn E. Schmottlach Purdue University, School of Electrical Engineering Follow this and additional works at: http://docs.lib.purdue.edu/ecetr Fredine, John E.; Goeckel, Dennis L.; Meyer, David G.; Sailer, Stuart E.; and Schmottlach, Glenn E., "RlSC & DSP Advanced Microprocessor System Design; Sample Projects, Fall 1991" (1992). ECE Technical Reports. Paper 302. http://docs.lib.purdue.edu/ecetr/302 This document has been made available through Purdue e-Pubs, a service of the Purdue University Libraries. Please contact [email protected] for additional information. RISC & DSP Advanced Microprocessor System Design Sample Projects, Fall 1991 John E. Fredine Dennis L. Goeckel David G. Meyer Stuart E. Sailer Glenn E. Schmottlach TR-EE 92- 11 March 1992 School of Electrical Engineering Purdue University West Lafayette, Indiana 47907 RlSC & DSP Advanced Microprocessor System Design Sample Projects, Fall 1991 John E. Fredine Dennis L. Goeckel David G. Meyer Stuart E. Sailer Glenn E. Schrnottlach School of Electrical Engineering Purdue University West Lafayette, Indiana 47907 Table of Contents Abstract ................................................................................................................... -

Embedded Computing Product Guide Our Customers Operate in Many Diverse Markets

Embedded Computing for Business-Critical Continuity™ Embedded Computing Product Guide Our customers operate in many diverse markets. What unites them is a need to work with a company that has an outstanding record as a reliable supplier. That’s Emerson Network Power. That’s the critical difference. The Embedded Computing business of Emerson Network Power enables original equipment manufacturers and systems integrators to develop better products quickly, cost effectively and with less risk. Emerson is a recognized leading provider of embedded computing solutions ranging from application-ready platforms, embedded PCs, enclosures, motherboards, blades and modules to enabling software and professional services. For nearly 30 years, we have led the ecosystem required to enable new technologies to succeed including defining open specifications and driving industry-wide interoperability. This makes your integration process straightforward and allows you to quickly and easily build systems that meet your application needs. Emerson’s engineering and technical support is backed by world-class manufacturing that can significantly reduce Table of Contents your time-to-market and help you gain a clear competitive edge. And, as part of Emerson, the Embedded Computing 4 AdvancedTCA Products business has strong financial credentials. 9 Commercial ATCA Products Let Emerson help you improve time-to-market and shift 10 Motherboard & COM Products your development efforts to the deployment of new, 14 RapiDex™ Board Customization value-add features and services that create competitive 15 OpenVPX Products advantage and build market share. With Emerson behind you, anything is possible. 16 VME Products 18 CompactPCI Products 20 Solution Services 21 Innovation Partnership Program 22 Terms & Conditions 2 Our leadership and heritage includes embedded computing solutions for military, aerospace, government, medical, automation, industrial and telecommunications applications. -

Introduction to Digital Signal Processors

INTRODUCTION TO Accumulator architecture DIGITAL SIGNAL PROCESSORS Memory-register architecture Prof. Brian L. Evans in collaboration with Niranjan Damera-Venkata and Magesh Valliappan Load-store architecture Embedded Signal Processing Laboratory The University of Texas at Austin Austin, TX 78712-1084 http://anchovy.ece.utexas.edu/ Outline n Signal processing applications n Conventional DSP architecture n Pipelining in DSP processors n RISC vs. DSP processor architectures n TI TMS320C6x VLIW DSP architecture n Signal and image processing applications n Signal processing on general-purpose processors n Conclusion 2 Signal Processing Applications n Low-cost embedded systems 4 Modems, cellular telephones, disk drives, printers n High-throughput applications 4 Halftoning, radar, high-resolution sonar, tomography n PC based multimedia 4 Compression/decompression of audio, graphics, video n Embedded processor requirements 4 Inexpensive with small area and volume 4 Deterministic interrupt service routine latency 4 Low power: ~50 mW (TMS320C5402/20: 0.32 mA/MIP) 3 Conventional DSP Architecture n High data throughput 4 Harvard architecture n Separate data memory/bus and program memory/bus n Three reads and one or two writes per instruction cycle 4 Short deterministic interrupt service routine latency 4 Multiply-accumulate (MAC) in a single instruction cycle 4 Special addressing modes supported in hardware n Modulo addressing for circular buffers (e.g. FIR filters) n Bit-reversed addressing (e.g. fast Fourier transforms) 4Instructions to keep the -

AFE#43 Phase 2 Report

DOT/FAA/AR-08/14 Microprocessor Evaluations for Air Traffic Organization Safety-Critical, Real-Time Operations Planning Office of Aviation Research and Development Applications: Authority for Washington, DC 20591 Expenditure No. 43 Phase 2 Report June 2008 Final Report This document is available to the U.S. public through the National Technical Information Service (NTIS), Springfield, Virginia 22161. U.S. Department of Transportation Federal Aviation Administration NOTICE This document is disseminated under the sponsorship of the U.S. Department of Transportation in the interest of information exchange. The United States Government assumes no liability for the contents or use thereof. The United States Government does not endorse products or manufacturers. Trade or manufacturer's names appear herein solely because they are considered essential to the objective of this report. This document does not constitute FAA certification policy. Consult your local FAA aircraft certification office as to its use. This report is available at the Federal Aviation Administration William J. Hughes Technical Center’s Full-Text Technical Reports page: actlibrary.tc.faa.gov in Adobe Acrobat portable document format (PDF). Technical Report Documentation Page 1. Report No. 2. Government Accession No. 3. Recipient's Catalog No. DOT/FAA/AR-08/14 4. Title and Subtitle 5. Report Date MICROPROCESSOR EVALUATIONS FOR SAFETY-CRITICAL, REAL-TIME June 2008 APPLICATIONS: AUTHORITY FOR EXPENDITURE NO. 43 PHASE 2 REPORT 6. Performing Organization Code 7. Author(s) 8. Performing Organization Report No. Rabi N. Mahapatra, Praveen Bhojwani, and Jason Lee TAMU-CS-AVSI-72005 9. Performing Organization Name and Address 10. Work Unit No. (TRAIS) Aerospace Vehicle Systems Institute Texas Engineering Experiment Station Texas A&M University Department of Computer Science 11. -

Release History

Release History TRACE32 Online Help TRACE32 Directory TRACE32 Index TRACE32 Technical Support ........................................................................................................... Release History ............................................................................................................................. 1 General Information ................................................................................................................... 4 Code 4 Release Information ................................................................................................................... 4 Software Release from 01-Feb-2021 5 Build 130863 5 Software Release from 01-Sep-2020 8 Build 125398 8 Software Release from 01-Feb-2020 11 Build 117056 11 Software Release from 01-Sep-2019 13 Build 112182 13 Software Release from 01-Feb-2019 16 Build 105499 16 Software Release from 01-Sep-2018 19 Build 100486 19 Software Release from 01-Feb-2018 24 Build 93173 24 Software Release from 01-Sep-2017 27 Build 88288 27 Software Release from 01-Feb-2017 32 Build 81148 32 Build 80996 33 Software Release from 01-Sep-2016 36 Build 76594 36 Software Release from 01-Feb-2016 39 Build 69655 39 Software Release from 01-Sep-2015 42 Build 65657 42 Software Release from 02-Feb-2015 45 Build 60219 45 Software Release from 01-Sep-2014 48 Build 56057 48 Software Release from 16-Feb-2014 51 ©1989-2021 Lauterbach GmbH Release History 1 Build 51144 51 Software Release from 16-Aug-2013 54 Build 50104 54 Software Release from 16-Feb-2013 56 -

Variable-Length Encoding (VLE) Extension Programming Interface Manual

Variable-Length Encoding (VLE) Extension Programming Interface Manual VLEPIM Rev. 1, 2/2006 How to Reach Us: Home Page: www.freescale.com email: [email protected] USA/Europe or Locations Not Listed: Freescale Semiconductor Technical Information Center, CH370 1300 N. Alma School Road Chandler, Arizona 85224 (800) 521-6274 480-768-2130 [email protected] Europe, Middle East, and Africa: Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) Information in this document is provided solely to enable system and software +49 89 92103 559 (German) implementers to use Freescale Semiconductor products. There are no express or +33 1 69 35 48 48 (French) implied copyright licenses granted hereunder to design or fabricate any integrated [email protected] circuits or integrated circuits based on the information in this document. Japan: Freescale Semiconductor reserves the right to make changes without further notice to Freescale Semiconductor Japan Ltd. Headquarters any products herein. Freescale Semiconductor makes no warranty, representation or ARCO Tower 15F guarantee regarding the suitability of its products for any particular purpose, nor does 1-8-1, Shimo-Meguro, Meguro-ku Freescale Semiconductor assume any liability arising out of the application or use of Tokyo 153-0064, Japan 0120 191014 any product or circuit, and specifically disclaims any and all liability, including without +81 3 5437 9125 limitation consequential or incidental damages. “Typical” parameters which may be [email protected] provided in Freescale Semiconductor data sheets and/or specifications can and do Asia/Pacific: vary in different applications and actual performance may vary over time. -

CMU DSP the Carnegie Mellon Synthesizable Digital Signal Processor Core

CMU DSP The Carnegie Mellon Synthesizable Digital Signal Processor Core Alpha Version Documentation 1.12 1999/06/10 Chris Inacio The CMU DSP Team [email protected] June 10, 1999 CONTENTS CONTENTS Contents 1 Introduction 3 1.1 Getting and Installing the Distribution . ................ 4 2 Architecture 5 2.1Overview................................ 5 2.2ArithmeticandDataLogicUnit.................... 6 2.3AddressGenerationUnit........................ 6 2.4OtherUnits............................... 7 2.4.1 Bus Switch ........................... 7 2.4.2 ProgramControlUnit..................... 7 2.5MemoryandExternalInterface..................... 7 3 File Repository 9 3.1 Availability ............................... 9 3.2VerilogSourceFiles........................... 9 3.3Documentation............................. 10 3.4TestScriptsandFiles.......................... 11 3.5MiscellaneousFiles........................... 11 4 Scripts and Tools 13 4.1 Introduction ............................... 13 4.2 Verilog PreProcessor ..................... 13 4.3 reformat ............................... 14 4.4 coff_text_dump .......................... 14 4.5 run-test ............................... 14 4.6 cp2build ............................... 16 4.7BuildingtheTools............................ 16 5 CMU DSP Testing 17 5.1 Introduction ............................... 17 5.2 Writing a new functional test . ................ 17 5.2.1 Overview............................ 17 5.2.2 Writing a new program . ................ 18 5.2.3 Motorola Simulation Traces . ............... -

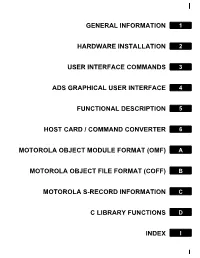

(DSP) Application Development System (ADS) User's Manual

GENERAL INFORMATION 1 HARDWARE INSTALLATION 2 USER INTERFACE COMMANDS 3 ADS GRAPHICAL USER INTERFACE 4 FUNCTIONAL DESCRIPTION 5 HOST CARD / COMMAND CONVERTER 6 MOTOROLA OBJECT MODULE FORMAT (OMF) A MOTOROLA OBJECT FILE FORMAT (COFF) B MOTOROLA S-RECORD INFORMATION C C LIBRARY FUNCTIONS D INDEX I 1 GENERAL INFORMATION 2 HARDWARE INSTALLATION 3 USER INTERFACE COMMANDS 4 ADS GRAPHICAL USER INTERFACE 5 FUNCTIONAL DESCRIPTION 6 HOST CARD / COMMAND CONVERTER A MOTOROLA OBJECT MODULE FORMAT (OMF) B MOTOROLA OBJECT FILE FORMAT (COFF) C MOTOROLA S-RECORD INFORMATION D C LIBRARY FUNCTIONS I INDEX DIGITAL SIGNAL PROCESSOR (DSP) Application Development System (ADS) User’s Manual PRELIMINARY Motorola, Incorporated Semiconductor Products Sector Wireless Signal Processing Division 6501 William Cannon Drive West Austin, TX 78735-8598 This document (and other documents) can be viewed on the World Wide Web at http://www.motorola-dsp.com. OnCE is a trademark of Motorola, Inc. MOTOROLA INC., 1989, 1997 Order this document by DSPADSUM/AD Motorola reserves the right to make changes without further notice to any products herein to improve reliability, function, or design. Motorola does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others. Motorola products are not authorized for use as components in life support devices or systems intendedPRELIMINARY for surgical implant into the body or intended to support or sustain life. Buyer agrees to notify Motorola of any such intended end use whereupon Motorola shall determine availability and suitability of its product or products for the use intended.