Rlsc & DSP Advanced Microprocessor System Design

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Pwny Documentation Release 0.9.0

pwny Documentation Release 0.9.0 Author Nov 19, 2017 Contents 1 pwny package 3 2 pwnypack package 5 2.1 asm – (Dis)assembler..........................................5 2.2 bytecode – Python bytecode manipulation..............................7 2.3 codec – Data transformation...................................... 11 2.4 elf – ELF file parsing.......................................... 16 2.5 flow – Communication......................................... 36 2.6 fmtstring – Format strings...................................... 41 2.7 marshal – Python marshal loader................................... 42 2.8 oracle – Padding oracle attacks.................................... 43 2.9 packing – Data (un)packing...................................... 44 2.10 php – PHP related functions....................................... 46 2.11 pickle – Pickle tools.......................................... 47 2.12 py_internals – Python internals.................................. 49 2.13 rop – ROP gadgets........................................... 50 2.14 shellcode – Shellcode generator................................... 50 2.15 target – Target definition....................................... 79 2.16 util – Utility functions......................................... 80 3 Indices and tables 83 Python Module Index 85 i ii pwny Documentation, Release 0.9.0 pwnypack is the official CTF toolkit of Certified Edible Dinosaurs. It aims to provide a set of command line utilities and a python library that are useful when playing hacking CTFs. The core functionality of pwnypack -

DSP56303 Product Brief, Rev

Freescale Semiconductor DSP56303PB Product Brief Rev. 2, 2/2005 DSP56303 24-Bit Digital Signal Processor 16 6 6 3 Memory Expansion Area The DSP56303 is intended Triple X Data HI08 ESSI SCI PrograM Y Data for use in telecommunication Timer RAM RAM RAM 4096 × 24 2048 × 24 2048 × 24 applications, such as multi- bits bits bits line voice/data/ fax (default) (default) (default) processing, video Peripheral Expansion Area conferencing, audio PM_EB XM_EB PIO_EB YAB YM_EB applications, control, and Address External 18 Generation XAB Address general digital signal Unit PAB Bus Address Six-Channel DAB Switch processing. DMA Unit External 24-Bit Bus 13 Bootstrap DSP56300 Interface ROM and Inst. Core Cache Control Control DDB 24 Internal YDB External Data XDB Data Bus Bus PDB Switch Data Switch GDB EXTAL Power Clock Management Data ALU 5 Generator Program Program Program × + → XTAL Interrupt Decode Address 24 24 56 56-bit MAC JTAG PLL Two 56-bit Accumulators Controller Controller Generator 56-bit Barrel Shifter OnCE™ DE 2 MODA/IRQA MODB/IRQB RESET MODC/IRQC PINIT/NMI MODD/IRQD Figure 1. DSP56303 Block Diagram The DSP56303 is a member of the DSP56300 core family of programmable CMOS DSPs. Significant architectural features of the DSP56300 core family include a barrel shifter, 24-bit addressing, instruction cache, and DMA. The DSP56303 offers 100 million multiply-accumulates per second (MMACS) using an internal 100 MHz clock at 3.0–3.6 volts. The DSP56300 core family offers a rich instruction set and low power dissipation, as well as increasing levels of speed and power to enable wireless, telecommunications, and multimedia products. -

Low Power Asynchronous Digital Signal Processing

LOW POWER ASYNCHRONOUS DIGITAL SIGNAL PROCESSING A thesis submitted to the University of Manchester for the degree of Doctor of Philosophy in the Faculty of Science & Engineering October 2000 Michael John George Lewis Department of Computer Science 1 Contents Chapter 1: Introduction ....................................................................................14 Digital Signal Processing ...............................................................................15 Evolution of digital signal processors ....................................................17 Architectural features of modern DSPs .........................................................19 High performance multiplier circuits .....................................................20 Memory architecture ..............................................................................21 Data address generation .........................................................................21 Loop management ..................................................................................23 Numerical precision, overflows and rounding .......................................24 Architecture of the GSM Mobile Phone System ...........................................25 Channel equalization ..............................................................................28 Error correction and Viterbi decoding ...................................................29 Speech transcoding ................................................................................31 Half-rate and enhanced -

Operating RISC: UNIX Standards in the 1990S

Operating RISC: UNIX Standards in the 1990s This case was written by Will Mitchell and Paul Kritikos at the University of Michigan. The case is based on public sources. Some figures are based on case-writers' estimates. We appreciate comments from David Girouard, Robert E. Thomas and Michael Wolff. The note "Product Standards and Competitive Advantage" (Mitchell 1992) supplements this case. The latest International Computerquest Corporation analysis of the market for UNIX- based computers landed on three desks on the same morning. Noel Sharp, founder, chief executive officer, chief engineer and chief bottle washer for the Superbly Quick Architecture Workstation Company (SQAWC) in Mountain View, California hoped to see strong growth predicted for the market for systems designed to help architects improve their designs. In New York, Bo Thomas, senior strategist for the UNIX systems division of A Big Computer Company (ABCC), hoped that general commercial markets for UNIX-based computer systems would show strong growth, but feared that the company's traditional mainframe and mini-computer sales would suffer as a result. Airborne in the middle of the Atlantic, Jean-Helmut Morini-Stokes, senior engineer for the UNIX division of European Electronic National Industry (EENI), immediately looked to see if European companies would finally have an impact on the American market for UNIX-based systems. After looking for analysis concerning their own companies, all three managers checked the outlook for the alliances competing to establish a UNIX operating system standard. Although their companies were alike only in being fictional, the three managers faced the same product standards issues. How could they hasten the adoption of a UNIX standard? The market simply would not grow until computer buyers and application software developers could count on operating system stability. -

Introduction to Digital Signal Processors

INTRODUCTION TO Accumulator architecture DIGITAL SIGNAL PROCESSORS Memory-register architecture Prof. Brian L. Evans in collaboration with Niranjan Damera-Venkata and Magesh Valliappan Load-store architecture Embedded Signal Processing Laboratory The University of Texas at Austin Austin, TX 78712-1084 http://anchovy.ece.utexas.edu/ Outline n Signal processing applications n Conventional DSP architecture n Pipelining in DSP processors n RISC vs. DSP processor architectures n TI TMS320C6x VLIW DSP architecture n Signal and image processing applications n Signal processing on general-purpose processors n Conclusion 2 Signal Processing Applications n Low-cost embedded systems 4 Modems, cellular telephones, disk drives, printers n High-throughput applications 4 Halftoning, radar, high-resolution sonar, tomography n PC based multimedia 4 Compression/decompression of audio, graphics, video n Embedded processor requirements 4 Inexpensive with small area and volume 4 Deterministic interrupt service routine latency 4 Low power: ~50 mW (TMS320C5402/20: 0.32 mA/MIP) 3 Conventional DSP Architecture n High data throughput 4 Harvard architecture n Separate data memory/bus and program memory/bus n Three reads and one or two writes per instruction cycle 4 Short deterministic interrupt service routine latency 4 Multiply-accumulate (MAC) in a single instruction cycle 4 Special addressing modes supported in hardware n Modulo addressing for circular buffers (e.g. FIR filters) n Bit-reversed addressing (e.g. fast Fourier transforms) 4Instructions to keep the -

1990 Motorola Annual Report

Annual Report 1990 (M) MOTOROLA INC. >\ About the Company Motorola is one of the world's leading providers of electronic equipment, systems, components and services for worldwide markets. Products include two-way radios, pagers, cellular telephones and systems, semiconductors, defense and aerospace electronics, automotive and industrial electronics, computers, data communications and informa- tion processing and handling equipment. Motorola was a winner of the first Malcolm Baldrige National Quality Award, in recognition of its superior company-wide management of quality processes. On the Cover One of the newest landmarks in Paris is architect I.M. Pei's pyramid entrance to the Louvre. Guards from Erom Se'curite' S.A. use Motorola two-way communications equipment at the museum to protect some of the finest art treasures in the world. In this year's report you will see how Motorola products and sys- tems serve our customers throughout the world. Contents Financial Highlights 2 To Our Stockholders and Other Friends 3 At a Glance 16 Review of Operations 19 Financial Review 24 Financial Statements 27 Notes to Consolidated Financial Statements 30 Five Year Financial Summary 36 Sectors, Groups and Divisions, Motorola Worldwide 37 Elected Officers 38 Directors, CEO Quality Awards, Dan Noble Fellows 40 Stockholder Reference Information 41 n each of our chosen arenas of the electronics industry, we plan to grow rapidly by providing our worldwide customers what they want, when they want it, with Six Sigma quality and best-in-class cycle time, as we strive to achieve our fundamental corporate objective of Total Customer Satisfaction, and to achieve our stated goals of increased global market share, best-in-class people, products, marketing, manufacturing, technology and service, and superior financial results. -

SCALP: a Superscalar Asynchronous Low-Power Processor Philip Brian

SCALP: A Superscalar Asynchronous Low-Power Processor A thesis submitted to the University of Manchester for the degree of Doctor of Philosophy in the Faculty of Science and Engineering Philip Brian Endecott Department of Computer Science 1996 Contents Contents . 2 List of Figures. 6 List of Tables . 8 Abstract. 10 Declaration . 12 Copyright and Intellectual Property Rights . 12 Acknowledgements. 13 The Author . 13 Chapter 1: SCALP: A Superscalar Asynchronous Low-Power Processor. 14 1.1 The Importance of Power Efficiency . 15 1.2 Low Power Design Techniques . 16 1.2.1 Low-Level Power Efficiency . 16 Process Technology. 16 Transistor Level Design . 17 Charge Recovery and Adiabatic Systems . 17 Logic Optimisation . 18 Supply Voltage Adjustment . 18 Parallelism. 19 Precomputation . 19 Clocking Schemes and Asynchronous Logic . 19 1.2.2 Higher-Level Power Efficiency: Microprocessors . 20 External Memory Bandwidth . 20 Cache Characteristics . 20 Datapath Arrangement . 21 1.3 Previous Low Power Processors. 21 1.4 Overview of the Thesis. 22 Chapter 2: Reducing Transitions . 24 2.1 Code Density . 24 2.1.1 Variable Length Instructions . 27 2.1.2 Register Specifiers . 29 2.1.3 Previous High Code Density Processors . 31 D16 . 31 Thumb . 32 Transputer . 32 2.2 Datapath Activity . 33 Chapter 3: Parallelism . 35 3.1 Parallelism and Power . 35 3.2 Power, Parallelism and Cost . 37 3.3 Parallelism in Special Purpose Processors . 38 3.4 Parallelism in General Purpose Processors. 39 3.5 Pipelining . 40 3.5.1 Branch Instructions. 43 3.5.2 Dependencies . 45 3.5.3 Different Pipeline Arrangements . 48 - 2 - Shorter Pipelines . -

The DENX U-Boot and Linux Guide (DULG) for Canyonlands

The DENX U-Boot and Linux Guide (DULG) for canyonlands Table of contents: • 1. Abstract • 2. Introduction ♦ 2.1. Copyright ♦ 2.2. Disclaimer ♦ 2.3. Availability ♦ 2.4. Credits ♦ 2.5. Translations ♦ 2.6. Feedback ♦ 2.7. Conventions • 3. Embedded Linux Development Kit ♦ 3.1. ELDK Availability ♦ 3.2. ELDK Getting Help ♦ 3.3. Supported Host Systems ♦ 3.4. Supported Target Architectures ♦ 3.5. Installation ◊ 3.5.1. Product Packaging ◊ 3.5.2. Downloading the ELDK ◊ 3.5.3. Initial Installation ◊ 3.5.4. Installation and Removal of Individual Packages ◊ 3.5.5. Removal of the Entire Installation ♦ 3.6. Working with ELDK ◊ 3.6.1. Switching Between Multiple Installations ♦ 3.7. Mounting Target Components via NFS ♦ 3.8. Rebuilding ELDK Components ◊ 3.8.1. ELDK Source Distribution ◊ 3.8.2. Rebuilding Target Packages ◊ 3.8.3. Rebuilding ELDT Packages ♦ 3.9. ELDK Packages ◊ 3.9.1. List of ELDT Packages ◊ 3.9.2. List of Target Packages ♦ 3.10. Rebuilding the ELDK from Scratch ◊ 3.10.1. ELDK Build Process Overview ◊ 3.10.2. Setting Up ELDK Build Environment ◊ 3.10.3. build.sh Usage ◊ 3.10.4. Format of the cpkgs.lst and tpkgs.lst Files ♦ 3.11. Notes for Solaris 2.x Host Environment • 4. System Setup ♦ 4.1. Serial Console Access ♦ 4.2. Configuring the "cu" command ♦ 4.3. Configuring the "kermit" command ♦ 4.4. Using the "minicom" program ♦ 4.5. Permission Denied Problems ♦ 4.6. Configuration of a TFTP Server ♦ 4.7. Configuration of a BOOTP / DHCP Server ♦ 4.8. Configuring a NFS Server • 5. -

Ronics APRIL 28, 1988

DATA GENERAL'S 88000 RISC CHIPS WILL HIT 100 MIPS/32 SMART-POWER IC SET ALL BUT ELIMINATES CIRCUIT DESIGN/93 A VNU PUBLICATION t• APRIL 28, 1988 ronics A CLOSE LOOK AT MOTOROLA'S 88000/75 CHOOSING A RISC CHIP: WHAT DRIVES CUSTOMERS?/85 This year,you'll hear alot of claims that "systems"design automation has arrived. database and user interface? This 32-bit Does it extend from design processor board At Mentor Grapimics/ definition through to was designed and PCB simulated on layout and output to manufacturing? Mentor Graphics we know better workstations by • Do you have more ASIC libraries Sequent Com- supported on your workstation than puter Systems for And so do our any other EDA vendor? Can you its multi-pro- cessor Symmetry include ASICs in board simulations? computer system. It contains over customers. Are your tools capable of manag- 175 IC compo- ing over 1000-page product docu- nents including They preach. We practice. 80386 pro- mentation projects from start to cessors, a14,000- Skeptical about "systems" elec- finish? gate standard cell and two 10,000- tronic design automation? Have you integrated mechanical gate arrays. You should be. Because in many packaging and analysis into the elec- cases, it's atriumph of form over tronic design and layout process? reason. Over 70% are repeat cus- content. In the end, there's only one Anything less than aperfect score tomers who've realized genuine practical yardstick for evaluating a is atotal loss. And aperfect score value added from our products and systems design solution. And that's does not mean just acheck in every seek to expand their competitive how many successful products it has box. -

CMU DSP the Carnegie Mellon Synthesizable Digital Signal Processor Core

CMU DSP The Carnegie Mellon Synthesizable Digital Signal Processor Core Alpha Version Documentation 1.12 1999/06/10 Chris Inacio The CMU DSP Team [email protected] June 10, 1999 CONTENTS CONTENTS Contents 1 Introduction 3 1.1 Getting and Installing the Distribution . ................ 4 2 Architecture 5 2.1Overview................................ 5 2.2ArithmeticandDataLogicUnit.................... 6 2.3AddressGenerationUnit........................ 6 2.4OtherUnits............................... 7 2.4.1 Bus Switch ........................... 7 2.4.2 ProgramControlUnit..................... 7 2.5MemoryandExternalInterface..................... 7 3 File Repository 9 3.1 Availability ............................... 9 3.2VerilogSourceFiles........................... 9 3.3Documentation............................. 10 3.4TestScriptsandFiles.......................... 11 3.5MiscellaneousFiles........................... 11 4 Scripts and Tools 13 4.1 Introduction ............................... 13 4.2 Verilog PreProcessor ..................... 13 4.3 reformat ............................... 14 4.4 coff_text_dump .......................... 14 4.5 run-test ............................... 14 4.6 cp2build ............................... 16 4.7BuildingtheTools............................ 16 5 CMU DSP Testing 17 5.1 Introduction ............................... 17 5.2 Writing a new functional test . ................ 17 5.2.1 Overview............................ 17 5.2.2 Writing a new program . ................ 18 5.2.3 Motorola Simulation Traces . ............... -

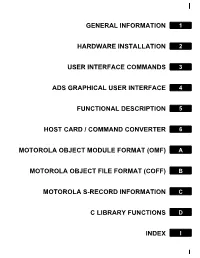

(DSP) Application Development System (ADS) User's Manual

GENERAL INFORMATION 1 HARDWARE INSTALLATION 2 USER INTERFACE COMMANDS 3 ADS GRAPHICAL USER INTERFACE 4 FUNCTIONAL DESCRIPTION 5 HOST CARD / COMMAND CONVERTER 6 MOTOROLA OBJECT MODULE FORMAT (OMF) A MOTOROLA OBJECT FILE FORMAT (COFF) B MOTOROLA S-RECORD INFORMATION C C LIBRARY FUNCTIONS D INDEX I 1 GENERAL INFORMATION 2 HARDWARE INSTALLATION 3 USER INTERFACE COMMANDS 4 ADS GRAPHICAL USER INTERFACE 5 FUNCTIONAL DESCRIPTION 6 HOST CARD / COMMAND CONVERTER A MOTOROLA OBJECT MODULE FORMAT (OMF) B MOTOROLA OBJECT FILE FORMAT (COFF) C MOTOROLA S-RECORD INFORMATION D C LIBRARY FUNCTIONS I INDEX DIGITAL SIGNAL PROCESSOR (DSP) Application Development System (ADS) User’s Manual PRELIMINARY Motorola, Incorporated Semiconductor Products Sector Wireless Signal Processing Division 6501 William Cannon Drive West Austin, TX 78735-8598 This document (and other documents) can be viewed on the World Wide Web at http://www.motorola-dsp.com. OnCE is a trademark of Motorola, Inc. MOTOROLA INC., 1989, 1997 Order this document by DSPADSUM/AD Motorola reserves the right to make changes without further notice to any products herein to improve reliability, function, or design. Motorola does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others. Motorola products are not authorized for use as components in life support devices or systems intendedPRELIMINARY for surgical implant into the body or intended to support or sustain life. Buyer agrees to notify Motorola of any such intended end use whereupon Motorola shall determine availability and suitability of its product or products for the use intended. -

Fixed-Point C Compiler for Tms320c50 Digital Signal Processor

FIXED-POINT C COMPILER FOR TMS320C50 DIGITAL SIGNAL PROCESSOR Jiyang liang Wonyong Sung School of Electrical Engineering Seoul National University, KOREA jiyang@hdtv .snu.ac. kr and wysung@dsp, snu. ac. kr ABSTRACT 2. FIXED-POINT ARITHMETIC RULES A fixed-point C compiler is developed for convenient and ef- An integer variable or a constant in C language consists of, ficient programming of TMS320C50 fixed-point digital sig- usually, 16 bits, and the LSB(Least Significant Bit) has the nal processor. This compiler supports the ‘fix’ data type weight of one for the conversion to or from the floating-point that can have an individual integer word-length according data type. This can bring overflows or unacceptable quanti- to the range of a variable. It can add or subtract two data zation errors when a floating-point digital signal processing having different integer word-lengths by automatically in- program is converted to an integer version. Therefore, it is serting shift operations. The accuracy of fixed-point mul- necessary to assign a different weight to the LSB of a vari- tiply operation is significantly increased by storing the up- able or a constant [7] [8]. For this purpose, we employed per part of the multiplied double-precision result instead of a fixed-point data type that can have an individual integer keeping the lower part as conducted in the integer multipli- word-length as follows: cation. Several target specific code optimization techniques are employed to improve the compiler efficiency. The empir- fix(integer-wordlength) variable-name; ical results show that the execution speed of a fixed-point C program is much, about an order of magnitude, faster than that of a floating-point C program in a fixed-point digital Note that the range (R)that a variable can represent and signal processor.