Electrical Characterization on Signal Transmission of SATA Cable Assembly

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

RS-485: Still the Most Robust Communication Table of Contents

TUTORIAL RS-485: Still the Most Robust Communication Table of Contents Abstract...........................................................................................................................1 RS-485 vs. RS-422..............................................................................................................................2 An In-Depth Look at RS-485...........................................................................................................3 Challenges of the Industrial Environment.....................................................................................5 Protecting Systems from Harsh Environments.........................................................................5 Conclusion......................................................................................................................10 References......................................................................................................................10 Abstract Despite the rise in popularity of wireless networks, wired serial networks continue to provide the most robust, reliable communication, especially in harsh environments. These well-engineered networks provide effective communication in industrial and building automation applications, which require immunity from noise, electrostatic discharge and voltage faults, all resulting in increased uptime. This tutorial reviews the RS-485 protocol and discusses why it is widely used in industrial applications and the common problems it solves. www.maximintegrated.com -

HD3SS214 8.1Gbps Displayport 1.4 2:1/1:2

Product Order Technical Tools & Support & Folder Now Documents Software Community HD3SS214 SLAS907B –DECEMBER 2015–REVISED JUNE 2017 HD3SS214 8.1 Gbps DisplayPort 1.4 2:1/1:2 Differential Switch 1 Features 3 Description HD3SS214 is a high-speed passive switch capable of 1• Compatible with DisplayPort 1.4 Electrical Standard switching two full DisplayPort 4 lane ports from one of two sources to one target location in an application. It • 2:1 and 1:2 Switching Supporting Data Rates up will also switch one source to one of two sinks. For to 8.1 Gbps DisplayPort Applications, the HD3SS214 supports • Supports HPD, AUX and DDC Switching switching of the Auxiliary (AUX), Display Data • Wide Differential BW of 8 GHz Channel (DDC) and Hot Plug Detect (HPD) signals in the ZQE package. • Excellent Dynamic Electrical Characteristics • V Operating Range 3.3 V ±10% One typical application would be a mother board that DD includes two GPUs that need to drive one DisplayPort • Extended Industrial Temperature Range of sink. The GPU is selected by the Dx_SEL pin. -40°C to 105°C Another application is when one source needs to • 5 mm x 5 mm, 50-Ball ųBGA Package switch between one of two sinks, example would be a • Output Enable (OE) Pin Disables Switch to Save side connector and a docking station connector. The Power switching is controlled using the Dx_SEL and AUX_SEL pins. The HD3SS214 operates from a • Power Consumption single supply voltage of 3.3 V over extended – Active < 2 mW Typical industrial temperature range -40°C to 105°C. -

Displayport to TMDS Level Shifting Re-Driver Check for Samples: SN75DP139

SN75DP139 www.ti.com SLLS977D –APRIL 2009–REVISED JULY 2013 DisplayPort to TMDS Level Shifting Re-driver Check for Samples: SN75DP139 1FEATURES • DisplayPort Physical Layer Input Port to TMDS • Enhanced ESD: 10kV on All Pins Physical Layer Output Port • Enhanced Commercial Temperature Range: • Integrated TMDS Level Shifting Re-driver With 0°C to 85°C Receiver Equalization • 48 Pin 7 × 7 QFN (RGZ) Package • Supports Data Rates up to 3.4Gbps • 40 Pin 5 x 5 QFN (RSB) Package • Achieves HDMI 1.4b Compliance • 3D HDMI Support With TMDS Clock Rates up APPLICATIONS to 340MHz • Personal Computer Market • 4k x 2k Operation (30Hz, 24bpp) – DP/TMDS Dongle • Deep Color Supporting 36bpp – Desktop PC • Integrated I2C Logic Block for DVI/HDMI – Notebook PC Connector Recognition – Docking Station 2 • Integrated Active I C Buffer – Standalone Video Card DESCRIPTION The SN75DP139 is a Dual-Mode DisplayPort input to Transition-Minimized Differential Signaling (TMDS) output. The TMDS output has a built in level shifting re-driver supporting Digital Video Interface (DVI) 1.0 and High Definition Multimedia Interface (HDMI) 1.4b standards. The SN75DP139 is specified up to a maximum data rate of 3.4Gbps, supporting resolutions greater then 1920x1200 or HDTV 12 bit color depth at 1080p (progressive scan). SN75DP139 is compliant with the HDMI 1.4b specifications and supports optional protocol enhancements such as 3D graphics at resolutions demanding a pixel rate up to 340MHz. An integrated Active I2C buffer isolates the capacitive loading of the source system from that of the sink and interconnecting cable. This isolation improves overall signal integrity of the system and allows for considerable design margin within the source system for DVI / HDMI compliance testing. -

LVDS Application and Data Handbook

LVDS Application and Data Handbook High-Performance Linear Products Technical Staff Literature Number: SLLD009 November 2002 Printed on Recycled Paper IMPORTANT NOTICE Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment. TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed. TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards. TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third–party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. -

Serial ATA Interface

Serial ATA Interface Frank R. Chu Senior Engineer Hitachi Global Storage Technologies June 2003 Why do we need a new interface? Limitations of parallel ATA Serial ATA was designed to overcome a number of limitations of parallel ATA. The most significant limitation of parallel ATA is the difficulty in increasing the data rate beyond 100MB/s. Parallel ATA uses a single-ended signaling system that is prone to induced noise. Increasing the parallel data rate beyond 100 MB/s would require a new signaling system that would not be backward compatible with existing systems. Desktop HDDs can be expected to outrun the 100 Mbytes/sec data rate in the next few years so a new system is needed. An additional limitation is that parallel ATA uses 5V signaling levels and upcoming silicon microelectronic processes are not compatible with 5V signaling. Serial ATA overcomes these issues by moving to 250mV differential signaling method. Differential signaling rejects induced noise. The 250mV differential signal level is compatible with future microelectronic fabrication processes. Parallel ATA Topology Serial ATA Topology Parallel ATA Topology Serial ATA Topology Operating system Operating System Serial ATA ATA Application 1 Application 1 Standard Adapter adapter Disk Driver Application 2 Driver Application 2 Drive Disk Application 3 Disk Disk Application 3 Drive drive drive Forecasts Indicate ATA Dominance ATA is the dominant HDD interface in the industry. The ATA interface market is expected to be approximately 190 million units in 2003, accounting for about 90% of all HDDs shipped, according to International Data Corporations (IDC) 2002/03 forecasts. By 2006, IDC projects ATA unit shipments will increase to beyond 310 million and continue to account for 90% of all HDDs shipments. -

FUSB1500 — USB2.0 Full-Speed / Low-Speed Transceiver with Charger Detection

FUSB1500 / FUSB1501 — USB2.0 Full-Speed April 2011 FUSB1500 — USB2.0 Full-Speed / Low-Speed Transceiver with Charger Detection Features Description . Complies with USB2.0 Specification The FUSB1500 is a USB2.0 FS/LS transceiver with resistive charger detection. It is compliant with the . Supports 12Mbps and 1.5Mbps USB2.0 Speeds Universal Serial Bus Specification, Rev. 2.0 (USB2.0). - Single Ended (SE) Mode Signaling Ideal for portable electronic devices; such as mobile - Slew-Rate Controlled Differential Data Driver phones, digital still cameras, and personal digital - Differential Input Receiver with Wide Common- assistants; it allows USB Application Specific ICs Mode Range and High Input Sensitivity (ASICs) and Programmable Logic Devices (PLDs) with Low-Speed Transceiver with Charger Detection - Stable RCV Output during SE0 Condition power supply voltages from 1.65V to 3.6V to interface with the physical layer of the Universal Serial Bus. - Two Single-Ended Receivers with Hysteresis The FUSB1500 can be used as a USB device Supports I/O Voltage: 1.65V to 3.6V . transceiver or a USB host transceiver. It can transmit and receive serial data at both full-speed (12Mbps) and Applications low-speed (1.5Mbps) data rates. The FUSB1500 supports the SE Mode controller . Dual-Camera Applications for Cell Phones interface. Dual-LCD Applications for Cell Phones, Digital Camera Displays, and Viewfinders IMPORTANT NOTE: For additional performance information, please contact [email protected]. Ordering Information Operating Top Packing Part Number Temperature Package Mark Method Range FUSB 16-Pin, Molded Leadless Package (MLP), FUSB1500MHX -40 to +85°C Tape and Reel 1500 JEDEC MO217 Equivalent, 3mm Square © 2008 Fairchild Semiconductor Corporation www.fairchildsemi.com FUSB1500 • Rev. -

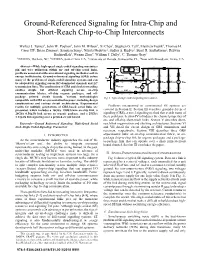

Ground-Referenced Signaling for Intra-Chip and Short-Reach Chip-To-Chip Interconnects

Ground-Referenced Signaling for Intra-Chip and Short-Reach Chip-to-Chip Interconnects Walker J. Turner1, John W. Poulton1, John M. Wilson1, Xi Chen2, Stephen G. Tell1, Matthew Fojtik1, Thomas H. Greer III1, Brian Zimmer2, Sanquan Song2, Nikola Nedovic2, Sudhir S. Kudva2, Sunil R. Sudhakaran2, Rizwan Bashirullah3, Wenxu Zhao4, William J. Dally2, C. Thomas Gray1 1NVIDIA, Durham, NC, 2NVIDIA, Santa Clara, CA, 3University of Florida, Gainesville, FL, 4Now with Broadcom, Irvine, CA Abstract—While high-speed single-ended signaling maximizes VDD pin and wire utilization within on- and off-chip serial links, VREF problems associated with conventional signaling methods result in R R energy inefficiencies. Ground-referenced signaling (GRS) solves DRIVE+ TERM TXDAT LINE many of the problems of single-ended signaling systems and can + RXDAT C CEXT + V be adapted for signaling across RC-dominated channels and LC - INT - DD RDRIVE- + transmission lines. The combination of GRS and clock forwarding VREF - enables simple but efficient signaling across on-chip GND communication fabrics, off-chip organic packages, and off- package printed circuit boards. Various methodologies Fig. 1. Typical single-ended signaling interconnect. compatible with GRS are presented in this paper, including design considerations and various circuit architectures. Experimental results for multiple generations of GRS-based serial links are Problems encountered in conventional SE systems are presented, which includes a 16Gb/s 170fJ/b/mm on-chip link, a covered in Section II. Section III describes ground-referenced 20Gb/s 0.58pJ/b link across an organic package, and a 25Gb/s signaling (GRS), a novel signaling method that avoids many of 1.17pJ/b link signaling over a printed-circuit board. -

LVDS Owner's Manual

LVDS Owner’s Manual Including High-Speed CML and Signal Conditioning High-Speed Interface Technologies Overview 9-13 Network Topology 15-17 SerDes Architectures 19-29 Termination and Translation 31-38 Design and Layout Guidelines 39-45 Jitter Overview 47-58 Interconnect Media and Signal Conditioning 59-75 I/O Models 77-82 Solutions for Design Challenges 83-101 www.ti.com/LVDS 2008 2 LVDS Owner’s Manual Including High-Speed CML and Signal Conditioning Fourth Edition 2008 www.ti.com/LVDS 3 Contents Introduction ..........................................................................7 Design and Layout Guidelines ........................................39 5.1 PCB Transmission Lines ......................................................39 High-Speed Interface Technologies Overview..............9 5.2 Transmission Loss ................................................................40 1.1 Differential Signaling Technology .......................................9 5.3 PCB Vias .................................................................................41 1.2 LVDS – Low-Voltage Differential Signaling .....................10 5.4 Backplane Subsystem .........................................................42 1.3 CML – Current-Mode Logic .................................................11 5.5 Decoupling .............................................................................44 1.4 Low-Voltage Positive-Emitter-Coupled Logic .................12 1.5 Selecting An Optimal Technology .....................................12 Jitter Overview ..................................................................47 -

High-Speed Signal Distribution Using Low-Voltage Differential Signaling (LVDS)

Maxim > Design Support > Technical Documents > Application Notes > Basestations/Wireless Infrastructure > APP 873 Maxim > Design Support > Technical Documents > Application Notes > High-Speed Interconnect > APP 873 Maxim > Design Support > Technical Documents > Application Notes > Interface Circuits > APP 873 Keywords: LVDS, low voltage, differential signaling signalling, lvds, EIA/TIA-644, high speed, clock distribution, communications, stubs, EMI, electro-magnetic immunity, fail-safe, noise immunity, low power APPLICATION NOTE 873 High-Speed Signal Distribution Using Low-Voltage Differential Signaling (LVDS) Dec 11, 2001 Abstract: The ANSI EIA/TIA-644 standard for Low Voltage Differential Signaling (LVDS) is well suited for a variety of applications including clock distribution, point-to-point and point-to-multipoint signal distribution. This note describes methods for distributing high-speed communications signals to different destinations using LVDS signaling. Low-voltage differential signaling (LVDS) is well-suited for a variety of applications, including clock distribution and point-to-multipoint signal distribution. This note describes methods for distributing high- speed signals to different destinations. Clock distribution is of great importance in digital systems where different subsystems are required to work with the same clock reference. For example, the DSP section of a basestation must, in most cases, be synchronized to the radio-frequency signal processing section, which is where phase-locked loops (PLLs) produce the required local oscillator frequencies and where analog-to-digital converters are locked to the central clock reference. Also, when working with applications that include radio receivers, the clock (and the signals) must be distributed with the lowest possible emission levels to avoid interfering with low-level signal paths. -

Comparison of RS-485 Differential-Mode Noise Immunity

Application Report SLLA322–November 2011 Comparison of Differential-Mode Noise Immunity of RS-485 Receivers With 3.3-V Supply Clark Kinnaird ........................................................................................................ Industrial Interface ABSTRACT RS-485 is a widely used standard for industrial communication due to its simplicity and suitability for use in high-noise environments on long cables. Inherent in the standard are balanced signal drivers and receivers, which use differential signaling to reject common-mode noise. Receiver hysteresis is commonly used to ensure glitch-free reception even when differential noise is present. This application report compares the noise immunity of the SN65HVD37 to similar devices available from competitors. Contents 1 Noise Immunity .............................................................................................................. 1 2 Receiver Sensitivity and Hysteresis ...................................................................................... 2 3 The Effect of Cable Attenuation ........................................................................................... 2 4 Test Method for Noise Immunity Comparison ........................................................................... 4 5 Noise Immunity Test Results .............................................................................................. 4 6 Comparison of Results ..................................................................................................... 9 List of -

Differential Signaling Doesn't Require Differential

Article for Printed Circuit Design By Lee W. Ritchey, 3Com Corporation Differential Signaling Doesn’t Require Differential Impedance Or, How to Design a Differential Signaling Circuit That title may seem like a complete contradiction to the “wisdom” written in many design documents describing how to route differential pair signals. It is ---- and that is just what its intent is. Now that your attention has been caught, let’s look at differential signaling. Virtually all design rules in common use require designers to provide a specified differential impedance between pairs of signals involved in differential signaling circuits such as differential ECL or LVDS (Low Voltage Differential Signaling). As a result, much effort is consumed trying to decide on PCB geometries that will provide the desired impedance and an equal amount of effort trying to lay out the traces and build the PCB. On top of this, much time is spent trying to accurately measure the differential impedance. As it turns out, differential impedance doesn’t play a role in this form of signaling and is not necessary. How it was decided to impose this condition on this type of signaling is a mystery. It probably happened because the word differential is in the title. In any case, as will be seen in the following explanation of how this signaling works, other design considerations are more important. First, it is useful to understand the problem that differential signaling was designed to solve. Differential signaling is designed to transmit logic signals between two boxes or units that have logic grounds offset from each other by an amount too large for single ended logic signals to function correctly. -

RS-485/RS-422 Circuit Implementation Guide by Hein Marais

AN-960 APPLICATION NOTE One Technology Way • P. O. Box 9106 • Norwood, MA 02062-9106, U.S.A. • Tel: 781.329.4700 • Fax: 781.461.3113 • www.analog.com RS-485/RS-422 Circuit Implementation Guide by Hein Marais INTRODUCTION WHY USE DIFFERENTIAL DATA TRANSMISSION? Industrial and instrumentation applications (I&I) require The main reason why RS-485 can communicate over long transmission of data between multiple systems often over distances is the use of differential or balanced lines. A com- very long distances. The RS-485 bus standard is one of the munication channel requires a dedicated pair of signal lines most widely used physical layer bus designs in I&I applica- to exchange information. The voltage on one line equals the tions. The key features of RS-485 that make it ideal for use inverse of the voltage on the other line. in I&I communications applications are TIA/EIA-485-A designates the two lines in this differential pair • Long distance links—up to 4000 feet. as A and B. Line A is more positive than Line B (VOA > VOB) on the driver output if a logic high is received on the input of the • Bidirectional communications possible over a single pair of transmitter (DI = 1). If a logic low is received on the input of the twisted cables. transmitter (DI = 0), the transmitter causes Line B to be more • Differential transmission increases noise immunity and positive than Line A (VOB > VOA). See Figure 1. decreases noise emissions. A DI RO • Multiple drivers and receivers can be connected on the VOD V V B V V same bus.