HMP8170 Datasheet

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

KSL-TV--First in the US with Teletext

DOCUMENT RESUME , ED 229 808 CS 504 188 AUTHOR Acker, Stephen R.; Larson, TimothyL. TITLE KSL-TV--First in fir U.S. with Te1etext. , PUB DATE Nov 82 , NOTE 19p.; Paper presented at the AnnualMeeting/ . of the . Speech Communication Association (68th,'Louipille, A KY, November 4=7, t9821t. PUB TYPE Rep9rts - Evaluative/Feasibility (142) Speeches/Conference Papers (150) EDRS PRICE MF01/PC01 Plus Postage. DESCRIPTOkS *Information Services; *Telephone Coimiunications/ Systems; *Television; Video Equipme; ;,*Videotex IDENTIFIERS *Station Kgr.. TV UT; *Two Way Televi ion ABSTRACT Under an experimental license issu din 1978, KSL-TV in Salt Lake City, Utah, provided 126pages of tel text information to its viewers. In choosing thissystem, the stati n had to decide between it and a videotext system. Althoughvideotext systems permit two-way communication, usuallyover telephone UT, teletext broadcast technology is much cheaper.The Cost fo a decoder, a critical factor in the consumer's'accoptance of e ther system, is ,expected to decline for both technologies.In tel text, access cost is zero, while in videotext theinformation provi er has the option of charging users. It'is possiblethat videotext' interactive capability and superior graphics willincrease rt penetration into paying households. Although teletextand videotext provide similar mass market services, videotext has substantiallymore flexibility and speed. Since systems currently beingused in different countries are incompatible, establishing,technical standards inthe areas of data format, transmission,a d display is of key importance. Current trends and the growing home co1iptermarket favor the growth of videotext, but KSL-TV's experiment howed the value of teletextas an interim information system. -

TVP5150AM1 VBI Quick Start

Application Report SLEA102–July 2010 TVP5150AM1 VBI Quick Start ..................................................................................................................................................... ABSTRACT The TVP5150AM1 video decoder has an internal vertical data processor (VDP) that can be used to slice various VBI data services such as V-Chip, Teletext (WST, NABTS), closed captioning (CC), wide screen signaling (WSS), copy generation management system (CGMS), video program system (VPS), electronic program guide (EPG or Gemstar), program delivery control (PDC) and vertical interval time code (VITC). This application report provides an introduction to the VBI data slicing capabilities of the TVP5150AM1 and focuses on configuring the TVP5150AM1 for the more commonly used VBI data services. Contents 1 Introduction .................................................................................................................. 2 2 VDP Configuration RAM ................................................................................................... 4 3 Line Mode Registers ........................................................................................................ 6 4 Sliced Data Retrieval ....................................................................................................... 7 5 Managing Data Retrieval ................................................................................................... 7 6 FIFO Access ................................................................................................................ -

VIDEOTEX ALTERNATIVES in CABLE Walter S. Ciciora William L

VIDEOTEX ALTERNATIVES IN CABLE Walter s. Ciciora William L. Thomas AMERICAN TELEVISION & COMMUNICATIONS CORPORATION ZENITH RADIO CORPORATION Introduction without increasing bandwidth. VBI teletext services are available on any The first videotex alternative systems that carry WTBS, NBC or CBS. determines whether the transmission is Both NBC and CBS are currently broad broadcast, telephone, or cable. The casting teletext according to the North concentration here is on cable. The American Broadcast Teletext Specifi reasons for this will be discussed in cation (NABTS). WTBS carries the Keyfax detail since they are fundamental to signal which follows the British understanding cable's substantial advan approach. Unfortunately, two different tages over competing media. In cable decoders would be required to receive there are a wide variety of alternatives all three signals. Full field teletext to consider. Should the videotex ser requires the dedication of a complete vice be vertical blanking interval or video channel to the teletext service. full field? Will financial support come In return for this commitment, full from advertising or from pay, or both? field teletext offers tremendous page If a pay structure is chosen will the capacity. Typical systems can carry 500 security be soft, firm or hard? Will or more pages per second. This is in the service be tiered and addressable or contrast to the 4 or 5 pages per second simply go no-go? Will it be one-way, possible in a VBI service. Thus, for a one-way upgradable, or two-way? Will given 10-second maximum wait time, full the display be RF or RGB? Are mosaic field teletext has a capacity of 5,000 graphics adequate, or must geometric pages. -

Videotex/Teletext Presentation Level Protocol Syntax (North American PIPS) I

American Canadian National Adopted for Use by the Federal Government REFERENCE | NBS PUBLICATIONS r i(/. f 1 1 wS\3 No.121 1986 | North American PLPS i Government use. pederai d has been adopted l°'Fe " , Government are c0™e„,ation Level This standard within ,hc Federal ^^eUrie*■*.ca,ions available concerning 'ts . ds Publication . list the P . Processing Deta''S °n Processing Standards for a cornet the Standards Qf SSSCU-*- American <C !ri b Canadian National CL'UCX IJ A- Standards Standard Association .110-1983 T500-1983 NBS RESEARCH INFORMATION Videotex/Teletext CENTER Presentation Level Protocol Syntax North American PLPS Published in December, 1983 by American National Standards Institute, Inc. Canadian Standards Association 1430 Broadway 178 Rexdale Boulevard New York, NY 10018 Rexdale (Toronto), Ontario M9W 1R3 (Approved November 3, 1983) (Approved October 3, 1983) American National Standards and Canadian Standards Standards approved by the American National Standards Institute (ANSI) and the Canadian Standards Association (CSA) imply a consensus of those substantially concerned with their scope and provisions. These standards are intended as guides to aid the manufacturer, the consumer, and the general public. The existence of a standard does not in any respect preclude any of the above groups, whether they have approved the standard or not, from manufacturing, marketing, purchasing, or using products, processes, or procedures not conforming to the standard. These standards are subject to periodic review and users are cautioned to obtain the latest editions. In this standard, the words ''shall/' "should,” and "may" represent requirements, recommendations, and options, respectively, as specified in ANSI and CSA policy and style guides. -

TES5 Serial Digital Multistandard TV Data Encoder Platform

TES5 Serial Digital Multistandard TV Data Encoder Platform Overview Key Features The Ross Video TES5 Serial Digital Multistandard TV Data Encoder / Inserter is a The TES5 combines the four highly flexible platform for encoding, inserting, receiving, bridging and multiplexing components necessary for TV data digital data in the vertical blanking interval (VBI) of any component serial digital TV transmission into one unit: signal. The TES5 has four input data ports that are enabled by software modules to accept RS-232 data; three ports are direct and one is via an internal 33.6Kbps • Communications: Four data modem or LAN adaptor. The TES5 can house up to four encoder software ports and VBI serial digital and modules for encoding and inserting up to four input data streams into a single VBI. analog data decoders can be The TES5 can operate in any television and AC power standard, and can encode used for data input and output. and insert data in any TV data format into either 525 or 625 line component serial digital video signals. • Processing: The heart of the TES5 is an Intel Prosessor The TES5 can be used as an encoder/inserter for encoding and inserting with FLASH disk. Data formatting asynchronous serial RS-232 data streams into the VBI, or as a data bridge for is handled by the unit and Ross extracting the data from the VBI of one video source and inserting it into the VBI Video encoder software modules of another. Standard encoder software modules are available for broadcasting or are stored in non-volatile bridging data meeting North American (NABTS), European (WST) or Japanese memory. -

Benefits Applications 2 Channel Hd/Sd Encoder

MODEL ENEN--2020 2 CHANNEL HD/SD ENCODER The EN-20 is a two-channel High and Standard defini- FEATURES | BENEFITS tion distribution encoder supporting ATSC and DVB via QAM, ASI and IP distribution platforms with MPEG-2 and AVC/H.264/MPEG-4 hardware options. 2-Channel high definition encoding Automatic SD and HD detection It inherits Adtec’s broadcast quality compression, ad- vanced feature set, service performance and reliability in SDI and CVBS Video Interfaces the new dense two-channel platform targeted towards broadcasters, cable and IP compression applications. Optional QAM modulation and RF up-conversion MPEG-2 and MPEG-4 encoding hardware options available The device automatically detects video and audio from two sources (combination of HD and SD acceptable), en- EAS, Time Code, Captions, Teletext and other VBI support codes, multiplexes and sends them back out as one com- bined TS via IP, ASI or optional QAM. Closed captioning Front Panel, Web UI, SNMP control and monitoring and support for Emergency Alert (EAS) ASI and IP Transport (IP supports UDP, RTP, and SMPTE are standard. 2022 FEC) Simultaneous ASI, IP, and QAM transport APPLICATIONS ATSC, DVB Distribution Tier Two/Three Contribution Private and MSO Cable Systems Campus, Hospitality, Education V11.2015 Dolby is a registered trademarks of Dolby laboratories. Listed features are dependent upon installed hardware and software options, features are subject to change. www.amt.com EN-20 Dual Channel HD/SD Encoder VIDEO ENCODER PROFILES: * VBI / VANC PROCESSING: EN-20-MP2 (MPEG2) -

CLOSED CAPTIONING with the LINE 21 SYSTEM Sharon Earley

CLOSED CAPTIONING WITH THE LINE 21 SYSTEM Sharon Earley NATIONAL CAPTIONING INSTITUTE, INC. ABSTRACT nationally. At present, 300,000 viewers across ~he country who use Line 21 Tele Closed captioning has enabled the hear Captio~decoding devices enjoy over 40 ing impaired to enjoy television more fully hours per week of predominantly prime-time over the past three years. Although over network programming. More than 200 major the-air broadcasters have provided the bulk advertisers caption their commercials and of closed-captioned programs, the partici support the costs of captioning television pation of the cable industry is both grow specials and series. ing and promising. The Line 21 system, with its proven transmission and reception Although the closed-caption service strengths, is an ideally suited caption began three years ago primarily as a delivery system for cablecasters. The Line broadcast network service, it has expanded 21 signal passes intact over satellite and into many other delivery systems - cable. It can be recorded in three-quarter satellite syndication, videocassette, and half-inch formats, and no special ac videodisk, local broadcast and cable. commodations are required to retransmit it. Decoding devices, specifically designed for DEVELOPMENTS IN CABLE cable, are currently available, as is a system which enables a local operator to The cable industry's first involve caption its own prograrrming in a cost ment in closed captioning was the delivery effective manner. The National Captioning of closed-captioned network programs to Institute sees the full participation of subscribers. Since 1982, however, cable cablecasters in the provision of closed support and involvement in the closed captions as an important step in increas caption service has been active and ing the access of the hearing impaired to growing rapidly. -

Cisco Powervu Model D9850 Program Receiver Data Sheet

Data Sheet Cisco PowerVu Model D9850 Program Receiver Product Overview The Cisco ® PowerVu ® Model D9850 Program Receiver (Figure 1) is designed for satellite content distribution applications requiring 4:2:0 video decoding. The receiver can receive digitally encrypted video, audio, utility data, and vertical blanking interval (VBI) data. Figure 1. Cisco PowerVu Model D9850 Program Receiver Analog Cable Program Distribution Composite video and balanced audio outputs can be connected to analog modulators for analog cable distribution. Four mono audio channels or two stereo pairs are available for primary audio programs, as well as secondary audio programs (SAP). For example, primary program audio could be carried on one of the stereo pairs, while SAP audio is carried on the other stereo pair. Digital Cable Program Distribution Uplink-addressable transport output provides MPEG program streams for digital tier program delivery, so quality video programs can be distributed efficiently to households equipped with digital set-top boxes. Digital Program Replacement Digital program replacement (DPR) allows programmers to transparently switch their primary service to an alternative service in the digital domain in blackout applications for cable digital tier distribution. This feature remaps the packet identifier (PID) information from the primary service to an alternate service, allowing downstream devices to continue to operate seamlessly. This helps make alternative programming available in the digital tier without operator intervention. Cable Headend Advertisement Insertion For flexible advertisement insertion configurations, this receiver provides four types of outputs: ● Dual-tone multifrequency (DTMF) cue tone ● Cue trigger support, with eight open collector outputs ● One programmable contact closure ● Digital program insertion (DPI) messaging using Asynchronous Serial Interface (ASI) output Low-Speed Data Output Asynchronous utility data (up to 38.4 kbps) is available through an RS-232 interface. -

United States Patent (19) 11 Patent Number: 6,067,122 Cahill, III (45) Date of Patent: May 23, 2000

US006067122A United States Patent (19) 11 Patent Number: 6,067,122 Cahill, III (45) Date of Patent: May 23, 2000 54) HOST-BASEDANTI-GHOSTING OF 5,600,380 2/1997 Patel et al. .............................. 348/614 TELETEXT DATA BASED ON 5,619.275 4/1997 Tults ........... ... 348/468 NON-OVERSAMPLED DATA 5,627,594 5/1997 Van Gestel. 348/468 5,812.207 9/1998 Cahill .......... ... 348/465 (75) Inventor: Benjamin M. Cahill, III, Ringoes, N.J. 5,812,217 9/1998 Cahill, III ............................... 348/614 Primary Examiner John K. Peng 73 Assignee: Intel Corporation, Santa Clara, Calif. ASSistant Examiner-Linus H. Lo Attorney, Agent, or Firm Blakely, Sokoloff, Taylor & 21 Appl. No.: 09/066,741 Zafman LLP 22 Filed: Apr. 23, 1998 57 ABSTRACT 51 Int. C.7 - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - HO)4N 5/21; HO4N 7/00 A method and apparatuS C provided for performing host 52 U.S. Cl. .......................... 348/478; 348/468; 348/466; based anti-ghosting of teletext data in a television signal 348/461; 348/614 using non-oversampled data. Teletext data is first encoded 58 Field of Search ..................................... 348/478,476, within a television Signal using multi-level error correction 348/473, 468, 466, 461, 614, 465 encoding, including the use of an inner correction code and an outer correction code. The television signal is then 56) References Cited transmitted using multiple Signal level modulation encoding, U.S. PATENT DOCUMENTS while adhering to the Standard teletext timing. A remote computer System receives the television Signal containing 4,388,645 6/1983 Cox et al. ................................. 358/86 the encoded teletext data. -

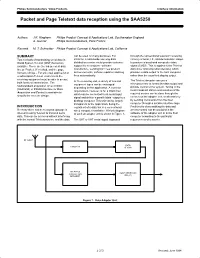

Packet and Page Teletext Data Reception Using the SAA5250

Philips Semiconductors Video Products Interface information Packet and Page Teletext data reception using the SAA5250 Authors: J.R. Kinghorn Philips Product Concept & Applications Lab, Southampton England A. Guenot Philips Semiconductors, Paris France Revised: M. T. Schneider Philips Product Concept & Applications Lab, California SUMMARY can be used for many purposes. For through the conventional television receiving Two methods of transmitting serial data in instance, a nationwide one way data circuitry of tuner, I.F., and demodulator stages World System Teletext (WST) format are distribution service could provide customer to produce a baseband composite video available. These are the independent data support for a computer software signal (CVBS). This is applied to the Teletext line or ‘Packet 31’ method, and the page manufacture, sending both new product data slicer and acquisition decoder, which format technique. For universal application in announcements, software updates and bug provides a data output to the host computer a subscription Teletext environment the fixes automatically. rather than the usual text display output. receiving equipment must be able to accept At the receiving end, a variety of terminal The Teletext decoder can use a both forms of transmission. The equipment types can be envisaged microprocessor to format the data output and Multistandard acquisition circuit CIDAC depending on the application. A common provide control of the system. Tuning in the (SAA5250) or CMOS Interface for Data requirement, however, is for a ‘black box’ local broadcast station and selection of the Acquisition and Control, is available to which can be connected to an aerial input required service can be done through the simplify the receiver design. -

HMP8117 Datasheet

HMP8117 NTSC/PAL Video Decoder NOT RECOMMENDED FOR NEW DESIGNS DATASHEET NO RECOMMENDED REPLACEMENT The HMP8117 is a high qual contact our Technical Support Center at decoder with internal A/D conv 1-888-INTERSIL or www.intersil.com/tsc NTSC M, PAL B, D, G, H, I, M,ity N, NTSC and combinationand PAL video N (N video standards. erters. It is compatible with FN4643 Rev 4.00 Both composite and S-video Features July 29, 2009 ) supported. A 2-line comb fil C • (M) NTSC and (B, D chrominance trap fil (Y/C) input formats are ter plus a user-selectable - Optional Auto Detect, G,of VideoH, I, M, Standard N, N User adjustments includeter provide brig high quality Y/C separation. - ITU-R BT.601 (CCIR601) and Square Pixel) PAL Operation Operation hue, and sharpness. C htness, contrast, saturation, • Videolyzer Feature Vertical blanking interval (VBI) data, such as Closed - Macrovision™ Bypass and Detection Captioning, Wide Screen Sig captured and output • Digital Anti-Alias Filter nalling and Teletext, may be Captioning and Wide asScreen BT.656 Signalling ancillary information data. Closed may also • Power Down Mode be read out via the I • Digital Output Formats 2C interface. The Videolyzer™ feature provides approved Macrovision - VMI Compatible copy-protection bypass and detection. - 8-bit, 16-bit 4:2:2 YCbCr - 15-bit (5, 5, 5), 16-bit (5, 6, 5) RGB Ordering Information ™ - Linear or Gamma-Corrected -8-bit BT.656 PART NUMBER • Analog Input Formats PART TEMP HMP8117CN HMP8117CNMARKING 0 to +70 80RANGE Ld PQFP - Three Analog Composite Inputs (°C) PACKAGE PKG - Analog Y/C (S-video) Input HMP8117CNZ DWG. -

Multistandard TV Data Encoder Platform

TES3 Multistandard TV Data Encoder Platform Overview Key Features The TES3 Multistandard TV Data Encoder / Inserter is a highly flexible platform The TES3 combines the four for encoding, inserting, receiving, bridging and multiplexing digital data in the components necessary for TV data vertical blanking interval (VBI) of any television signal. The TES3 has 4 input data transmission into one unit: ports that are enabled by software modules to accept RS232 data; 3 ports are direct and one is via an internal 33.6Kbps modem or 10Base-T LAN adaptor. • Communications: Multiple data The TES3 can house up to four software modules for encoding and inserting up to ports and internal TV data 4 input data streams into a single VBI. The TES3 is the first world-capable TV Data decoders for data input and Encoder platform that can operate in any television and AC power standard, and output. can encode and insert data in any TV data format. • Processing: The heart of the The TES3 can be used as an encoder / inserter for encoding and inserting TES3 is an Intel processor with asynchronous serial RS232 or LAN data streams into the VBI, or as a data bridge FLASH disk. The various modes for extracting the data from the VBI of one video source and inserting it into the and features of the TES3 VBI of another. Standard encoder software modules are available for broadcasting platform are enabled by loading or bridging data meeting North American (NABTS), European (WST) or Japanese Ross Video software modules (JTES) standards for teletext data transmission.