Procyon Arcade Fpga Hdmi Board Brief Description

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

What Way Is It Meant to Be Played?

What Way Is It Meant To Be Played? Florian Mihola March 2020 Abstract and home video game consoles digital inputs were the standard up until the “16-bit” era of the 1990s. The most commonly used interface between a Sony PlayStation, Nintendo 64 and Sega Saturn fi video game and the human user is a handheld are among the rst which brought with them ad- “game controller”, “game pad”, or in some occa- ditional analog controls—either at launch or as an sions an “arcade stick.” Directional pads, analog updated controller option. And even though mod- sticks and buttons—both digital and analog—are ern mass-market offerings include analog sticks linked to in-game actions. One or multiple simul- and analog triggers, digital buttons and directional taneous inputs may be necessary to communicate pads remain the ubiquitous fundamentals of input. the intentions of the user. Activating controls may The simple nature and widespread use of digital be more or less convenient depending on their po- inputs leads to a degree of interoperability: Game sition and size. In order to enable the user to per- software is not necessarily tied to a single game fi form all inputs which are necessary during game- controller—whether we interpret this as a speci c play, it is thus imperative to find a mapping be- model, a design and protocol available by different tween in-game actions and buttons, analog sticks, manufacturers, or a class of generic controllers— and so on. We present simple formats for such but can be enjoyed using a range of controllers, mappings as well as for the constraints on possi- provided they share at least some common char- ble inputs which are either determined by a phys- acteristics. -

Programme Edition

JOURNEE 13h00 - 18h00 WEEK END 14h00 - 19h00 JOURJOURJOUR Vendredi 18/12 - 19h00 Samedi 19/12 Dimanche 20/12 Lundi 21/12 Mardi 22/12 ThèmeThèmeThème Science Fiction Zelda & le J-RPG (Jeu de rôle Japonais) ArcadeArcadeArcade Strange Games AnimeAnimeAnime NES / Twin Famicom / MSXMSXMSX The Legend of Zelda Rainbow Islands Teenage Mutant Hero Turtles SC 3000 / Master System Psychic World Streets of Rage Rampage Super Nintendo Syndicate Zelda Link to the Past Turtles in Time + Sailor Moon Megadrive / Mega CD / 32X32X32X Alien Soldier + Robo Aleste Lunar 2 + Soleil Dynamite Headdy EarthWorm Jim + Rocket Knight Adventures Dragon Ball Z + Quackshot Nintendo 64 Star Wars Shadows of the Empire Furai no Shiren 2 Ridge Racer 64 Buck Bumble SaturnSaturnSaturn Deep Fear Shining Force III scénario 2 Sky Target Parodius Deluxe Pack + Virtual Hydlide Magic Knight Rayearth + DBZ Shinbutouden Playstation Final Fantasy VIII + Saga Frontier 2 Elemental Gearbolt + Gun Blade Arts Tobal n°1 Dreamcast Ghost Blade Spawn Twinkle Star Sprites Alice's Mom Rescue Gamecube F Zero GX Zelda Four Swords 4 joueurs Bleach Playstation 2 Earth Defense Force Code Age Commanders / Stella Deus Puyo Pop Fever Earth Defense Force Cowboy Bebop + Berserk XboxXboxXbox Panzer Dragoon Orta Out Run 2 Dead or Alive Xtreme Beach Volleyball Wii / Wii UWii U / Wii JPWii JP Fragile Dreams Xenoblade Chronicles X Devils Third Samba De Amigo Tatsunoko vs Capcom + The Skycrawlers Playstation 3 Guilty Gear Xrd Demon's Souls J Stars Victory versus + Catherine Kingdom Hearts 2.5 Xbox 360 / XBOX -

Procedural Audio for Video Games

Procedural Audio for Video Games: Are we there yet ? Nicolas Fournel – Principal Audio Programmer Sony Computer Entertainment Europe Overview • What is procedural audio ? • How can we implement it in games ? • Pre-production • Design • Implementation • Quality Assurance What is Procedural Audio ? First, a couple of definitions… Procedural refers to the process that computes a particular function Procedural content generation generating content by computing functions Procedural techniques in other domains Landscape generation • Fractals (terrain) • L-systems (plants) • Perlin noise (clouds) Procedural techniques in other domains Texture generation • Perlin noise • Voronoi diagrams Procedural techniques in other domains City creation (e.g. CityEngine) Procedural techniques in other domains • Demo scene: 64 Kb / 4Kb / 1 Kb intros • .kkrieger: 3D first person shooter in 96K from Farbrausch Procedural content in games A few examples: • Sentinel • Elite • DEFCON • Spore • Love Present in some form or another in a lot of games What does that teach us ? Procedural content generation is used: • due to memory constraints or other technology limitations • when there is too much content to create • when we need variations of the same asset • when the asset changes depending on the game context What does that teach us ? • Data is created at run-time • Is based on a set of rules • Is controllable by the game engine Defining Procedural Audio For sound effects: • Real-time sound synthesis • With exposed control parameters • Examples of existing systems: • Staccato Systems: racing and footsteps • WWISE SoundSeed (Impact and Wind / Whoosh) • AudioGaming Defining Procedural Audio For dialogue: • real-time speech synthesis e.g. Phonetic Arts, SPASM • voice manipulation systems e.g. -

CP/M-80 Kaypro

$3.00 June-July 1985 . No. 24 TABLE OF CONTENTS C'ing Into Turbo Pascal ....................................... 4 Soldering: The First Steps. .. 36 Eight Inch Drives On The Kaypro .............................. 38 Kaypro BIOS Patch. .. 40 Alternative Power Supply For The Kaypro . .. 42 48 Lines On A BBI ........ .. 44 Adding An 8" SSSD Drive To A Morrow MD-2 ................... 50 Review: The Ztime-I .......................................... 55 BDOS Vectors (Mucking Around Inside CP1M) ................. 62 The Pascal Runoff 77 Regular Features The S-100 Bus 9 Technical Tips ........... 70 In The Public Domain... .. 13 Culture Corner. .. 76 C'ing Clearly ............ 16 The Xerox 820 Column ... 19 The Slicer Column ........ 24 Future Tense The KayproColumn ..... 33 Tidbits. .. .. 79 Pascal Procedures ........ 57 68000 Vrs. 80X86 .. ... 83 FORTH words 61 MSX In The USA . .. 84 On Your Own ........... 68 The Last Page ............ 88 NEW LOWER PRICES! NOW IN "UNKIT"* FORM TOO! "BIG BOARD II" 4 MHz Z80·A SINGLE BOARD COMPUTER WITH "SASI" HARD·DISK INTERFACE $795 ASSEMBLED & TESTED $545 "UNKIT"* $245 PC BOARD WITH 16 PARTS Jim Ferguson, the designer of the "Big Board" distributed by Digital SIZE: 8.75" X 15.5" Research Computers, has produced a stunning new computer that POWER: +5V @ 3A, +-12V @ 0.1A Cal-Tex Computers has been shipping for a year. Called "Big Board II", it has the following features: • "SASI" Interface for Winchester Disks Our "Big Board II" implements the Host portion of the "Shugart Associates Systems • 4 MHz Z80-A CPU and Peripheral Chips Interface." Adding a Winchester disk drive is no harder than attaching a floppy-disk The new Ferguson computer runs at 4 MHz. -

Video Gaming and Death

Untitled. Photographer: Pawel Kadysz (https://stocksnap.io/photo/OZ4IBMDS8E). Special Issue Video Gaming and Death edited by John W. Borchert Issue 09 (2018) articles Introduction to a Special Issue on Video Gaming and Death by John W. Borchert, 1 Death Narratives: A Typology of Narratological Embeddings of Player's Death in Digital Games by Frank G. Bosman, 12 No Sympathy for Devils: What Christian Video Games Can Teach Us About Violence in Family-Friendly Entertainment by Vincent Gonzalez, 53 Perilous and Peril-Less Gaming: Representations of Death with Nintendo’s Wolf Link Amiibo by Rex Barnes, 107 “You Shouldn’t Have Done That”: “Ben Drowned” and the Uncanny Horror of the Haunted Cartridge by John Sanders, 135 Win to Exit: Perma-Death and Resurrection in Sword Art Online and Log Horizon by David McConeghy, 170 Death, Fabulation, and Virtual Reality Gaming by Jordan Brady Loewen, 202 The Self Across the Gap of Death: Some Christian Constructions of Continued Identity from Athenagoras to Ratzinger and Their Relevance to Digital Reconstitutions by Joshua Wise, 222 reviews Graveyard Keeper. A Review by Kathrin Trattner, 250 interviews Interview with Dr. Beverley Foulks McGuire on Video-Gaming, Buddhism, and Death by John W. Borchert, 259 reports Dying in the Game: A Perceptive of Life, Death and Rebirth Through World of Warcraft by Wanda Gregory, 265 Perilous and Peril-Less Gaming: Representations of Death with Nintendo’s Wolf Link Amiibo Rex Barnes Abstract This article examines the motif of death in popular electronic games and its imaginative applications when employing the Wolf Link Amiibo in The Legend of Zelda: Breath of the Wild (2017). -

Imitation and Limitation

Fake Bit: Imitation and Limitation Brett Camper [email protected] ABSTRACT adventure and role-playing games, which are traditionally less A small but growing trend in video game development uses the action-oriented. Several lesser known NES games contributed to “obsolete” graphics and sound of 1980s-era, 8-bit microcomputers the style early on as well, such as Hudson Soft’s Faxanadu (1989) to create “fake 8-bit” games on today’s hardware platforms. This and Milon’s Secret Castle (1986), as well as Konami’s The paper explores the trend by looking at a specific case study, the Goonies II (1987). In more recent decades, the Castlevania series platform-adventure game La-Mulana, which was inspired by the from Konami has also adopted and advanced the form, from Japanese MSX computer platform. Discussion includes the Symphony of the Night (1997) on PlayStation, through Portrait of specific aesthetic traits the game adopts (as well as ignores), and Ruin (2006) for the Nintendo DS. the 8-bit technological structures that caused them in their original La-Mulana is an extremely well made title that ranks among the 1980s MSX incarnation. The role of technology in shaping finest in this genre, displaying unusual craftsmanship and aesthetics, and the persistence of such effects beyond the lifetime cohesiveness. Its player-protagonist is Professor Lemeza, an of the originating technologies, is considered as a more general archaeologist explorer charting out vast underground ruins in a “retro media” phenomenon. distant, unspecified corner of the globe (Indiana Jones is an obvious pop culture reference, but also earlier examples like H. -

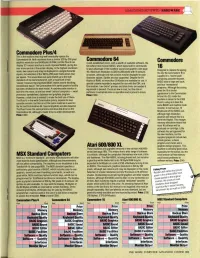

Commodore 16 Commodore Plus/4 MSX Standard Computers

•!. Commodore Plus/4 This is the machine that may well eventually replace the Commodore 64. Both machines have a similar 320 by 200 pixel Commodore 64 graphics resolution and 64 Kbytes of RAM, but the Plus/4 can A well-established micro, with a wealth of available software, the Commodore display 121 colours and has a much improved BASIC, giving the 64 suffers from its poor BASIC, which lacks built-in commands user more control of the screen display. In the highest resolution 16 to take advantage of the excellent sound and graphics (see page Designed to replace the ageing mode, two colours only may be displayed in a single character 10). Maximum resolution is 320 by 200 pixels with 16 colours square, but selection of the 160 by 200 pixel mode allows four Vic-20, the Commodore 16 is onscreen, although only two colours may be displayed in each supplied in a 'starter pack' per square. The sound does not quite match up to the high character square. Sprites are also supported. Despite the 64 standards of the Commodore 64, with a maximum of two containing cassette recorder, Kbytes of RAM, no more than 39 Kbytes are available for use. A BASIC tutorial tape and book. 'voices': however, the improved BASIC makes sound-handling special cassette recorder is required for use with the C64, and considerably easier. The Commodore 64's sprite graphics facility and four 'recreational' Commodore 'own brand' printers and disk drives are needed if programs. Although the casing has been omitted in the new model. A machine code monitor is expansion is desired. -

History of Video Games-Wikipedia

History of video games From Wikipedia, the free encyclopedia The Atari VCS was a popular home video game console in the late 1970s and early 1980s. Pictured is the four-switch model from 1980–1982. An Atari CX40 joystick controller, with a single button The history of video games goes as far back as the early 1950s, when academic computer scientists began designing simple games and simulations as part of their research or just for fun. At M.I.T. in the 1960s, professors and students played games such as 3D tic-tac-toe and Moon Landing. These games were played on computer such as the IBM 1560, and moves were made by means of punch cards. Video gaming did not reach mainstream popularity until the 1970s and 1980s, when video arcade games and gaming consoles using joysticks, buttons, and other controllers, along with graphics on computer screens and home computer games were introduced to the general public. Since the 1980s, video gaming has become a popular form of entertainment and a part of modern popular culture in most parts of the world. One of the early games was Spacewar!, which was developed by computer scientists. Early arcade video games developed from 1972 to 1978. During the 1970s, the first generation of home consoles emerged, including the popular game Pong and various "clones". The 1970s was also the era of mainframe computer games. The golden age of arcade video games was from 1978 to 1982. Video arcades with large, graphics- decorated coin-operated machines were common at malls and popular, affordable home consoles such as the Atari 2600 and Intellivision enabled people to play games on their home TVs. -

MSX Computer Magazine 2

De eerste echte computerstandaard heet vanaf nu MSX. Door Microsoft ™ ont wikkeld op een Spectravideo home-computer. Door steeds meerfabrikanten van ho me-computers overgenomen en toegepast. MSX stáát voor volledige uitwisselbaarheid van hard- en software. De Spectravideo SV 728 MSX is deze nieuwe computerstandaard waardig. Aan de binnenkant: krachtig en indruk wekkend. Aan de buitenkant: functioneel, strak en mooi genoeg om overal neer te zetten. Met een professioneel 90-toetsenbord, apart numeriek toetsenbord en speciale toetsen voor tekst verwerking. De ingebouwde MSX-basic met meer dan 140 commando's en statements complementeert de kracht van deze computer, die ook geen enkele moeite heeft met zakelijk gebruik. In alle opzichten: Compatible! Door de 5 1/4 inch diskdrive kunnen zowel MSX-DOS als CP/M 2.2 programma's gedraaid worden. Met de Spectravideo SV 728 MSX neem je alvast een voorschot op de toekomst. S ecifikaties. epu z aOA Kloksnelheid 3.6 M Hz Geheugen aOK byte RAM (64K gebruikers RAM + 16K video RAM voor graphics), 32K byte ROM.o ___ Software ingebouwde MSX Basic interpreter met meer dan 140 commando's en statements Specificaties 10 funktietoetsen, definieerbaar door de gebruiker. MSX-DOS en CP/ M compatible. Toetsenbord 90 toetsen ful l stroke incl. speciale toetsen en numeriek toetsenbord. Display Maximaal oplossend vermogen van 256*192 puntjes in de grafische mode. 40 kolommen x 40 lijnen in d:.:ec...:t7-'ex.:.:.t -'..:m.:.:oc::d::.e.~ ___ _______ 32 onafhankelijk programmeerbare sprites. 16 kleuren. Geluid 3 geluidskanalen met ieder a octaven. Op aanvraag is uitgebreide documentatie beschikbaar. svr Importeur: Electronics Nederland bv Tijnmuiden 15/ 19, 1046 AK Amsterdam. -

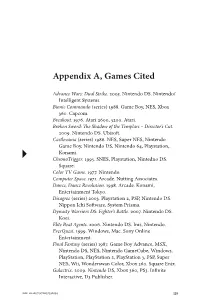

Appendix A, Games Cited

Appendix A, Games Cited Advance Wars: Dual Strike. 2005. Nintendo DS. Nintendo/ Intelligent Systems. Bionic Commando (series) 1988. Game Boy, NES, Xbox 360. Capcom. Breakout. 1976. Atari 2600, 5200. Atari. Broken Sword: The Shadow of the Templars – Director’s Cut. 2009. Nintendo DS. Ubisoft. Castlevania (series) 1986. NES, Super NES, Nintendo Game Boy, Nintendo DS, Nintendo 64, Playstation,. Konami. ChronoTrigger. 1995. SNES, Playstation, Nintedno DS. Square. Color TV Game. 1977. Nintendo. Computer Space. 1971. Arcade. Nutting Associates. Dance, Dance Revolution. 1998. Arcade. Konami, Entertainment Tokyo. Disagree (series) 2003. Playstation 2, PSP, Nintendo DS. Nippon Ichi Software, System Prisma. Dynasty Warriors DS: Fighter’s Battle. 2007. Nintendo DS. Koei. Elite Beat Agents. 2006. Nintendo DS. Inis, Nintendo. EverQuest. 1999. Windows, Mac. Sony Online Entertainment. Final Fantasy (series) 1987. Game Boy Advance, MSX, Nintendo DS, NES, Nintendo GameCube, Windows, PlayStation, PlayStation 2, PlayStation 3, PSP, Super NES, Wii, Wonderswan Color, Xbox 360. Square Enix. Galactrix. 2009. Nintendo DS, Xbox 360, PS3. Infinite Interactive, D3 Publisher. doi: 10.1057/9781137396594 Appendix Gun Fight. 1975. Arcade. Taito, Midway. Halo (series) 2001. (Xbox) Bungie, Micosoft Game Studios. Henry Hatsworth in the Puzzling Adventure. 2009. Nintendo DS. EA Tiburon, EA Games. Knights in the Nightmare. 2008. Nintendo DS. Sting, Sting Entertainment. Legend of Zelda Phantom Hourglass. 2007. Nintendo DS. Nintendo EAD. Metal Gear (series) 1987. NES, PC, Playstation, Playstation 2, Playstation 3, PSP, Xbox, Xbox360. Konami. Missile Command. 1980. Arcade. Atari. Mortal Kombat (series) 1992. Arcade, Super NES, Mega Drive/Genesis, Sega Mega CD, Amiga, Game Gear, Game Boy, Sega Master System, Midway Games, Nether Realms. -

Daily Coin Master

Daily Coin Master Daily Coin Master CLICK HERE TO ACCESS COIN MASTER GENERATOR Coin Master Hack No Human Verification - Add Free Coins and Spins. This new Coin Master Hack No Human Verification is out and you can finally use. You will see that if you decide to take advantage of this generator, you will certainly be better in this game. Article by Lukyan Stefan. 898. Our Coin Master Free Spins Promo Codes 2021 are 100% op working codes. These are the most up-to-date list of codes. you can redeem those Dear game lovers. we added here free spins for coin master. Here are the last up-to-date codes. we always update our list when a new coupon code comes. Use the Coin Master hack to get unlimited free coins and spins!... See more of Coin Master Hack & Cheats - Free Spins and Coins on Facebook. CoinMaster. Offers in-app purchases. Add to Wishlist. Install. Join your Facebook friends and millions of players around the world in attacks, ... ★ Coin Master is free on all devices with in-app purchases. Follow Coin Master on Facebook for exclusive offers and bonuses! Facebook: ... Coin Master: Free Spins and Coins [Daily Links August 2020]levvvel com › Gaming › Coin Master After you've invited all your friends and they have joined then you and your friends can gift each other free spins and coins every day! You don't lose any personal spins this way In total you can send... Our Coin Master Free Spins Promo Codes 2021 are 100% op working codes. These are the most up-to-date list of codes. -

Wii Terminology

Wii Terminology Wii Terminology Version: 3.0 Initial Version: 2005/05/25 Modified: 2007/04/24 © 2006-2007 Nintendo RVL-06-0115-001-D CONFIDENTIAL 1 Released: June 12, 2007 Wii Terminology Table of Contents Revision History 3 1. Console Names 6 2. Console Parts Names 7 3. Peripheral Names and Parts Names 9 4. Nintendo GameCube Console Names, Peripheral Names, and Parts Names 26 5. Terms and Expressions Related to Operations 29 6. Channel-Related Terms and Expressions 32 7. Screen Names 40 © 2006-2007 Nintendo RVL-06-0115-001-D CONFIDENTIAL 2 Released: June 12, 2007 Wii Terminology Revision History Version Revision Date Details of Revision General Unified the name used for the Wii console (Wii console, Wii, and console) to all read Wii console. 2. Console Parts Names ■Wii Console ・Replaced figure. 3. Peripheral Names and Parts Names ■Wii Remote, Strap, Nunchuk, Classic Controller, Wii AC Adaptor, Sensor Bar, Sensor Bar Stand, Wii AV Cable, Wii S-Video Stereo AV cable, Wii Component Video cable, Wii D-Terminal cable, Wii LAN adapter (Ethernet), Wii console stand, Wii stand plate ・Replaced figures. ■Sensor Bar and Sensor Bar Stand ・Added Description. ■Wii RGB cable, SD Card, Wii Points Card ・Added figures. ■LAN adaptor for Wii ・Changed from "LAN adapter" to "Wii LAN adapter (Ethernet)." ■Wii Points Card 3.0 2007/04/27 ・Divided "Wii Points Card" to detailed categories, "Wii Points Card 1000," "Wii Points Card 2000," and "Wii Points Card 5000." 5. Terms and Expressions Related to Operations ・Changed Description of "Register the Wii Remote with the Wii console." ・Deleted "Simple register the Wii Remote with the Wii console." ・Added "Normal-pair the Wii Remote with the Wii console." and "Simple-pair the Wii Remote with the Wii console." 6.1.