A Comparative Study of 64 Bit Microprocessors Apple, Intel and AMD

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Thermal Interface Material Comparison: Thermal Pads Vs

Thermal Interface Material Comparison: Thermal Pads vs. Thermal Grease Publication # 26951 Revision: 3.00 Issue Date: April 2004 © 2004 Advanced Micro Devices, Inc. All rights reserved. The contents of this document are provided in connection with Advanced Micro Devices, Inc. (“AMD”) products. AMD makes no representations or warranties with respect to the accuracy or completeness of the contents of this publication and reserves the right to make changes to specifications and product descriptions at any time without notice. No license, whether express, implied, arising by estoppel, or otherwise, to any intellectual property rights are granted by this publication. Except as set forth in AMD’s Standard Terms and Conditions of Sale, AMD assumes no liability whatsoever, and disclaims any express or implied warranty, relating to its products including, but not limited to, the implied warranty of merchantability, fitness for a particular purpose, or infringement of any intellectual property right. AMD’s products are not designed, intended, authorized or warranted for use as components in systems intended for surgical implant into the body, or in other applications intended to support or sustain life, or in any other application in which the failure of AMD’s product could create a situation where personal injury, death, or severe property or environmental damage may occur. AMD reserves the right to discontinue or make changes to its products at any time without notice. Trademarks AMD, the AMD Arrow logo, AMD Athlon, AMD Duron, AMD Opteron and combinations thereof, are trademarks of Advanced Micro Devices, Inc. Other product names used in this publication are for identification purposes only and may be trademarks of their respective companies. -

MOVR Mobile Overview Report April – June 2017

MOVR Mobile Overview Report April – June 2017 The first step in a great mobile experience TBD 2 The first step in a great mobile experience TBD 3 The first step in a great mobile experience Q1 2017 to Q2 2017 Comparisons Top Smartphones Top Smartphones Africa Asia Europe N. America Oceania S. America • New to the list this Apple iPhone 5S 1.3% 2.9% 4.1% 3.5% 3.9% 3.1% quarter are the Apple Apple iPhone 6 2.2% 4.8% 5.6% 9.3% 10.1% 4.5% iPhone SE and the Apple iPhone 6 Plus 0.8% 2.4% 0.9% 3.7% 3.2% 1.0% Samsung J7 Prime. Apple iPhone 6S 1.7% 4.4% 6.3% 11.0% 13.9% 3.1% Apple iPhone 6S Plus 0.7% 2.6% 1.1% 6.1% 4.6% 0.9% • Dropping off the list Apple iPhone 7 1.2% 2.9% 4.0% 7.6% 9.3% 2.2% are the Motorola Moto Apple iPhone 7 Plus 0.7% 3.1% 1.3% 6.9% 6.2% 1.1% G4, Samsung Galaxy J2 Apple iPhone SE 0.3% 0.6% 2.4% 2.2% 2.1% 1.0% (2015), and the Huawei P8 Lite 2.2% 0.3% 2.1% 0.2% 0.2% 0.6% Vodafone Smart Kicka. Motorola Moto G 0.0% 0.0% 0.1% 0.2% 0.0% 2.1% Motorola Moto G (2nd Gen) 0.0% 0.1% 0.0% 0.1% 0.1% 2.6% • North America and Motorola MotoG3 0.0% 0.1% 0.1% 0.2% 0.1% 3.1% Oceania continue to be Samsung Galaxy A3 1.2% 0.9% 2.2% 0.1% 0.2% 0.5% concentrated markets Samsung Galaxy Grand Neo 1.8% 0.8% 0.8% 0.1% 0.1% 0.6% for brands, with the Samsung Galaxy Grand Prime 0.5% 1.0% 1.5% 0.9% 0.1% 3.5% top smartphones Samsung Galaxy J1 1.8% 0.6% 0.3% 0.1% 0.3% 0.8% accounting for 63.7% and 74.4% Samsung Galaxy J1 Ace 2.5% 0.2% 0.0% 0.1% 0.3% 0.7% respectively. -

VOLUME V INFORMATIQUE NON AMERICAINE Première Partie Par L' Ingénieur Général De L'armement BOUCHER Henri TABLE

VOLUME V INFORMATIQUE NON AMERICAINE Première partie par l' Ingénieur Général de l'Armement BOUCHER Henri TABLE DES MATIERES INFORMATIQUE NON AMERICAINE Première partie 731 Informatique européenne (statistiques, exemples) 122 700 Histoire de l'Informatique allemande 1 701 Petits constructeurs 5 702 Les facturières de Kienzle Data System 16 703 Les minis de gestion de Nixdorf 18 704 Siemens & Halske AG 23 705 Systèmes informatiques d'origine allemande 38 706 Histoire de l'informatique britannique 40 707 Industriels anglais de l'informatique 42 708 Travaux des Laboratoires d' Etat 60 709 Travaux universitaires 63 710 Les coeurs synthétisables d' ARM 68 711 Computer Technology 70 712 Elliott Brothers et Elliott Automation 71 713 Les machines d' English Electric Company 74 714 Les calculateurs de Ferranti 76 715 Les études de General Electric Company 83 716 La patiente construction de ICL 85 Catalogue informatique – Volume E - Ingénieur Général de l'Armement Henri Boucher Page : 1/333 717 La série 29 d' ICL 89 718 Autres produits d' ICL, et fin 94 719 Marconi Company 101 720 Plessey 103 721 Systèmes en Grande-Bretagne 105 722 Histoire de l'informatique australienne 107 723 Informatique en Autriche 109 724 Informatique belge 110 725 Informatique canadienne 111 726 Informatique chinoise 116 727 Informatique en Corée du Sud 118 728 Informatique à Cuba 119 729 Informatique danoise 119 730 Informatique espagnole 121 732 Informatique finlandaise 128 733 Histoire de l'informatique française 130 734 La période héroïque : la SEA 140 735 La Compagnie -

Open APPLE THESIS FINAL__1 .Pdf

THE PENNSYLVANIA STATE UNIVERSITY SCHREYER HONORS COLLEGE DEPARTMENT OF SUPPLY CHAIN AND INFORMATION SYSTEMS SUPPLY CHAIN AS A SWORD AND A SHIELD: LESSONS FROM APPLE LAUREN E. STERN SPRING 2013 A thesis submitted in partial fulfillment of the requirements for a baccalaureate degree in Supply Chain and Information Systems with honors in Supply Chain and Information Systems Reviewed and approved* by the following: Felisa Preciado Clinical Associate Professor of Supply Chain and Information Systems Thesis Supervisor John C. Spychalski Professor Emeritus of Supply Chain Management Honors Adviser * Signatures are on file in the Schreyer Honors College. i ABSTRACT In the past few decades, Apple has gone from being an incredible startup success story, to a company on the very brink of failure, to its current status as one of the most valuable and emulated companies in the world. It originally got its start through technological innovations, laser-like focus and a sometimes uncanny understanding for what consumers would want, and those things have certainly been constant themes during its periods of success. But one of the biggest reasons for its outstanding success in the past decade has been the way Apple has leveraged its supply chain both to control costs and to give it a competitive advantage unmatched by any of its competitors. This paper analyzes the Apple supply chain to try to identify the way in which Apple has taken advantage of its supply chain, adapted it to changes in the market, and used it as both a defensive and offensive competitive weapon to become one of the most successful and influential companies in the world. -

SIMD Extensions

SIMD Extensions PDF generated using the open source mwlib toolkit. See http://code.pediapress.com/ for more information. PDF generated at: Sat, 12 May 2012 17:14:46 UTC Contents Articles SIMD 1 MMX (instruction set) 6 3DNow! 8 Streaming SIMD Extensions 12 SSE2 16 SSE3 18 SSSE3 20 SSE4 22 SSE5 26 Advanced Vector Extensions 28 CVT16 instruction set 31 XOP instruction set 31 References Article Sources and Contributors 33 Image Sources, Licenses and Contributors 34 Article Licenses License 35 SIMD 1 SIMD Single instruction Multiple instruction Single data SISD MISD Multiple data SIMD MIMD Single instruction, multiple data (SIMD), is a class of parallel computers in Flynn's taxonomy. It describes computers with multiple processing elements that perform the same operation on multiple data simultaneously. Thus, such machines exploit data level parallelism. History The first use of SIMD instructions was in vector supercomputers of the early 1970s such as the CDC Star-100 and the Texas Instruments ASC, which could operate on a vector of data with a single instruction. Vector processing was especially popularized by Cray in the 1970s and 1980s. Vector-processing architectures are now considered separate from SIMD machines, based on the fact that vector machines processed the vectors one word at a time through pipelined processors (though still based on a single instruction), whereas modern SIMD machines process all elements of the vector simultaneously.[1] The first era of modern SIMD machines was characterized by massively parallel processing-style supercomputers such as the Thinking Machines CM-1 and CM-2. These machines had many limited-functionality processors that would work in parallel. -

User's Manual User's Manual

User’s Manual (English Edition) Intel Pentium 4 Socket 478 CPU AMD Athlon/ Duron/Athlon XP Socket 462 CPU AMD Athlon 64 Socket 754 CPU ZM-WB2 Gold * Please read before installation http://www.zalman.co.kr http://www.zalmanusa.com 1. Features 1) Gold plated pure copper base maximizes cooling performance and prevents CPU blocks from galvanic corrosion 2) Intel Pentium 4 (Socket 478), AMD Athlon/Duron/Athlon XP (Socket 462),Athlon 64 (Socket 754) compatible design for broad compatibility. 3) Three types of compression fitting are offered for use with water tubes (8X10mm,8X11mm,10X13mm) * Zalman Tech. Co., Ltd. is not responsible for any damage resulting from CPU OVERCLOCKING. 2. Specifications Part No Part name Q’ ty Weight (g) Use 1 CPU block 1 447.0 CPU mountimg 2 Hand screw 2 8.0 Clip mountimg 3 Thermal grease 1 1.8 Apply to cpu core 4 Clip 1 9.6 CPU block mountimg 5 User’s manual 1 6 Clip supports 2 8.2 Socket 478 7 Clip supports A 2 5.0 Socket 462 8 Clip supports B 2 5.0 Socket 462 9 Bolts 4 0.8 Clip supports, A, B-type 10 Paper washer 1 set 7, 8 mountimg 11 Nipple 2 6.2 Socket 754 mountimg 12 Back plate 60.0 Socket 754 mountimg Fitting to 13 Fitting 3 set 8 x 10mm, 8 x 11mm, 10 x 13mm tubes NOTE 1) The maximum weight for the cooler is specified as 450g/450g/300g for socket 478/754/462 respectively. Special care should be taken when moving a computer equipped with a cooler which exceeds the relevant weight limit. -

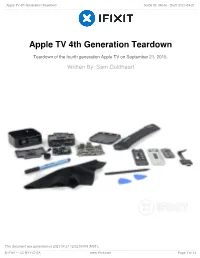

Apple TV 4Th Generation Teardown Guide ID: 49046 - Draft: 2021-04-21

Apple TV 4th Generation Teardown Guide ID: 49046 - Draft: 2021-04-21 Apple TV 4th Generation Teardown Teardown of the fourth generation Apple TV on September 21, 2015. Written By: Sam Goldheart This document was generated on 2021-04-21 12:02:09 PM (MST). © iFixit — CC BY-NC-SA www.iFixit.com Page 1 of 14 Apple TV 4th Generation Teardown Guide ID: 49046 - Draft: 2021-04-21 INTRODUCTION Apple fans are doing the happy dance, what with a slew of new devices coming out of Cupertino— including the first new Apple TV in more than three years. Our teardown engineers look pretty happy too. That's because we've got our hands on a 4th generation Apple TV. That's right, kids. It's teardown time! Don't touch that dial—unless you're looking for more teardown news on our Facebook, Instagram, or Twitter. [video: https://www.youtube.com/watch?v=lSA8uFwptJc] TOOLS: iFixit Opening Picks set of 6 (1) Spudger (1) T7 Torx Screwdriver (1) T3 Torx Screwdriver (1) This document was generated on 2021-04-21 12:02:09 PM (MST). © iFixit — CC BY-NC-SA www.iFixit.com Page 2 of 14 Apple TV 4th Generation Teardown Guide ID: 49046 - Draft: 2021-04-21 Step 1 — Apple TV 4th Generation Teardown We like to start with some specs, and in this case a lot of the good stuff is packed into the fancypants new remote. The box itself contains: Dual-core, 64-bit Apple A8 chip Ethernet, 802.11a/b/g/n/ac Wi-Fi, IR receiver, and HDMI 1.4 connectivity ...whilst the remote is packing: Glass Touch surface Dual microphones Accelerometer and gyroscope Bluetooth 4.0, IR transmitter, Lightning connector This document was generated on 2021-04-21 12:02:09 PM (MST). -

TSMC Integrated Fan-Out (Info) Package Apple A10

Electronic Costing & Technology Experts 21 rue la Nouë Bras de Fer 44200 Nantes – France Phone : +33 (0) 240 180 916 email : [email protected] www.systemplus.fr September 2016 – Version 1 – Written by Stéphane ELISABETH DISCLAIMER : System Plus Consulting provides cost studies based on its knowledge of the manufacturing and selling prices of electronic components and systems. The given values are realistic estimates which do not bind System Plus Consulting nor the manufacturers quoted in the report. System Plus Consulting is in no case responsible for the consequences related to the use which is made of the contents of this report. The quoted trademarks are property of their owners. © 2016 by SYSTEM PLUS CONSULTING, all rights reserved. 1 Return to TOC Glossary 1. Overview / Introduction 4 – A10 Die Analysis 57 – Executive Summary – A10 Die View, Dimensions & Marking – Reverse Costing Methodology – A10 Die Cross-Section – A10 Die Process Characteristics 2. Company Profile 7 – Comparison with previous generation 65 – Apple Inc. – A9 vs. A10 PoP – Apple Series Application processor – A9 vs. A10 Process – Fan-Out Packaging – TSMC Port-Folio 4. Manufacturing Process Flow 70 – TSMC inFO packaging – Chip Fabrication Unit – Packaging Fabrication Unit 3. Physical Analysis 15 – inFO Reconstitution Flow – Physical Analysis Methodology – iPhone 7 Plus Teardown 17 5. Cost Analysis 81 – A10 Die removal – Synthesis of the cost analysis – A10 Package-on-Package Analysis 23 – Main steps of economic analysis – A10 Package View, Dimensions – Yields Hypotheses – A10 Package XRay View – Die Cost Analysis 86 – A10 Package Opening – Wafer Cost – A10 Package Marking – Die Cost – A10 Package Cross-Section – inFO Packaging Cost Analysis 90 – A10 Package Cross-Section – Adhesive & Passivation – Packaging Wafer Cost – A10 package cross-Section - TIVs – Packaging Cost per process Steps – A10 package cross-Section – Solder Balls – Component Cost – A10 package cross-Section – RDL – Land-Side Decoupling Capacitor Analysis 48 6. -

The Tablet That Can Replace Your Laptop What Makes Surface 3 the Tablet That Can Replace Your Laptop?

The tablet that can replace your laptop What makes Surface 3 the tablet that can replace your laptop? The Best of Works like Runs Windows Great Pen a Tablet a Laptop & Office Experience Ultra-thin, ultra-light, ultra-durable Intel processor so you can run Works with old and new The optional Surface Pen feels all of your favorite Windows devices – like smartphones, cameras, and works just like a real pen, Up to 10 hours of video playback desktop software printers – more than any other OS and now comes in 2 vibrant colors Watch videos hands-free with Be productive anywhere Install millions of desktop apps One click opens OneNote, a 3-position Kickstand with a removable keyboard even when Surface 3 is For a limited time*, one year of Microsoft Office 365 Personal** and 3-position Kickstand locked or asleep comes included – a $69.99 value – with Connect to your devices with full versions of Excel, Word, PowerPoint, Palm block technology lets you powerful ports including OneNote, and Outlook, plus rest your hand on the screen, USB 3.0 OneDrive cloud storage. and you can apply natural pressure for thicker ink Use it however you want – with the Surface Pen, with touch, or with a mouse and keyboard How does Surface 3 beat iPad Air 2? Unlike iPad Air 2, Surface 3 works with all of your favorite devices like printers, smartphones, and cameras. iPad Air 2 is a tablet. Surface 3 gives you all the You can install millions of desktop apps and hundreds of thousands of touch-first apps on Surface 3. -

Amd Athlon Ii X2 270 Manual

Amd Athlon Ii X2 270 Manual Specifications. Please visit AMD Athlon II X2 215 (rev. C3) and AMD Athlon II X2 270 pages for more detailed specifications. Review, Differences, Benchmarks, Specifications, Comments Athlon II X2 270. CPUBoss recommends the AMD Athlon II X2 270 based on its. See full details. Specifications. Please visit AMD Athlon II X2 270 and AMD Athlon II X2 280 pages for more detailed specifications of both. Far Cry 4 on AMD Athlon x2 340(Dual Core) 4GB RAM HD 6570 PC Specifications. Specifications. Please visit AMD Athlon II X2 270 and AMD FX-6300 pages for more detailed specifications of both. AMD Athlon II x2 260 (3.2GHz) Although the specifications of this cpu list 74C as the max temp, i prefer to stick to the old "65C max" rule-of-thumb for amd cpus. Amd Athlon Ii X2 270 Manual Read/Download AMD Athlon II X2 270u. 2 GHz, Dual core. Front view of AMD Athlon II X2 270u. 5.9 Out of 10. VS Review, Differences, Benchmarks, Specifications, Comments. Photos of the AMD Athlon II X2 270 Black Edition from the KitGuru Price Comparison Engine. Specifications. Please visit AMD Athlon II X2 270 and AMD FX-4300 pages for more detailed specifications of both. SPECIFICATIONS : Model : AMD Athlon II X2 270. CPU Clock Speed : 3.4 GHz. Core : 2. Total L2 Cache : 2 MB Sockets : Socket AM2+,Socket AM3 Supported. up vote -5 down vote favorite. These are my specifications: AMD Athlon II x2 270 CPU, AMD 760g GPU, 4GB RAM. grand-theft-auto-5. -

SMART MOVEMENT DETECTION for ANDROID PHONES a Degree Thesis Submitted to the Faculty of the Escola Tècnica D'enginyeria De Tele

SMART MOVEMENT DETECTION FOR ANDROID PHONES A Degree Thesis Submitted to the Faculty of the Escola Tècnica d'Enginyeria de Telecomunicació de Barcelona Universitat Politècnica de Catalunya by Pablo Navarro Morales In partial fulfilment of the requirements for the degree in TELECOMMUNICATION ENGINEERING Advisor: Sergio Bermejo Barcelona, October 2016 Abstract This project describes a decision tree based pedometer algorithm and its implementation on Android using machine learning techniques. The pedometer can count steps accurately and It can discard irrelevant motion. The overall classification accuracy is 89.4%. Accelerometer, gyroscope and magnetic field sensors are used in the device. When user puts his smartphone into the pocket, the pedometer can automatically count steps. A filter is used to map the acceleration from mobile phone’s reference frame to the direction of gravity. As a result of this project, an android application has been developed that, using the built-in sensors to measure motion and orientation, implements a decision tree based algorithm for counting steps. 2 Resumen Este proyecto describe un algoritmo para un podómetro basado en un árbol de decisiones y su aplicación en Android utilizando técnicas de aprendizaje automático. El podómetro puede contar los pasos con precisión y se puede descartar el movimiento irrelevante. La precisión de la clasificación general es del 89,4%. Un acelerómetro, un giroscopio y un sensor de campo magnético se utilizan en el dispositivo. Cuando el usuario pone su teléfono en el bolsillo, el podómetro puede contar automáticamente pasos. Un filtro se utiliza para asignar la aceleración del sistema de referencia de teléfono móvil a la dirección de la gravedad. -

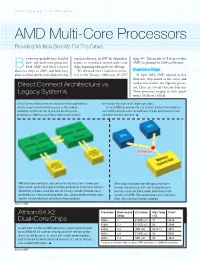

AMD Multi-Core Processors Providing Multiple Benefits for the Future

hard hat area | white paper AMD Multi-Core Processors Providing Multiple Benefits For The Future y now you probably have heard of variations this year. In 2007 the chipmakers (page 50). This month, we’ll focus on what dual- and multi-core processors. expect to introduce several multi-core AMD has planned for 2006 and beyond. B Both AMD and Intel released chips, beginning with quad-core offerings. dual-core chips in 2005, and both have We discussed Intel’s multi-core proces- Dual-Core Chips plans to release dozens more dual-core chip sors in the January 2006 issue of CPU In April 2005, AMD released its first dual-core chip aimed at the server and workstation market, the Opteron proces- Direct Connect Architecture vs. sor. There are several Opteron dual-core Legacy Systems 90nm processors ranging in clock speeds from 1.6GHz to 2.4GHz. Direct Connect Architecture lives up to its name by providing a for the past few years in its single-core chips. direct connection between the processor, the memory But now AMD has extended the use of Direct Connect Architecture to controller, and the I/O area to improve overall system connect the cores on a dual- or multi-core chip die and to connect each performance. AMD has used Direct Connect Architecture core to its memory controller. ▲ With multi-core architecture, each core on the chip has its own memory con- When using a dual-processor x86 legacy architecture, troller, which significantly improves memory performance. Using Direct Connect however, two processors then have to share the same Architecture to make a connection with the memory controller eliminates most memory control hub, which creates bottlenecks in data bottlenecks and makes multitasking easier.