SPARC/MEM-20 Installation Guide P/N 204227Edition6.0 P/N October 2001

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

SPARC/CPU-5V Technical Reference Manual

SPARC/CPU-5V Technical Reference Manual P/N 203651 Edition 5.0 February 1998 FORCE COMPUTERS Inc./GmbH All Rights Reserved This document shall not be duplicated, nor its contents used for any purpose, unless express permission has been granted. Copyright by FORCE COMPUTERS CPU-5V Technical Reference Manual Table of Contents SECTION 1 INTRODUCTION ....................................................................................1 1. Getting Started ..................................................................................................................................... 1 1.1. The SPARC CPU-5V Technical Reference Manual Set.................................................................. 1 1.2. Summary of the SPARC CPU-5V ................................................................................................... 2 1.3. Specifications ................................................................................................................................... 4 1.3.1. Ordering Information........................................................................................................... 6 1.4. History of the Manual ...................................................................................................................... 9 SECTION 2 INSTALLATION ....................................................................................11 2. Introduction........................................................................................................................................ 11 2.1. Caution -

Discontinued Emulex- Branded Products

Broadcom 1320 Ridder Park Drive San Jose, CA 95131 broadcom.com Discontinued Emulex- branded Products . Fibre Channel Host Bus Adapters . Fibre Channel HUBS . Switches . Software Solutions October 30, 2020 This document only applies to Emulex- branded products. Consult your supplier for specific information on OEM-branded products. Discontinued Emulex-branded Products Overview Broadcom Limited is committed to our customers by delivering product functionality and reliability that exceeds their expectation. Below is a description of key terminology and discontinued product tables. Table 1—Fibre Channel Host Bus Adapters . Table 2—Fibre Channel Optical Transceiver Kits . Table 3—Fibre Channel HUBs . Table 4—Switches . Table 5—Software Solutions Key Terminology End of Life (EOL) notification EOL indicates the date that distributors were notified of Broadcom intent to discontinue an Emulex model in production. Distributors are typically given a three-to-six month notice of Broadcom plans to discontinue a particular model. Final order This is the last date that Broadcom will accept orders from a customer or distributor. End of support This is the last date technical support is available for reporting software issues on discontinued models. The tables below indicate the last date of support or whether support has already ended. Software updates Active devices: Drivers for already supported operating system (OS) versions and firmware are updated periodically with new features and/ or corrections. Customers should check www.broadcom.com or call technical support for support of new OS versions for a given device. End of maintenance, Support Availability For software solutions, this is the last date software upgrades or updates are available. -

Sun Ultratm 2 Workstation Just the Facts

Sun UltraTM 2 Workstation Just the Facts Copyrights 1999 Sun Microsystems, Inc. All Rights Reserved. Sun, Sun Microsystems, the Sun Logo, Ultra, SunFastEthernet, Sun Enterprise, TurboGX, TurboGXplus, Solaris, VIS, SunATM, SunCD, XIL, XGL, Java, Java 3D, JDK, S24, OpenWindows, Sun StorEdge, SunISDN, SunSwift, SunTRI/S, SunHSI/S, SunFastEthernet, SunFDDI, SunPC, NFS, SunVideo, SunButtons SunDials, UltraServer, IPX, IPC, SLC, ELC, Sun-3, Sun386i, SunSpectrum, SunSpectrum Platinum, SunSpectrum Gold, SunSpectrum Silver, SunSpectrum Bronze, SunVIP, SunSolve, and SunSolve EarlyNotifier are trademarks, registered trademarks, or service marks of Sun Microsystems, Inc. in the United States and other countries. All SPARC trademarks are used under license and are trademarks or registered trademarks of SPARC International, Inc. in the United States and other countries. Products bearing SPARC trademarks are based upon an architecture developed by Sun Microsystems, Inc. OpenGL is a registered trademark of Silicon Graphics, Inc. UNIX is a registered trademark in the United States and other countries, exclusively licensed through X/Open Company, Ltd. Display PostScript and PostScript are trademarks of Adobe Systems, Incorporated. DLT is claimed as a trademark of Quantum Corporation in the United States and other countries. Just the Facts May 1999 Sun Ultra 2 Workstation Figure 1. The Sun UltraTM 2 workstation Sun Ultra 2 Workstation Scalable Computing Power for the Desktop Sun UltraTM 2 workstations are designed for the technical users who require high performance and multiprocessing (MP) capability. The Sun UltraTM 2 desktop series combines the power of multiprocessing with high-bandwidth networking, high-performance graphics, and exceptional application performance in a compact desktop package. Users of MP-ready and multithreaded applications will benefit greatly from the performance of the Sun Ultra 2 dual-processor capability. -

Sbus Specification B.O Written by Edward H

SBus Specification B.O Written by Edward H. Frank and Jim Lyle. Edited by Jim Lyle and Mike Harvey. Copyright ©1990 Sun Microsystems, Inc.-Printed in U.S.A. The Sun logo, Sun Microsystems, and Sun Workstation are registered trademarks of Sun Microsystems, Inc. Sun, Sun-2, Sun-3, Sun-4, Sun386i, Sunlnstall, SunOS, SunView, NFS, SunLink, NeWS, SPARC, and SPARCstation 1 are trademarks of Sun Microsystems, Inc. UNIX is a registered trademark of AT&T. The Sun Graphical User Interface was developed by Sun Microsystems, Inc. for its users and licensees. Sun acknowledges the pioneering efforts of Xerox in researching and developing the concept of visual or graphical user interfaces for the computer industry. Sun holds a non-exclusive license from Xerox to the Xerox Graphical User Interface, which license also covers Sun's licensees. All other products or services mentioned in this document are identified by the trademarks or service marks of their respective companies or organizations, and Sun Microsystems, Inc. disclaims any responsibility for specifying which marks are owned by which companies or organizations. All rights reserved. No part of this work covered by copyright hereon may be reproduced in any form or by any means-graphic, electronic, or mechanical-including photocopying, recording, taping, or storage in an information retrieval system, without the prior written permission of the copyright owner. Restricted rights legend: use, duplication, or disclosure by the U.S. government is subject to restrictions set forth in subparagraph (c)(1)(ii) of the Rights in Technical Data and Computer Software clause at DFARS 52.227-7013 and in similar clauses in the FAR and NASA FAR Supplement. -

Archived: Getting Started with Your SB-GPIB and NI-488.2M for Solaris 1

Getting Started with Your SB-GPIB and the NI-488.2M™ Software for Solaris 1 November 1993 Edition Part Number 320299-01 © Copyright 1991, 1994 National Instruments Corporation. All Rights Reserved. National Instruments Corporate Headquarters 6504 Bridge Point Parkway Austin, TX 78730-5039 (512) 794-0100 Technical support fax: (800) 328-2203 (512) 794-5678 Branch Offices: Australia (03) 879 9422, Austria (0662) 435986, Belgium 02/757.00.20, Canada (Ontario) (519) 622-9310, Canada (Québec) (514) 694-8521, Denmark 45 76 26 00, Finland (90) 527 2321, France (1) 48 14 24 24, Germany 089/741 31 30, Italy 02/48301892, Japan (03) 3788-1921, Netherlands 03480-33466, Norway 32-848400, Spain (91) 640 0085, Sweden 08-730 49 70, Switzerland 056/20 51 51, U.K. 0635 523545 Limited Warranty The SB-GPIB is warranted against defects in materials and workmanship for a period of two years from the date of shipment, as evidenced by receipts or other documentation. National Instruments will, at its option, repair or replace equipment that proves to be defective during the warranty period. This warranty includes parts and labor. The media on which you receive National Instruments software are warranted not to fail to execute programming instructions, due to defects in materials and workmanship, for a period of 90 days from date of shipment, as evidenced by receipts or other documentation. National Instruments will, at its option, repair or replace software media that do not execute programming instructions if National Instruments receives notice of such defects during the warranty period. National Instruments does not warrant that the operation of the software shall be uninterrupted or error free. -

Ross Technology RT6224K User Manual 1 (Pdf)

Full-service, independent repair center -~ ARTISAN® with experienced engineers and technicians on staff. TECHNOLOGY GROUP ~I We buy your excess, underutilized, and idle equipment along with credit for buybacks and trade-ins. Custom engineering Your definitive source so your equipment works exactly as you specify. for quality pre-owned • Critical and expedited services • Leasing / Rentals/ Demos equipment. • In stock/ Ready-to-ship • !TAR-certified secure asset solutions Expert team I Trust guarantee I 100% satisfaction Artisan Technology Group (217) 352-9330 | [email protected] | artisantg.com All trademarks, brand names, and brands appearing herein are the property o f their respective owners. Find the Ross Technology RT6224K-200/512S at our website: Click HERE 830-0016-03 Rev A 11/15/96 PRELIMINARY Colorado 4 RT6224K hyperSPARC CPU Module Features D Based on ROSS’ fifth-generation D SPARC compliant — Zero-wait-state, 512-Kbyte or hyperSPARC processor — SPARC Instruction Set Architec- 1-Mbyte 2nd-level cache — RT620D Central Processing Unit ture (ISA) Version 8 compliant — Demand-paged virtual memory (CPU) — Conforms to SPARC Reference management — RT626 Cache Controller, Memory MMU Architecture D Module design Management, and Tag Unit — Conforms to SPARC Level 2 MBus — MBus-standard form factor: 3.30” (CMTU) Module Specification (Revision 1.2) (8.34 cm) x 5.78” (14.67 cm) — Four (512-Kbyte) or eight D Dual-clock architecture — Provides CPU upgrade path at (1-Mbyte) RT628 Cache Data Units module level (CDUs) Ċ CPU scaleable up to -

Draft Standard for a Common Mezzanine Card Family

Introduction IEEE P1386/Draft 2.0 04-APR-1995 Draft Standard for a Common Mezzanine Card Family: CMC Sponsored by the Bus Architecture Standards Committee of the IEEE Computer Society P1386/Draft 2.0 April 4, 1995 Sponsor Ballot Draft Abstract: This draft standard defines the mechanics of a common mezzaninecard family. Mez- zanine cards designed to this draft standard can be usedinterchangeably on VME64 boards, Multibus I boards, Multibus II boards, Futurebus+ modules, desktopcomputers, portable com- puters, servers and other similar types of applications.Mezzanine cards can provide modular front panel I/O, backplane I/O or general function expansion or acombination for host comput- ers. Single wide mezzanine cards are 75 mm wide by 150 mm deep by 8.2 mmhigh. Keywords: Backplane I/O, Bezel, Board, Card, Face Plate, Front Panel I/O,Futurebus+, Host Computer, I/O, Local Bus, Metric, Mezzanine, Module, Modular I/O,Multibus, PCI, SBus, VME, VME64 or VMEbus Copyright (c) 1995 by the The Institute of Electrical and Electronics Engineers, Inc. 345 East 47th Street New York, NY 10017-2394, USA All rights reserved. This is an unapproved draft of a proposed IEEE Standard, subjectto change. Permission is hereby granted for IEEE Standards Committee participants toreproduce this document for pur- poses of IEEE standardization activities. If this document is tobe submitted to ISO or IEC, noti- fication shall be given to the IEEE Copyright Administrator.Permission is also granted for member bodies and technical committees of ISO and IEC toreproduce this document for pur- poses of developing a national position. Other entities seekingpermission to reproduce this document for standardization or other activities, or to reproduceportions of this document for these or other uses must contact the IEEE Standards Department forthe appropriate license. -

Fieldserver – EZ Gateway M-Bus to Modbus & Bacnet Start-Up Guide FS-EZX-MBUS-MOD-BAC

FieldServer – EZ Gateway M-Bus to Modbus & BACnet Start-up Guide FS-EZX-MBUS-MOD-BAC APPLICABILITY & EFFECTIVITY Effective for all systems manufactured after March 2019. Document Revision: 2.D T18604 EZ Gateway M-Bus to Modbus & BACnet Start-up Guide Technical Support Please call us for any technical support needs related to the FieldServer product. Sierra Monitor Corporation 1991 Tarob Court Milpitas, CA 95035 Website: www.sierramonitor.com U.S. Support Information: +1 408 964-4443 +1 800 727-4377 Email: [email protected] EMEA Support Information: +31 33 808 0590 Email: [email protected] Technical Support EZ Gateway M-Bus to Modbus & BACnet Start-up Guide TABLE OF CONTENTS 1 About the EZ Gateway......................................................................................................................................... 5 2 Certification .......................................................................................................................................................... 5 2.1 BTL Mark – BACnet Testing Laboratory ........................................................................................................ 5 3 Supplied equipment ............................................................................................................................................ 5 4 Installing the EZ Gateway ................................................................................................................................... 6 4.1 Mounting ........................................................................................................................................................ -

An Overview of Soc Buses

Vojin Oklobdzija/Digital Systems and Applications 6195_C007 Page Proof page 1 11.7.2007 2:16am Compositor Name: JGanesan 7 An Overview of SoC Buses 7.1 Introduction....................................................................... 7-1 7.2 On-Chip Communication Architectures ........................ 7-2 Background . Topologies . On-Chip Communication Protocols . Other Interconnect Issues . Advantages and M. Mitic´ Disadvantages of On-Chip Buses M. Stojcˇev 7.3 System-On-Chip Buses ..................................................... 7-4 AMBA Bus . Avalon . CoreConnect . STBus . Wishbone . University of Nisˇ CoreFrame . Manchester Asynchronous Bus for Low Energy . Z. Stamenkovic´ PI Bus . Open Core Protocol . Virtual Component Interface . m IHP GmbH—Innovations for High SiliconBackplane Network Performance Microelectronics 7.4 Summary.......................................................................... 7-15 7.1 Introduction The electronics industry has entered the era of multimillion-gate chips, and there is no turning back. This technology promises new levels of integration on a single chip, called the system-on-a-chip (SoC) design, but also presents significant challenges to the chip designers. Processing cores on a single chip may number well into the high tens within the next decade, given the current rate of advancements [1]. Interconnection networks in such an environment are, therefore, becoming more and more important [2]. Currently, on-chip interconnection networks are mostly implemented using buses. For SoC applications, design reuse becomes easier if standard internal connection buses are used for interconnecting components of the design. Design teams developing modules intended for future reuse can design interfaces for the standard bus around their particular modules. This allows future designers to slot the reuse module into their new design simply, which is also based around the same standard bus [3]. -

Sparc Cpu-8Vt

SPARC CPU-8VT Superior performance with redundancy features for business critical applications SPARC CPU-8VT — SPARCstation 5 compatibility with TurboSPARC performance in a single 6U VMEbus slot. The SPARC® CPU-8VT further enhances FORCE COMPUTERS single-slot SPARC family bringing TurboSPARC performance and redundancy features to your telecommunications and C3I applications. The addition of an external cache for the TurboSPARCTM doubles the perfor- mance of the fastest microSPARC CPU, while retaining the major microSPARC advantages of low power consumption and compact design. Couple this powerful CPU core with the integral workstation-type I/O found on the CPU-8VT and you have the ideal platform to develop and deploy powerful Solaris® and real-time applications. Further enhance this I/O with an integral sec- ond SCSI and a second Ethernet channel and you have a board that fulfils the typical requirements of most common high-availability and network routing applications without the necessity of adding SBus cards. Full compatibility with the established CPU-5VT provides a seamless upgrade path, extending our portfolio of high volume, premium price/performance embed- ded SPARC solutions for your applications. Facts... ...and features ◆ High-performance TurboSPARC processor ◆ Highest performance single-slot SPARC CPU ◆ 512 KByte L2 cache ◆ Functionally compatible with the Sun® SPARCstation 5 family and Solaris/SunOS® operating environment ◆ 16 to 128 MByte field upgradable Memory providing shared access to CPU, VME, SCSI, Ethernet & Centronics -

Computer Architectures an Overview

Computer Architectures An Overview PDF generated using the open source mwlib toolkit. See http://code.pediapress.com/ for more information. PDF generated at: Sat, 25 Feb 2012 22:35:32 UTC Contents Articles Microarchitecture 1 x86 7 PowerPC 23 IBM POWER 33 MIPS architecture 39 SPARC 57 ARM architecture 65 DEC Alpha 80 AlphaStation 92 AlphaServer 95 Very long instruction word 103 Instruction-level parallelism 107 Explicitly parallel instruction computing 108 References Article Sources and Contributors 111 Image Sources, Licenses and Contributors 113 Article Licenses License 114 Microarchitecture 1 Microarchitecture In computer engineering, microarchitecture (sometimes abbreviated to µarch or uarch), also called computer organization, is the way a given instruction set architecture (ISA) is implemented on a processor. A given ISA may be implemented with different microarchitectures.[1] Implementations might vary due to different goals of a given design or due to shifts in technology.[2] Computer architecture is the combination of microarchitecture and instruction set design. Relation to instruction set architecture The ISA is roughly the same as the programming model of a processor as seen by an assembly language programmer or compiler writer. The ISA includes the execution model, processor registers, address and data formats among other things. The Intel Core microarchitecture microarchitecture includes the constituent parts of the processor and how these interconnect and interoperate to implement the ISA. The microarchitecture of a machine is usually represented as (more or less detailed) diagrams that describe the interconnections of the various microarchitectural elements of the machine, which may be everything from single gates and registers, to complete arithmetic logic units (ALU)s and even larger elements. -

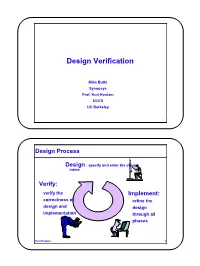

Design Verification

Design Verification Mike Butts Synopsys Prof. Kurt Keutzer EECS UC Berkeley 1 Design Process Design : specify and enter the design intent Verify: verify the Implement: correctness of refine the design and design implementation through all phases Kurt Keutzer 2 1 Design Verification HDL specification RTL manual Synthesis design netlist Is the Library/ design module logic generators optimization consistent with the original netlist specification? physical Is what I think I want design what I really want? layout Kurt Keutzer 3 Implementation Verification HDL RTL manual Synthesis design a 0 d netlist q b 1 Is the Library/ s clk implementation module logic generators optimization consistent with the original a 0 d q design intent? netlist b 1 s clk physical Is what I design implemented what I layout wanted? Kurt Keutzer 4 2 Manufacture Verification (Test) HDL Is the manufactured RTL manual circuit Synthesis design consistent with the a 0 d netlist q 1 Library/ b implemented s clk module logic design? generators optimization a 0 d Did they q b 1 netlist build s clk what I physical wanted? design layout Kurt Keutzer 5 Design Verification HDL specification RTL manual Synthesis design netlist Is the Library/ design module logic generators optimization consistent with the original netlist specification? physical Is what I think I want design what I really want? layout Kurt Keutzer 6 3 Verification is an Industry-Wide Issue Intel: Processor project verification: “Billions of generated vectors” “Our VHDL regression tests take 27 days to run. ” Sun: