LDO Basics (Rev. A)

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Basics of Linear Regulators ,Application Note

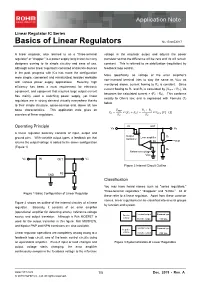

Linear Regulator IC Series Basics of Linear Regulators No.15020EAY17 A linear regulator, also referred to as a "three-terminal voltage in the regulator output and adjusts the power regulator" or "dropper," is a power supply long known to many transistor so that the difference will be zero and Vo will remain designers owning to its simple circuitry and ease of use. constant. This is referred to as stabilization (regulation) by Although some linear regulators consisted of discrete devices feedback loop control. in the past, progress with ICs has made the configuration More specifically, as voltage of the error amplifier's more simple, convenient and miniaturized, besides workable non-inversed terminal tries to stay the same as VREF as with various power supply applications. Recently, high mentioned above, current flowing to R2 is constant. Since efficiency has been a must requirement for electronic current flowing to R1 and R2 is calculated by (VREF / R2), Vo equipment, and equipment that requires large output current becomes the calculated current × (R1+R2). This conforms has mainly used a switching power supply, yet linear exactly to Ohm’s law, and is expressed with Formula (1) regulators are in strong demand virtually everywhere thanks below. to their simple structure, space-savings and, above all, low noise characteristics. This application note gives an 1 overview of linear regulators. Operating Principle IN OUT VIN VO A linear regulator basically consists of input, output and Output Error amplifier R1 ground pins. With variable output types, a feedback pin that transistor FB =VREF returns the output voltage is added to the above configuration + (Figure 1). -

A Low Dropout, CMOS Regulator with High PSR Over Wideband Frequencies Vishal Gupta, Student Member, IEEE, and Gabriel A

A Low Dropout, CMOS Regulator with High PSR over Wideband Frequencies Vishal Gupta, Student Member, IEEE, and Gabriel A. Rincón-Mora, Member, IEEE Abstract- Modern System-on-Chip (SoC) environments are advance towards integration, these state-of-the-art regulators swamped in high frequency noise that is generated by RF and are increasingly integrated “on-chip” and deployed at the digital circuits and propagated onto supply rails through point-of-load, with output currents in the range of 10 – 50 mA capacitive coupling. In these systems, linear regulators are used [9]–[15]. This strategy allows the regulators to be optimized to to shield noise-sensitive analog blocks from high frequency fluctuations in the power supply. This work presents a low cater to the specific demands of the sub-systems that load dropout regulator that achieves Power Supply Rejection (PSR) them [4]. Also, on-chip capacitors (10-200 pF) can often be better than -40dB over the entire frequency spectrum. The used for frequency compensation [9]-[15], thereby conserving system has an output voltage of 1.0V and a maximum current board-space and leading to increasing levels of integration. capability of 10mA. It consists of operational amplifiers (op Since the regulators do not use an external capacitor to amps), a bandgap reference, a clock generator, and a charge establish the dominant low-frequency pole, they are termed pump and has been designed and simulated using BSIM3 models “internally compensated regulators”. of a 0.5µm CMOS process obtained from MOSIS. In this work, the basic linear regulator and current schemes I. -

A Two-Module Linear Regulator with 3.9–10 V Input, 2.5 V Output, and 500 Ma Load

electronics Article A Two-Module Linear Regulator with 3.9–10 V Input, 2.5 V Output, and 500 mA Load Quanzhen Duan 1, Weidong Li 1, Shengming Huang 1,*, Yuemin Ding 2,*, Zhen Meng 3 and Kai Shi 2 1 School of Electrical and Electronic Engineering and Tianjin Key Laboratory of Film Electronic and Communication Devices, Tianjin University of Technology, Tianjin 300384, China; [email protected] (Q.D.); [email protected] (W.L.) 2 School of Computer and Science Engineering, Tianjin University of Technology, Tianjin 300384, China; [email protected] 3 Institute of Microelectronics of the Chinese Academy of Sciences, Beijing 100029, China; [email protected] * Correspondence: [email protected] (S.H.); [email protected] (Y.D.) Received: 7 September 2019; Accepted: 4 October 2019; Published: 10 October 2019 Abstract: A linear regulator with an input range of 3.9–10 V, 2.5 V output, and a maximal 500 mA load for use with battery systems was developed and presented here. The linear regulator featured two modules of a preregulator and a linear regulator core circuit, offering minimized power dissipation and high-level stability. The preregulator delivered an internal power voltage of 3 V and supplied internal circuits including the second module (the linear regulator core). The preregulator fitted with an active, low-pass filter provided a low-noise reference voltage to the linear regulator core circuit. To ensure operational stability for the linear regulator, error amplifiers incorporating the Miller compensation technique and featuring a large slewing rate were employed in the two modules. -

Voltage Regulator Solutions for Xilinx Virtex Edual Voltage Fpgas

Application Report SLVA086 - June 2000 Voltage Regulator Solutions for Xilinx Virtex E Dual Voltage FPGAs Bill Milus AAP Power Supplies ABSTRACT This application report serves as a reference for engineers designing with Xilinx 2.5-V and 1.8-V Virtex multivoltage FPGA products. It provides basic information on the issues facing engineers not experienced with multivoltage type products. Contents 1 Introduction . 2 2 Virtex Core and I/O Voltage Requirements. 2 3 Multivoltage Device Issues. 3 3.1 Xilinx Recommendations for Virtex Series FPGAs. 3 4 Load Current Estimations for Virtex Devices. 4 4.1 Core . 4 4.2 I/O . 4 4.3 Assumptions Used: Current Estimations for the Various Devices. 4 4.4 Core Assumptions . 4 4.5 I/O Considerations . 5 4.6 I/O Assumptions . 5 5 Supply Voltage Regulator Options. 7 5.1 Linear Regulators . 7 5.2 Inductive Switching Regulators. 7 5.3 Inductive Switching Power-Supply Module. 8 6 TI Recommended Solutions. 9 6.1 Switching Regulators ≥ 3 Amps. 10 6.2 Power Modules (Power Trends). 10 6.3 Summary . 11 List of Tables 1 Xilinx Virtex Offering . 2 2 Typical ICCINT Current Draw for Virtex Family. 5 3 Virtex Maximum User I/O Available in Package. 6 4 Virtex ICCIO (Output) mA. 6 5 Linear Regulators . 9 6 Dual-Output 250-mA to 1-A LDOs. 10 7 Switching-Regulator Solutions. 10 8 5-V/3.3-V Input Switching-Power-Supply Modules. 11 Virtex is a trademark of Xilinx, Inc. Other trademarks are the property of their respective owners. 1 SLVA086 1 Introduction Many devices, such as digital signal processors (DSP), microprocessors, and field- programmable gate arrays (FPGA), are designed to consume minimum power while providing high performance at low cost. -

ADP1762 (Rev. D)

2 A, Low VIN, Low Noise, CMOS Linear Regulator Data Sheet ADP1762 FEATURES TYPICAL APPLICATION CIRCUITS 2 A maximum output current ADP1762 VIN = 1.7V VOUT = 1.5V Low input voltage supply range VIN VOUT CIN COUT 10µF 10µF VIN = 1.10 V to 1.98 V, no external bias supply required SENSE Fixed output voltage range: VOUT_FIXED = 0.9 V to 1.5 V RPULL-UP ON 100kΩ EN Adjustable output voltage range: VOUT_ADJ = 0.5 V to 1.5 V PG PG OFF Ultralow noise: 2 μV rms, 100 Hz to 100 kHz SS VADJ Noise spectral density CSS VREG REFCAP 10nF C 4 nV/√Hz at 10 kHz CREG GND REF 1µF 1µF 3 nV/√Hz at 100 kHz 12922-001 Low dropout voltage: 62 mV typical at 2 A load Figure 1. Fixed Output Operation Operating supply current: 4.5 mA typical at no load ADP1762 VIN = 1.7V VOUT = 1.5V ±1.5% fixed output voltage accuracy over line, load, and VIN VOUT CIN COUT temperature 10µF 10µF SENSE Excellent power supply rejection ratio (PSRR) performance RPULL-UP ON 100kΩ EN 62 dB typical at 10 kHz at 2 A load PG PG OFF 46 dB typical at 100 kHz at 2 A load SS VADJ Excellent load/line transient response CSS VREG REFCAP RADJ 10nF C 10kΩ Soft start to reduce inrush current CREG GND REF 1µF 1µF Optimized for small 10 μF ceramic capacitors 12922-002 Current-limit and thermal overload protection Figure 2. Adjustable Output Operation Power-good indicator Table 1. Related Devices Precision enable Input Maximum Fixed/ 16-lead, 3 mm × 3 mm LFCSP package Device Voltage Current Adjustable Package AEC-Q100 qualified for automotive applications ADP1761 1.10 V to 1 A Fixed/adjustable 16-lead 1.98 -

Section 1 Point-Of-Load Power

Point-of-Load Power Practical Power Solutions 1. Point-of-Load Power 2. System Power Management and Portable Power 3. Power for Mixed Analog/Digital Systems 4. Hardware Design Techniques Copyright © 2009 By Analog Devices, Inc. All rights reserved. This book, or parts thereof, must not be reproduced in any form without permission of the copyright owner. SECTION 1 POINT-OF-LOAD POWER Fixed Power Point-of-Load Applications....................................................................1.1 Linear Regulators..........................................................................................................1.9 Switching Regulators and Controllers.....................................................................1.26 Powering FPGAs.........................................................................................................1.41 Powering DSPs.............................................................................................................1.51 ADIsimPower Design Tool...........................................................................................1.57 Technical References..............................................................................................1.68 1.0 Point-of-Load Power Fixed Power Point-of-Load Applications Today's system power requirements have become quite challenging, and design engineers must deal with multiple supply voltages, sequencing issues, high transient load currents, thermal considerations, and many others. In most cases, these problems must be addressed at the PC -

Full On-Chip CMOS Low-Dropout Voltage Regulator Robert J

IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS—I: REGULAR PAPERS, VOL. 54, NO. 9, SEPTEMBER 2007 1879 Full On-Chip CMOS Low-Dropout Voltage Regulator Robert J. Milliken, Jose Silva-Martínez, Senior Member, IEEE, and Edgar Sánchez-Sinencio, Fellow, IEEE Abstract—This paper proposes a solution to the present bulky external capacitor low-dropout (LDO) voltage regulators with an external capacitorless LDO architecture. The large external capac- itor used in typical LDOs is removed allowing for greater power system integration for system-on-chip (SoC) applications. A com- pensation scheme is presented that provides both a fast transient response and full range alternating current (ac) stability from 0- to 50-mA load current even if the output load is as high as 100 pF. The 2.8-V capacitorless LDO voltage regulator with a power supply of 3 V was fabricated in a commercial 0.35- m CMOS technology, consuming only 65 A of ground current with a dropout voltage of 200 mV. Experimental results demonstrate that the proposed ca- Fig. 1. External capacitorless LDO voltage regulator. pacitorless LDO architecture overcomes the typical load transient and ac stability issues encountered in previous architectures. Index Terms—Analog circuits, capacitorless low dropout (LDO), The conventional LDO voltage regulator, for stability require- dc–dc regulator, fast path, LDO voltage regulators, transient com- ments, requires a relatively large output capacitor in the single pensation. microfarad range. Large microfarad capacitors cannot be real- ized in current design technologies, thus each LDO regulator I. INTRODUCTION needs an external pin for a board mounted output capacitor. To overcome this issue, a capacitorless LDO has been proposed in NDUSTRY is pushing towards complete system-on-chip [2]; that topology is, however, unstable at low currents making (SoC) design solutions that include power management. -

Power Management Considerations for Fpgas and Asics

LM2734,LM2736,LM2742,LM2743,LM2744, LM5642 Power Management Considerations for FPGAs and ASICs Literature Number: SNVA586 POWER designer SM Expert tips, tricks, and techniques for powerful designs No. 102 Power Management Considerations for Feature article............1-7 FPGAs and ASICs 2 MHz synchronous — By David Baba, Staff Application Engineer buck controllers............2 Voltage Regulator 1A SOT-23 buck (termination) Voltage Regulator Core Voltage regulators........................4 (core) Voltage Regulator I/O Voltage FPGA or ASIC 4.5V-36V synchronous (I/O) Voltage Regulator Auxiliary Voltage buck controllers............6 (auxiliary) Power design tools........8 Figure 1: Typical FPGA or ASIC power management requirements n today’s hypercompetitive markets with increasing time-to-market pressures for electronic sub-systems, the importance of FPGAs and ASICs Ihas been elevated to the point that they frequently contain the critical functionality of the new system. One of the most critical factors in an FPGA system design is power management. To power an FPGA effectively, a detailed system overview is needed. These same techniques often apply to ASICs. Power supply requirements are important because of the complex initial conditions, transient behavior, turn-on, and turn-off specifications, among many others. Bypassing or decoupling the power supplies at the device (in the context of the device’s application) also requires careful attention. Figure 1 shows typical power management requirements for an FPGA. Usually a mini- mum of two voltages are needed to power FPGAs: one for the “core” (1.0V to 2.5V typ.) and one for the “I/Os” (3.3V typ.). Many FPGAs also require a third low-noise, low-ripple voltage to provide power to the auxiliary circuits. -

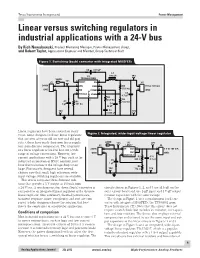

Linear Versus Switching Regulators in Industrial Applications with a 24-V

Texas Instruments Incorporated Power Management Linear versus switching regulators in industrial applications with a 24-V bus By Rich Nowakowski, Product Marketing Manager, Power Management Group, and Robert Taylor, Applications Engineer and Member, Group Technical Staff Figure 1. Switching (buck) converter with integrated MOSFETs C2 0.01 µF L1 U1 100 µH TP3 24VIN TPS54061DRB TP1 1 8 J1 BOOT PH J2 1 2 7 1 24VIN VIN GND R3 5 V at 100 mA 2 3 6 53.6 kΩ 2 GND EN COMP GND 4 5 C5 RT/CLK VSNS 4.7 µF PWPD R2 9 24.9 kΩ R4 C1 R1 10.2 kΩ 1 µF 301 kΩ C4 22 pF TP2 C3 TP4 0.022 µF Linear regulators have been around for many years. Some designers still use linear regulators Figure 2. Integrated, wide-input-voltage linear regulator that are over 20 years old for new and old proj- ects. Others have made their own linear regula- 24VIN TP5 U2 TP7 J3 LM317 J4 tors from discrete components. The simplicity 1 4 1 24VIN 3 IN OUT 5 V at 100 mA of a linear regulator is hard to beat for a wide 2 2 OUT 2 GND 1 GND range of voltage conversions. However, low- GND/ADJ current applications with a 24-V bus, such as for R5 C10 243 Ω 4.7 µF industrial automation or HVAC controls, may C6 1 µF have thermal issues if the voltage drop is too R6 large. Fortunately, designers have several TP6 732 Ω TP8 choices now that small, high-efficiency, wide- input-voltage switching regulators are available. -

Green Electronics: High Efficiency On-Chip Power Management

Green Electronics: High Efficiency On-chip Power Management Solutions for Portable and Battery-Powered Applications Dissertation Presented in Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in the Graduate School of The Ohio State University By Anqiao Hu, B.S., M.S. Graduate Program in Electrical and Computer Engineering The Ohio State University 2010 Dissertation Committee: Mohammed Ismail, Advisor Steven Bibyk Waleed Khalil Copyright by Anqiao Hu 2010 Abstract With increasing recognition of green house gas emission as a major contributor to global warming, and that fossil fuels are finite resources that would eventually dwin- dle, green electronics, a commitment toward designing more energy-efficient products, is not only an environmental, social, and ethical imperative for the integrated circuit research community, but also a shrewd business practice for industry. This dissertation discusses various mixed-signal VLSI techniques at system and circuit (transistor) levels that would help build energy-efficient green electronics, which are instrumental for current consumer applications and future sustainable renewable-energy economy. At system level, a truly effective power management scheme should be a holistic solution involving system software, VLSI architecture, and silicon IPs. Sleep-mode efficiency is pointed out as the bottleneck for low power battery-powered applications, and around 30% battery runtime extension is estimated based on published experimental data if sleep-mode efficient power management IPs are available and used in place. At circuit level, a number of linear regulator and switch-mode power converter designs are presented. A sleep-mode ready, current-area efficient capacitor-free low drop-out regulator with input current-differencing is designed, fabricated, and mea- sured in 0.5 µm CMOS process. -

Linear Regulators Selection Guide Ver.5.0 Linear Regulators Selection Guide

Linear Regulator Linear Regulators Selection Guide Ver.5.0 Linear Regulators Selection Guide INDEX Recommended Products P.02 Ultra-Small-size CMOS LDO Regulators P.02 High Voltage LDO Regulators P.03 Secondary LDO Regulators P.05 Hi-Fi Audio Power Supplies P.07 Single Output Linear Regulators P.08 All Product Selection P.08 Low Quiescent Current (IQ) Product Selection P.08 Small-size Product Selection P.09 High Accuracy Product Selection P.10 Low Saturation Selection P.10 AEC-Q100 qualified P.10 3-Terminal Linear Regulator Lineup P.11 LDO-type Linear Regulator Lineup P.13 LDO-type Linear Regulator Selection Charts P.19 Ultra-Low LDO-type Linear Regulators P.22 Multi-Output LDOs P.23 Termination Regulators for DDR SDRAM P.24 LDO+(plus) P.25 Guide to ROHM’s Website P.28 Package List P.29 Before using the ICs, please verify the numerical values, data, and functions listed in the latest datasheet. 01 Linear Regulators Selection Guide Recommended Products Ultra-Small-size CMOS LDO Regulators Single Output CMOS LDO Regulators In the rapidly expanding ADAS (Advanced Driver Assistance System) field, a growing number of cameras and sensor modules are being used to obtain information, 6.5V rated increasing the demand for greater miniaturization. ROHM developed the BUxxJA2 VIN BUxxJA2 (200mA) VOUT series to meet this need. These automotive-grade CMOS LDOs deliver 200mA output 1.7V to 6.0V 1.0V to 3.4V in a class-leading small package size. In addition, low current consumption and superior response make them ideal for a range of automotive applications, from ADAS to power supplies for vehicle instrument panels and onboard radar systems. -

Linear Voltage Regulator

Linear Voltage Regulator Introduction For most electronic equipment a DC power supply is preferred since, except for a start-up transient, the supply does not (ideally) introduce any fiduciary timing dependence. However by and large electrical power is generated and distributed with a sinusoidal waveform. Thus a power supply typically begins with a rectifier to convert a sinusoidal input, e.g., 60 Hz for most U.S. consumer electronics, to a half- or more usually a full-wave rectified waveform. The supply is almost always a voltage supply as a practical matter; it is easier and less lossy to maintain a voltage supply in a standby condition rather than a current supply, and to operate it under varying load. The unidirectional but varying rectified waveform is filtered in various ways to reduce the variation ( the 'ripple' voltage) to an acceptable level. Nevertheless for many purposes the filtered supply voltage ripple variation often is unacceptably large, particularly within practical filtering limitations. Power line variations, for example, are passed on to the rectified output. Moreover the Thevenin equivalent circuit for the rectified and filtered power supply often involves a substantial 'internal' resistance, so that the terminal voltage of the supply varies with the amount of current drawn because of the voltage drop across this internal resistance. A 'voltage regulator' inserts additional electronics between the unregulated supply terminals and the load primarily to reduce this terminal voltage variation, but also to provide additional benefits. Voltage rectification and filtering is discussed in a separate note. The objective of this note is to provide an introduction to voltage regulator operation.