Lecture-54 INTEL 8253: Programmable Interval Timer Intel

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Computers Shouldn't Be Limitations Advertising & Distribution a Handicap Is a Limitation

.. No. 48 July-August 1989 $3.95 T HE MICRO TECHN I CAL J 0 URN A L Tools For The Physically Impaired What's important to people who have handicaps? We asked them. (Their responses may surprise you.) The Adventure Begins page 8 Dallas Vordahl demonstrates what you can do with a computer, a mouthstick, and a very limited amount of head motion. Writing Software For page 16 The Blind Don' t exclude the blind from your next software package. File Transfer Via The page 20 Parallel Port The LIMBO Project page 28 Build a maze-running robot. And More ... Debugging A Processor page 44 Growing Your Own page 66 Software Business Great SOGs page 83 And Much, Much, More 07 a 7447019388 3 U[J!]£?[jj) J/@[J!]£? !fJ©llfU/5Ju O[jj)(]@ (j] /JJ@r:'.JQ£?fj[J!]O /LfI1@@£?(JJ(]@£?J/ (j][jj)@ @[jj)@]O[jj)QQ£?O[jj)@] (]@@ODDD Introducing ... The PC-LabCard Family Only from HSC Electronic Supply Digital 1/0 and Prototype Development IBM PC/XT/AT and it's Counter Card compatible models are moving into Card Industrial/Laboratory applications at • 32 Digital Input Channels • Large breadboard area (3290 holes) - TTL compatible an increasing rate. The reasons for • Independent memory and I/O address - Low loading: 0.2 rnA at O.4V input this include their price/performance decoders built-in • 32 Digital Output Channels ratio and short user learning curve. • Memory and I/O ports are jumper - TTL compatible PC-based data acquisition boards selectable - Driving capacity: Sink 24 rnA, are now taking the place of the • All bus signals are buffered, marked, source 15 rnA and ready for use • Intel 8253 Timer/Counter traditional data loggers or recorders - 3 channels of timer/counter which cost several times more. -

8253/8253·5 Programmable Interval Timer

TABLE OF CONTENTS HOW TO CONFIGURE YOUR SYSTEM SUPPORT 1 IN UNDER 5 MINUTES, WITHOUT READING THE MANUAL • • •• 5 Other options and jumpers ••••• 6 Important note about system memory 6 ABOUT SYSTEM SUPPORT 7 Technical overview • 7 CONFIGURING THE SYSTEM SUPPORT 1 9 Setting I/O address 9 Setting memory address •• 10 Other memory options • • • • • • • • • 11 Disabling the memory • • 11 Global/extended address selection 11 Phantom* response options •••• 12 Battery back-up for CMOS RAM • • 12 Wait states ••••••••••• 12 Using higher speed 9511A or 9512 • 13 Interrupt jumpers and options 13 Using a 9511 or 9512 with interrupts 15 Interval timer options • • • • • • • 15 Configuring the serial channel • • • • 16 Other miscellaneous hardware options 17 Connecting the battery • • • • 18 Mounting the battery holder 18 Replacing the battery • • • • • 18 I/O port map • • • • • • • • 19 PROGRAMMING CONSIDERATIONS FOR THE SYSTEM SUPPORT 1 20 Power-up initialization • • • • 20 Programming the serial channel 20 UART initialization • • • • • • • • • • 25 Sample UART program • • • • • 25 Programming the real time clock • • • • 26 Clock programming sequence • • • • 28 Sample clock program • • • • • • • • • • 29 Programming the interrupt controllers 35 Important note about using DDT to debug interrupts 35 "INTEL 8259A Programmable Interrupt Controller". 36 Initializing the 8259A • • • • • • • • • • • 56 Routine for initializing master/slave 8259As 56 Disabling the 8259As •••••••••••• 57 Programming the interval timer. • • • • • • •••• 58 "INTEL 8253/8253-5 -

15 Pecision System Clock Architecture

Pecision System Clock Architecture 15 Pecision System Clock Architecture “Time iz like money, the less we hav ov it teu spare the further we make it go.” Josh Billing Encyclopedia and Proverbial Philosophy of Wit and Humor, 1874 225 Pecision System Clock Architecture Limitations of the Art Over the almost three decades that NTP has evolved, accuracy expectations have improved from 100 ms to less than 1 ms on fast LANs with multiple segments interconnected by switches and less than a few milliseconds on most campus and corporate networks with multiple subnets interconnected by routers. Today the practical expectations with a GPS receiver, PPS signal and precision kernel support are a few microseconds. In principle the ultimate expectations are limited only by the 232-ps resolution of the NTP timestamp format or about the time light travels three inches. Improving accuracy expectations below the PPS regime is proving intricate and tricky. In this chapter we turn to the most ambitious means available to minimize errors in the face of hardware and software not designed for extraordinary timekeeping. First we examine the hardware and software components for a precision system clock and evolve an optimal design. Next we survey timestamping techniques using both hardware, driver and software methods to minimize errors due to media, device and operating system latencies. Finally, we explore the IEEE 1588 Precision Time Protocol (PTP), how it is used in a high speed LAN, and how it and NTP can sail in the same boat. The parting shots section proposes a hardware assisted design which provides performance equivalent to PTP with only minimal modifications to the Unix operating system kernel. -

143847-003.Pdf

iSBC® 88/25 SINGLE BOARD COMPUTER 8-Bit 8088 Microprocessor Operating at Programmable Synchronousl • 5 MHz • Asynchronous RS232C Compatible One Megabyte Addressing Range Serial Interface with Software • Selectable Baud Rates Two iSBXTM Bus Connectors • 24 Programmable Parallel I/O Lines Optional Numeric Data Processor with • • iSBC® 337 MUL TIMODULETM Processor Two Programmable 16-Bit BCD or • Binary Timers/Event Counters 4K Bytes of Static RAM; Expandable • On-Board to 16K Bytes 9 Levels of Vectored Interrupt Control, • Expandable to 65 Levels Sockets for up to 64K Bytes of JEDEC • 24/28-Pin Standard Memory Devices; • MUL TIBUS® Interface for Multimaster Expandable On-Board to 128K Bytes Configurations and System Expansion Development Support with Intel's iPDS, • Low Cost Personal Development System, and EMV-88 Emulator The iSBC 88/25 Single Board Computer is a member of Intel's complete line of OEM microcomputer systems which take full advantage of Intel's technology to provide economical, self-contained, computer-based solu tions for OEM applications. The iSBC 88/25 board is complete computer system on a single 6.75 x 12.00-in. printed circuit card. The CPU, system clock, read/write memory, nonvolatile read only memory, I/O ports and drivers, serial communications interface, priority interrupt logic and programmable timers, all reside on the board. The large control storage capacity makes the iSBC 88/25 board ideally suited for control-oriented applications such as process control, instrumentation, industrial automation and many others. 143847-1 September 1987 3-63 Order Number: 143847-003 infef iSBC® 88/25 FUNCTIONAL DESCRIPTION ASCII data, and iterative word and byte string manip ulation functions. -

Features: • 3 8-Bit IO Ports PA, PB, PC • PA Can Be Set for Modes 0, 1, 2

Features: · 3 8-bit IO ports PA, PB, PC · PA can be set for Modes 0, 1, 2. PB for 0,1 and PC for mode 0 and for BSR. Modes 1 and 2 are interrupt driven. · PC has 2 4-bit parts: PC upper (PCU) and PC lower (PCL), each can be set independently for I or O. Each PC bit can be set/reset individually in BSR mode. · PA and PCU are Group A (GA) and PB and PCL are Group B (GB) · Address/data bus must be externally demux'd. · TTL compatible. · Improved dc driving capability The 8255A is a programmable peripheral interface (PPI) device designed for use in Intel microcomputer systems. Its function is that of a general purposes I/O component to Interface peripheral equipment to the microcomputer system bush. The functional configuration of the 8255A is programmed by the systems software so that normally no external logic is necessary to interface peripheral devices or structures. ARCHITECTURE OF 8255 PPI: The port A lines are identified by symbols PA0-PA7 while the port C lines are identified as PC4-PC7 similarly. Group B contains an 8-bit port B, containing lines PB0- PB7 and a 4-bit port C with lower bits PC0-PC3. The port C upper and port C lower can be used in combination as an 8-bit port C. Both the port Cs is assigned the same address. Thus one may have either three 8-bit I/O ports or two 8-bit and two 4-bit I/O ports from 8255. -

A Structured Approach to Microcomputer System Design

Behavior Research Methods & Instrumentation 1976, Vol. 8 (2), 123-128 A structured approach to microcomputer system design KEN McKENZIE Intel Corporation. Santa Clara, California .95053 A simple "building block" philosophy for construction of high-performance microcomputer-based systems utilizing I/O functional definition and a structured implementation of MOS/LSI semiconductor devices. The wide acceptance of the microcomputer as a DEFINITION OF SYSTEM ARCHITECTURE practical tool for on-line computation and dedicated control applications has drastically altered the manner in The heart of any structured philosophy is the disci which today's design engineer approaches a new project. pline upon which the system is based. In a microcom The traditional circuit by circuit analysis is no longer puter system, this discipline is referred to as the system necessary or desirable. A total systems approach of bus. Basically, it is a group of interconnections that closely studying each I/O device and its interface in con carry the total information transfer from one device in junction with the desired performance level of the over the system to another. All system devices, central pro all system then, by selectingthe proper MaS/LSI devices cessing unit, memory. and I/O, intercommunicate over and writing the support software, produces an efficient, the system bus. modular design. In the 8080 microcomputer system (see Figure I), The purpose of this paper is to show how a building the system bus is broken down into three major groups: block approach to both hardware and software will Data bus is the bus upon which all data flows in effect system design, introduce the latest MaS/LSI de the system. -

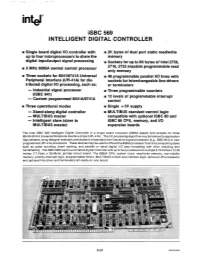

Isbc 569 INTELLIGENT DIGITAL CONTROLLER

iSBC 569 INTELLIGENT DIGITAL CONTROLLER • Single board digital 110 controller with • 2K bytes of dual port static. read/write up to four microprocessors to share the memory digital input/output signal processing • Sockets for up to 8K bytes of Intel 2758, 2716,2732 erasable programmable read • 3 MHz 8085A central control processor only memory • Three sockets for 8041/8741 A Universal • 48 programmable parallel I/O lines with Peripheral Interface (UPI·41A) for dis· sockets for interchangeable line drivers tributed digital I/O processing, such as: or terminators - Industrial signal processor • Three programmable counters (iSBC 941) • 12 levels of programmable interrupt - Custom programmed 8041A18741A control • Three operational modes • Single + 5V supply - Stand·along digital controller • MULTIBUS standard control logic - MULTIBUS master compatible with optional iSBC80 and . - Intelligent slave (slave to iSBC 86 CPU, memory, and I/O . MULTIBUS master) expansion. boards The Intel iSBC 569 Intelligent Digital Controller is a single board computer (8085A based) with sockets for three 8041A/8741A Universal Peripheral Interface chips (UPI-41A). The I/O processing algorithm may be·tailored to application requirements using designer selected combinations of standard Intel industrial signal processors (e.g., iSBC 941) or user programmed UPI-41A processors. These devices may be used to offload the 8085A processorfrom time consuming tasks such as pulse counting, event sensing, and parallel or serial digital 110 data formatting with error checking and handshaking. The iSBC 569 board is a complete digital controller with up to four processors on a single 6.75 inches x 12.00 inches (17.15cm x ·30.48cm) printed circuit board. -

EAGLE PC SERIES TECHNICAL NOTES ------/ 41({:R~

( !\ ,i; I~ '~ EAGLE PC SERIES TECHNICAL NOTES ------------------------------- / 41({:r~ PC-E PC-l PC-2 PC-XL ----- RAM 64KB l28KB l28KB l28KB FLOPPY DISKS 1 DiS 1 DiS 2 DIS 1 DIS 48 TPI 48 TPI 48 TPI 48 TPI HARD DISK NIA N/A NIA FILE - 10 MONITOR OPT. 12" 12" OPT. ..1j -+ c A'X.> 720X352 720X352 l AVAILABLE 3 EXPANSION SLOTS 2 1 1 0 SOFTWARE OPT. INCLD. INCLD. OPT. *' All are 8088 based systems @ 4.7 Mhz. * Available or standard expansion boards. 1. Floppy disk controller board. , 2. Video/Graphics board. N ll~r I-rMl~ ~ 3. SASI boarQ. (Std. in -XL mopel) • ;:::i7 ~ n L.E I '0 E-IC f t'lNS10N * RAM is expandable to 5l2Kb, in 64Kb increments. The RAM p.1!~vided is 65,536 words by l"";bit dynamic 'MOS'RAM. 1 * All systems corne with two serial ports and one parallel port. The parallel ports' major device is a 8255A and is centronics compatible. The serial ports are asynchronous only and use two 8250s'. SERIAL PORT PIN-OUTS Pin # Signal Name 2 TX Data 3 RX Data 4 RTS 5 CTS 6 DSR 7 GND. 8 Carrier Detect DTR ~.~cit> RI ~ -- ~~~- * The EPROMs are 2764s' and contain the boot ~ ChuT~ routine and diagnostics. ~ :2 J; f((D ~!\ 5 «£'ifC-N-- PIA 0 D I.,,) 151\ c.. fRo 'M. 2. III J111111111 III 1111" JIll IIIJ 111111 III II HI 11111111 I.:~(r I PIN 1. Eagle PC with a File 10/40 add-on . }-) J) l'DAO~ ( 3 Floppy disk drive strapping for a Teac FD-55B. -

Microprocessors: from Basic Chips to Complete Systems

- 237 - MICROPROCESSORS: FROM BASIC CHIPS TO COMPLETE SYSTEMS R. W. Dobinson,*) University of Illinois, Urbana, Illinois, USA. "Good-morning, good morning!", the General said When we met him last week on our way to the line. Now the soldiers he smiled at are most of them dead, And we're cursing his staff for Incompetent swine. "He's a cheery old card," grunted Harry to Jack As they slogged up to Arras with rifle and pack. * * * * But he did for them both by his plan of attack. Siegfried Sassoon April 1917 1. AIMS OF THESE LECTURES Microprocessor technology has, since its conception and birth in the early 1970's, entered very many areas of our lives. No end to its growth is in sight, and new uses appear almost daily. The semiconductor industry continues to produce ever more powerful integrated circuits (known far and wide as chips); more functionality and speed at lower cost is every salesman's cry. These lectures aim to present and explain in general terms some of the characteristics of microprocessor chips and associated components. They will show how systems are synthesized from the basic integrated circuit building blocks which are currently available; processor, memory, input-output (I/O) devices, etc. It is not my intention to discuss in detail the many different microprocessors now available on the market, nor will a complete catalogue of support chips be presented. Time will not permit this. Instead, emphasis will be placed on explaining the basic principles of different types of chip. As far as possible X will avoid talking too much about any specific devices; thus I will spend some time discussing a generic microprocessor accessing generic memory and talking to the outside world via generic I/O devices. -

Computer Interrupt a Signal Indicating That an Event Needing Immediate Attention Has Occurred

Computer Interrupt a signal indicating that an event needing immediate attention has occurred 2 Types of Interrupts: External - generated outside CPU by other hardware Internal - generated within CPU as a result of an instruction or operation - x86 has internal interrupts: int, into, Divide Error and Single Step - Trap generally means any processor generated interrupt - in x86, Trap usually means the Single Step interrupt x86 Interrupts: 1) Hardware Interrupt - External Uses INTR and NMI 2) Software Interrupt - Internal - from int or into 3) Processor Interrupt - Traps and 10 Software Interrupts (12 total) 8086/8088 Pinout Diagrams GND 1 40 VCC GND 1 40 VCC AD14 2 39 AD15 A14 2 39 A15 AD13 3 38 A16/S3 A13 3 38 A16/S3 AD12 4 37 A17/S4 A12 4 37 A17/S4 AD11 5 36 A18/S5 A11 5 36 A18/S5 AD10 6 35 A19/S6 A10 6 35 A19/S6 AD9 7 34 BHE/S7 A9 7 34 SS0 AD8 8 33 MN/MX A8 8 33 MN/MX AD7 9 8086 32 RD AD7 9 8088 32 RD AD6 10 31 HOLD AD6 10 31 HOLD AD5 11 30 HLDA AD5 11 30 HLDA AD4 12 29 WR AD4 12 29 WR AD3 13 28 M/IO AD3 13 28 IO/M AD2 14 27 DT/R AD2 14 27 DT/R AD1 15 26 DEN AD1 15 26 DEN AD0 16 25 ALE AD0 16 25 ALE NMI 17 24 INTA NMI 17 24 INTA INTR 18 23 TEST INTR 18 23 TEST CLK 19 22 READY CLK 19 22 READY GND 20 21 RESET GND 20 21 RESET 8086 8088 Pin ModePin Mode Minimum Maximum Minimum Maximum 31 HOLD RQ/GT0 31 HOLD RQ/GT0 30 HLDA RQ/GT1 30 HLDA RQ/GT1 29 WR LOCK 29 WR LOCK 28 M/IO S2 28 IO/M S2 27 DT/R S1 27 DT/R S1 26 DEN S0 26 DEN S0 25 ALE QS0 25 ALE QS0 24 INTA QS1 24 INTA QS1 34 SS0 High State *Minimum/Maximum Mode Refers to the Bus Handshaking -

3.5 TIMER PROGRAMMABLE INTERVAL TIMER (8253/8254) The

ROHINI COLLEGE OF ENGINEERING & TECHNOLOGY 3.5 TIMER PROGRAMMABLE INTERVAL TIMER (8253/8254) The Intel 8253 and 8254 are Programmable Interval Timers (PTIs) designed for microprocessors to perform timing and counting functions using three 16-bit registers. Each counter has 2 input pins, i.e. Clock & Gate, and 1 pin for “OUT” output. To operate a counter, a 16-bit count is loaded in its register. On command, it begins to decrement the count until it reaches 0, then it generates a pulse that can be used to interrupt the CPU. Difference between 8253 and 8254 825 825 3 4 Its operating frequency is 0 - 2.6 MHz Its operating frequency is 0 - 10 MHz It uses N-MOS technology It uses H-MOS technology Read-Back command is not available Read-Back command is available Reads and writes of the same counter Reads and writes of the same counter cannot be can be interleaved. interleaved. EC 8691 MICROPROCESSORS AND MICROCONTROLLERS ROHINI COLLEGE OF ENGINEERING & TECHNOLOGY Figure 3.5.1 Internal blocks of 8253 and pin diagram [Source: Advanced Microprocessors and Microcontrollers by A.K Ray & K.M. Bhurchandi] CS - Chip select .When it is low,enables the communication between CPU and 8253. WR-When it is low,the CPU output data in the form of mode information are loading counters. RD – When it is low,the CPU reads data. A0-A1: These pins are connected to address bus. These are used to select one of the three counters. D0-D7: These are tri-state bidirectional data bus used to interface 8253 to the system data bus. -

Isbc™ 86/12A Or (Psbc 86/12A *) SINGLE BOARD COMPUTER

iSBC™ 86/12A or (pSBC 86/12A *) SINGLE BOARD COMPUTER .8086 16-bit HMOS microprocessor II Two programmable 16-bit BCD or binary central processor unit timers/event counters • 32K bytes of dual-port read/write • 9 levels of vectored interrupt control, memory expandable on-board to 64K expandable to 65 levels bytes with on-board refresh • Sockets for up to 16K bytes of read only • Auxiliary power bus and power fail memory expandable on-board to 32K interrupt control logic for read/write bytes memory battery backup • System memory expandable to 1 mega • MULTIBUS® interface for multi master byte configurations and system expansion • 24 programmable parallel I/O lines with sockets for interchangeable line drivers • Compatible with iSBC 337 MULTI and terminators MODULE™ Numeric Data Processor • Programmable synchronous/asynchro • Compatible with iSBC 80 family single nous RS232C compatible serial board computers, memory, digital and interface with software selectable analog I/O, and peripheral controller baud rates boards The iSBC 86/12A Single Board Computer is a member of Intel's complete line of OEM microcomputer systems which take full advantage of Intel's LSI technology to provide economical self-contained computer based solutions for OEM applications. The iSBC 86/12A board is a complete computer system on a single 6.75 x 12.00-inch printed circuit card. The CPU, system clock, read/write memory, nonvolatile read only memory, I/O ports and drivers, serial communications interface, priority interrupt logic and programmable timers, all reside on the board. Full MULTIBUS interface logic is included to offer compatibility with the Intel OEM Microcomputer Systems family of Single Board Computers, expansion memory options, digital and analog 110 expansion boards and peripheral controllers.