Retrocomputing on an FPGA Reconstructing an 80’S-Era Home Computer with Programmable Logic

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

The Canon Cat After of Release Before Macintosh

LORI EMERSON & FINN BRUNTON THE CANON CAT PROCESSING ADVANCED WORK In the fall of 2014, Finn Brunton, an assistant professor at NYU, contacted Lori Emerson, Director of the Media Archaeology Lab (MAL) at the University of Colorado, Boulder, about a rare fi nd he came across on ebay: a Canon Cat, which billed itself in 1986 as an “advanced work processor.” The MAL wasn’t immediately able to purchase the machine; however, Brunton purchased the Canon Cat with the agreement that he’d experiment with the Canon Cat for six months or so, sell it to the MAL, and then he and Emerson would co-write a piece – now, this piece – on the obscure machine from an ever-more distant past. Here, we hope to give you a glimpse into what computing could have been and still could be. 353 [SHIFT]+[DOCUMENT] [SHIFT]+[DOCUMENT] Who will the user be? The shape that early personal Jef Raskin began to work on designing the Canon Cat after computing takes rests in part on this question, with he left Apple in 1982, two years before release of Macintosh. its implicit temporal paradox. The scenario, or persona, The Cat was then introduced to the public by Canon in 1987 or model, or instance of the user threads through the for $1495 – roughly $3100 in 2015. Although the Cat was production of the machine, from input devices and discontinued after only six months, around 20,000 units performance criteria to software, industrial design, and were sold during this time. The Canon Cat fascinates me marketing. -

Retrocomputing As Preservation and Remix

Retrocomputing as Preservation and Remix Yuri Takhteyev Quinn DuPont University of Toronto University of Toronto [email protected] [email protected] Abstract This paper looks at the world of retrocomputing, a constellation of largely non-professional practices involving old computing technology. Retrocomputing includes many activities that can be seen as constituting “preservation.” At the same time, it is often transformative, producing assemblages that “remix” fragments from the past with newer elements or joining together historic components that were never combined before. While such “remix” may seem to undermine preservation, it allows for fragments of computing history to be reintegrated into a living, ongoing practice, contributing to preservation in a broader sense. The seemingly unorganized nature of retrocomputing assemblages also provides space for alternative “situated knowledges” and histories of computing, which can sometimes be quite sophisticated. Recognizing such alternative epistemologies paves the way for alternative approaches to preservation. Keywords: retrocomputing, software preservation, remix Recovering #popsource In late March of 2012 Jordan Mechner received a shipment from his father, a box full of old floppies. Among them was a 3.5 inch disk labelled: “Prince of Persia / Source Code (Apple) / ©1989 Jordan Mechner (Original).” Mechner’s announcement of this find on his blog the next day took the world of nerds by storm.1 Prince of Persia, a game that Mechner single-handedly developed in the late 1980s, revolutionized computer games when it came out due to its surprisingly realistic representation of human movement. After being ported to DOS and Apple’s Mac OS in the early 1990s the game sold 2 million copies (Pham, 2001). -

A Look at SÉCAM III

Viewer License Agreement You Must Read This License Agreement Before Proceeding. This Scroll Wrap License is the Equivalent of a Shrink Wrap ⇒ Click License, A Non-Disclosure Agreement that Creates a “Cone of Silence”. By viewing this Document you Permanently Release All Rights that would allow you to restrict the Royalty Free Use by anyone implementing in Hardware, Software and/or other Methods in whole or in part what is Defined and Originates here in this Document. This Agreement particularly Enjoins the viewer from: Filing any Patents (À La Submarine?) on said Technology & Claims and/or the use of any Restrictive Instrument that prevents anyone from using said Technology & Claims Royalty Free and without any Restrictions. This also applies to registering any Trademarks including but not limited to those being marked with “™” that Originate within this Document. Trademarks and Intellectual Property that Originate here belong to the Author of this Document unless otherwise noted. Transferring said Technology and/or Claims defined here without this Agreement to another Entity for the purpose of but not limited to allowing that Entity to circumvent this Agreement is Forbidden and will NOT release the Entity or the Transfer-er from Liability. Failure to Comply with this Agreement is NOT an Option if access to this content is desired. This Document contains Technology & Claims that are a Trade Secret: Proprietary & Confidential and cannot be transferred to another Entity without that Entity agreeing to this “Non-Disclosure Cone of Silence” V.L.A. Wrapper. Combining Other Technology with said Technology and/or Claims by the Viewer is an acknowledgment that [s]he is automatically placing Other Technology under the Licenses listed below making this License Self-Enforcing under an agreement of Confidentiality protected by this Wrapper. -

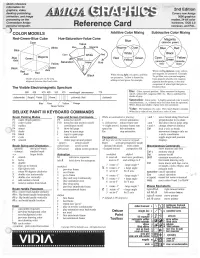

Amiga Graphics Reference Card 2Nd Edition

Quick reference information for graphics, video, 2nd Edition desktop publishing, Covers new Amiga animation, and image 3000 graphics processing on the modes, 24-bit color Commodore Amiga hardware, DOS 2.0 personal computer. Reference Card overscan, and PAL. ) COLOR MODELS Additive Color Mixing Subtractive Color Mixing Red-Green-Blue Cube Hue-Saturation-Value Cone Cyan Value White Blue Blue] Axis Yellow Black ~reen Axis When mixi'hgpigments, cyan, yellow, Red When mixing light, red, green, and blue and magenta are primaries. Example: are primaries. Yell ow is formed by To get blue, mix cyan and magenta. Shades of gray are on the long Cyan pigment absorbs red, magenta adding red and green, for example. diagonal between black and white. pigment absorbs green, so the only component of white light that gets re The Visible Electromagnetic Spectrum flected is blue. 380 420 470 495 535 575 wavelength (nanometers) 770 Hue: Color; spectral position. Often measured in degrees; red=0°, yellow=60°, magenta=300°, etc. Hue is undefined for shades of gray. (ultraviolet) Purple Violet yellowish Red (infrared) Saturation: Color purity. A highly-saturated color is nearly Blue Orange monochromatic, i.e., contains only one color from the spectrum. White, black, and shades of gray have zero saturation. Value: The darkness of a color. How much black it contain's. DELUXE PAINT Ill KEYBOARD COMMANDS White has a value of one, black has a value of zero. Brush Painting Modes Page and Screen Commands While an animation is playing: ; ana, move brush along fixed axis -

The Ultimate C64 Overview Michael Steil, 25Th Chaos Communication Congress 2008

The Ultimate C64 Overview Michael Steil, http://www.pagetable.com/ 25th Chaos Communication Congress 2008 Retrocomputing is cool as never before. People play Look and Feel C64 games in emulators and listen to SID music, but few people know much about the C64 architecture A C64 only needs to be connected to power and a TV and its limitations, and what programming was like set (or monitor) to be fully functional. When turned back then. This paper attempts to give a comprehen- on, it shows a blue-on-blue theme with a startup mes- sive overview of the Commodore 64, including its in- sage and drops into a BASIC interpreter derived from ternals and quirks, making the point that classic Microsoft BASIC. In order to load and save BASIC computer systems aren't all that hard to understand - programs or use third party software, the C64 re- and that programmers today should be more aware of quires mass storage - either a “datasette” cassette the art that programming once used to be. tape drive or a disk drive like the 5.25" Commodore 1541. Commodore History Unless the user really wanted to interact with the BA- SIC interpreter, he would typically only use the BA- Commodore Business Machines was founded in 1962 SIC instructions LOAD, LIST and RUN in order to by Jack Tramiel. The company specialized on elec- access mass storage. LOAD"$",8 followed by LIST tronic calculators, and in 1976, Commodore bought shows the directory of the disk in the drive, and the chip manufacturer MOS Technology and decided LOAD"filename",8 followed by RUN would load and to have Chuck Peddle from MOS evolve their KIM-1 start a program. -

300 Baud Issue 03

#3 Well, well, well! We actually did it and we find ourselves back for another issue. #"6% Its been hard going but it is now complete and in your hands. Once again thanks to everyone that made this possible, the writers in particular who gave up their time and creative efforts. And another thanks to the people who came out of the woodwork between issues to offer VCF-GB REPORT a hand in other ways. All going well we will march on forwards, towards issue four, but AN EXHIBITOR’S PERSPECTIVE honestly, we cant do it without you. Really. MARK WICKENS Going back a bit to last issue, it is worth throwing out a “Congratulations!!!” to Derek, who won the Atomic Robot competition. Well done Derek for walking to the post office and being randomly chosen! From my perspective receiving the post cards, it very was nice seeing stamps from different parts of the world. It seems I can pretty much geek out about anything. Thanks for sharing. Anyway back to this issue. As always we As the cat winks at me from a cushion on the sofa, and Stevie Wonder sings have some things of ‘everything is all right’ I start penning my thoughts on the first ‘official’ Vintage interest to the newbie Computer Festival in the UK, *ever*. Having never quite made it to VCF-E (the and to the hardcore geek. At one end of European VCF held in Munich every year in the Spring) and after my own DEC the spectrum, Gavin Legacy Event in aid of the National Museum of Computing, it seemed appropriate Picknell returns to to show up with my DEC gear at an event geared firmly towards the masses. -

IARU-R1 VHF Handbook

IARU-R1 VHF Handbook Vet Vers Version 9.01 March 2021 ion 8.12 IARU-R1 The content of this Handbook is the property of the International Amateur Radio Union, Region 1. Copying and publication of the content, or parts thereof, is allowed for non-commercial purposes provided the source of information is quoted. Contact information Website: http://www.iaru-r1.org/index.php/vhfuhsshf Newsletters: http://www.iaru- r1.org/index.php/documents/Documents/Newsletters/VHF-Newsletters/ Wiki http://iaruwiki.oevsv.at Contest robot http://iaru.oevsv.at/v_upld/prg_list.php VHF Handbook 9.00 1/180 IARU-R1 Oostende, 17 March 2021 Dear YL and OM, The Handbook consists of 5 PARTS who are covering all aspects of the VHF community: • PART 1: IARU-R1 VHF& up Organisation • PART 2: Bandplanning • PART 3: Contesting • PART 4: Technical and operational references • PART 5: archive This handbook is updated with the new VHF contest dates and rules and some typo’s in the rest of the handbook. Those changes are highlighted in yellow. The recommendations made during this Virtual General conference are highlighted in turquoise 73 de Jacques, ON4AVJ Secretary VHF+ committee (C5) IARU-R1 VHF Handbook 9.00 2/180 IARU-R1 CONTENT PART 1: IARU-1 VHF & UP ORGANISATION ORGANISATION 17 Constitution of the IARU Region 1 VHF/UHF/Microwaves Committee 17 In the Constitution: 17 In the Bye-laws: 17 Terms of reference of the IARU Region 1 VHF/UHF/Microwaves Committee 18 Tasks of IARU R-1 and its VHF/UHF/µWave Committee 19 Microwave managers Sub-committee 20 Coordinators of the VHF/UHF/Microwaves Committee 21 VHF Contest Coordinator 21 Satellite coordinator 21 Beacon coordinator 21 Propagations coordinators 21 Records coordinator 21 Repeater coordinator 21 IARU R-1 Executive Committee 21 Actual IARU-R1 VHF/UHF/SHF Chairman, Co-ordinators and co-workers 22 National VHF managers 23 Microwave managers 25 Note. -

Retromagazine 01 Eng.Pdf

Spring 2020: there’s a scent of change in the air SUMMARY <HIDDE N> Despite the frankly somewhat dark times we live in, this late spring brings many changes in our lives. Perhaps even finally a return to life as we know ◊ MISTER FPGA, one year later… Page 3 it, after the CoViD-19 nightmare. Even within our editorial initiative there ◊ Interview with Francesco Sblendorio Page 7 are no shortage of changes on the horizon. Indeed, many have already started or will soon be under way. ◊ FAST BASIC – a Locomotive Basic Page 14 compiler in CP/M Let's start with the name of your (hopefully) beloved magazine. From this issue the name of the magazine changes to RetroMagazine World. We ◊ Star Watcher Page 17 have been thrifty and modest: we have only added a small word ("World") ◊ Playing infinite lives with your C64 – Page 21 to our historical name, mostly in order to show our new intention to The challenge goes on address the entire international community and no longer only our numerous Italian readers. ◊ Retromath: Secret Codes Page 24 ◊ 3D Graphs with few lines in BASIC Page 27 How do we intend to do this? Well, actually, we already did it last May 2nd, with the release of issue zero of RetroMagazine English, a pilot publication ◊ Japan cronicles: A new Game & Watch? Page 32 entirely in English, dedicated to all the retrocomputing, retrogaming and retrocoding fans scattered all over the planet. These readers have long ◊ How I discovered RPG games on my Page 36 been asking us to bring in a "neutral" language (an official language, TI99/4A understandable to all) for the content and columns that for over two years ◊ KNIGHTMARE SAGA (MSX) Page 42 have been reaching Italian readers. -

Retrocomputer Magazine

Jurassic News Retrocomputing: Buon compleanno tre scuole di Spectrum! pensiero, un solo movimento C R La storia del BASIC A Y 1 Le mostre Torino: Steve Jobs 1955-2011 Bertiolo 2012 Apple Club: il miniBASIC Trento: Era domani Retrocomputer Magazine Anno 7 - Numero 41 - Maggio 2012 Collophon I dati editoriali della rivista Jurassic News Jurassic News Rivista aperiodica di Retrocomputer Jurassic News Coordinatore editoriale: Tullio Nicolussi [Tn] E’ una fanzine dedicata al retro- Redazione: computing nella più ampia accezione del [email protected] termine. Gli articoli trattano in generale dell’informatica a partire dai primi anni Hanno collaborato a questo numero: ‘80 e si spingono fino ...all’altro ieri. Besdelsec [Bs] Lorenzo [L2] La pubblicazione ha carattere Sonicher [Sn] puramente amatoriale e didattico, tutte Salvatore Macomer [Sm] Lorenzo Paolini [Lp] le informazioni sono tratte da materiale Giovanni [jb72] originale dell’epoca o raccolte su Internet. Antonio Tierno Cecilia Botta Normalmente il materiale originale, Moira Bertolini anche se “giurassico” in termini Felice Pescatore informatici, non è privo di restrizioni di Luca Papinutti utilizzo, pertanto non sempre è possibile Damiano Cavicchio Massimo Cellini riportare per intero articoli, foto, schemi, listati, etc…, che non siano esplicitamente Diffusione: liberi da diritti. La rivista viene diffusa in formato PDF via Internet agli utenti E’ possibile che parti del materiale registrati sul sito: pubblicato derivi da siti internet che non sono citati direttamente negli articoli. www.jurassicnews.com. Questo per la difficoltà di attribuzione del Contatti: materiale alla fonte originale; eventuali [email protected] segnalazioni e relative notifiche sono benvenute. Copyright: I marchi citati sono di copyrights La redazione e gli autori degli dei rispettivi proprietari. -

BOULDER DASH CONSTRUCTION KIT Disk Into the Disk Drive, Label Side Up, and Type LOAD" *",8,1 and Press RETURN

Game Designed by First Star Software, Inc, The name's Rockford.™ And diamonds It ain't always easy. You spend half are my game. your life in the diamonds and half your life out of 'em. £ LOTS OF 6 MUMMIES *nKFY So I decided to do some research. Looks like I came to the right place. And I started at the Cairo Museum of Check out these glass cases! Diamond History... Sure they turn into diamonds - but these critters can turn you into mine And f/7/s slimy stuff can multiply into a dust too! fortune-or a fiasco... Woah...Now we're talking diamonds... It appears you have an interest in I'll just jot this down and hop on the diamonds young man... next plane to fame and fortune. ...most young miners do. Thinkin' ... Every successful - and not-so-suc they can get rich quick and the like. cessful - miner has read the ancient Well sometimes you can, but you have miner's handbook. It tells you how you to do your homework. can make it to the top - but read the fine print... ...For instance there is the curse you know - the curse of poor planning, ...Yeah....uhuh...sure...I'm giving that poor concentration, poor minin1 skills. some thought... All will bring overly anxious young miners to the poor house. Are you thinking about that? OBJECTIVE You have two objectives in BOULDER DASH "CONSTRUCTION KIT1? You can either play the pre-saved game provided on the program disk, or construct your own games with the construction kit. -

Fourier Theory & Practice, Part II: Practice

Fourier Theory & Practice, Part II: Practice Operating the HP 54600 Series Scope with Measurement/Storage Module By: Robert Witte Hewlett-Packard Co. Practice Adding the Measurement/ Storage module to the scope adds additional waveform math capability, including FFT. These functions appear in the softkey menu under the ± (math) key. There are two math functions available, F1 and F2. The FFT function is available on Function F2. Function F2 can use function F1 as an operand, allowing an FFT to be performed on the result of F1. By setting function F1 to Channel 1 - Channel 2, and setting F2 to the FFT of F1, the FFT of a differential measurement can be obtained. The Measure- ment/Storage Module operating manual provides a more detailed discussion of these math functions. The scope can display the time domain waveform and the frequency domain spectrum simultaneously or individually. Normally, the sample points are not connected. For best frequency domain display, the sample points should be connected with lines (vectors). This can be accomplished by turning off all (time domain) channels and turning on only the FFT function. Alternatively, the Vectors On/Off softkey (on the Display menu) can be turned On and the STOP key pressed. Either of these actions allow the frequency domain samples to be connected by vectors which causes the display to appear more like a spectrum analyzer. The vertical axis of the FFT display is logarithmic, displayed in dBV (decibels relative to 1 Volt RMS). dB V = 20 log (VRMS) Thus, a 1 Volt RMS sinewave (2.8 Volts peak-to-peak) will read 0 dBV on the FFT display. -

NTSC Specifications

NTSC Modulation Standard ━━━━━━━━━━━━━━━━━━━━━━━━ The Impressionistic Era of TV. It©s Never The Same Color! The first analog Color TV system realized which is backward compatible with the existing B & W signal. To combine a Chroma signal with the existing Luma(Y)signal a quadrature sub-carrier Chroma signal is used. On the Cartesian grid the x & y axes are defined with B−Y & R−Y respectively. When transmitted along with the Luma(Y) G−Y signal can be recovered from the B−Y & R−Y signals. Matrixing ━━━━━━━━━ Let: R = Red \ G = Green Each range from 0 to 1. B = Blue / Y = Matrixed B & W Luma sub-channel. U = Matrixed Blue Chroma sub-channel. U #2900FC 249.76° −U #D3FC00 69.76° V = Matrixed Red Chroma sub-channel. V #FF0056 339.76° −V #00FFA9 159.76° W = Matrixed Green Chroma sub-channel. W #1BFA00 113.52° −W #DF00FA 293.52° HSV HSV Enhanced channels: Hue Hue I = Matrixed Skin Chroma sub-channel. I #FC6600 24.29° −I #0096FC 204.29° Q = Matrixed Purple Chroma sub-channel. Q #8900FE 272.36° −Q #75FE00 92.36° We have: Y = 0.299 × R + 0.587 × G + 0.114 × B B − Y = −0.299 × R − 0.587 × G + 0.886 × B R − Y = 0.701 × R − 0.587 × G − 0.114 × B G − Y = −0.299 × R + 0.413 × G − 0.114 × B = −0.194208 × (B − Y) −0.509370 × (R − Y) (−0.1942078377, −0.5093696834) Encode: If: U[x] = 0.492111 × ( B − Y ) × 0° ┐ Quadrature (0.4921110411) V[y] = 0.877283 × ( R − Y ) × 90° ┘ Sub-Carrier (0.8772832199) Then: W = 1.424415 × ( G − Y ) @ 235.796° Chroma Vector = √ U² + V² Chroma Hue θ = aTan2(V,U) [Radians] If θ < 0 then add 2π.[360°] Decode: SyncDet U: B − Y = -┼- @ 0.000° ÷ 0.492111 V: R − Y = -┼- @ 90.000° ÷ 0.877283 W: G − Y = -┼- @ 235.796° ÷ 1.424415 (1.4244145537, 235.79647610°) or G − Y = −0.394642 × (B − Y) − 0.580622 × (R − Y) (−0.3946423068, −0.5806217020) These scaling factors are for the quadrature Chroma signal before the 0.492111 & 0.877283 unscaling factors are applied to the B−Y & R−Y axes respectively.