GHDL Documentation Release 1.0-Dev

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Digital Systems Modeling Chapter 2 VHDL-Based Design

Digital Systems Modeling Chapter 2 VHDL-Based Design Alain Vachoux Microelectronic Systems Laboratory [email protected] Digital Systems Modeling Chapter 2: VHDL-Based Design Chapter 2: Table of contents ♦ VHDL overview ♦ Synthesis with VHDL ♦ Test bench models & verification techniques A. Vachoux, 2004-2005 Digital Systems Modeling Chapter 2: VHDL-Based Design - 2 A. Vachoux 2004-2005 2-2 Digital Systems Modeling Chapter 2: VHDL-Based Design VHDL highlights (1/2) ♦ Hardware description language • Digital hardware systems • Modeling, simulation, synthesis, documentation • IEEE standard 1076 (1987, 1993, 2002) ♦ Originally created for simulation • IEEE standards 1164 (STD_LOGIC) and 1076.4 (VITAL) ♦ Further adapted to synthesis • Language subset • IEEE standards 1076.3 (packages) and 1076.6 (RTL semantics) A. Vachoux, 2004-2005 Digital Systems Modeling Chapter 2: VHDL-Based Design - 3 A. Vachoux 2004-2005 2-3 Digital Systems Modeling Chapter 2: VHDL-Based Design VHDL highlights (2/2) ♦ Application domain (abstraction levels): Functional -> logic ♦ Modularity • 5 design entities: entity, architecture, package declaration and body, configuration • Separation of interface from implementation • Separate compilation ♦ Strong typing • Every object has a type • Type compatibility checked at compile time ♦ Extensibility: User-defined types ♦ Model of time • Discrete time, integer multiple of some MRT (Minimum Resolvable Time) ♦ Event-driven simulation semantics A. Vachoux, 2004-2005 Digital Systems Modeling Chapter 2: VHDL-Based Design - 4 A. Vachoux 2004-2005 2-4 Digital Systems Modeling Chapter 2: VHDL-Based Design VHDL-based design flow Editor (text or graphic) Test bench models VHDL packages RTL model Logic simulation Logic/RTL Constraints synthesis (area, timing, power) VHDL VITAL standard cell Gate-level modeld netlist Standard cell library SDF file Place & route Delay Layout extraction A. -

Xilinx Synthesis and Verification Design Guide

Synthesis and Simulation Design Guide 8.1i R R Xilinx is disclosing this Document and Intellectual Property (hereinafter “the Design”) to you for use in the development of designs to operate on, or interface with Xilinx FPGAs. Except as stated herein, none of the Design may be copied, reproduced, distributed, republished, downloaded, displayed, posted, or transmitted in any form or by any means including, but not limited to, electronic, mechanical, photocopying, recording, or otherwise, without the prior written consent of Xilinx. Any unauthorized use of the Design may violate copyright laws, trademark laws, the laws of privacy and publicity, and communications regulations and statutes. Xilinx does not assume any liability arising out of the application or use of the Design; nor does Xilinx convey any license under its patents, copyrights, or any rights of others. You are responsible for obtaining any rights you may require for your use or implementation of the Design. Xilinx reserves the right to make changes, at any time, to the Design as deemed desirable in the sole discretion of Xilinx. Xilinx assumes no obligation to correct any errors contained herein or to advise you of any correction if such be made. Xilinx will not assume any liability for the accuracy or correctness of any engineering or technical support or assistance provided to you in connection with the Design. THE DESIGN IS PROVIDED “AS IS” WITH ALL FAULTS, AND THE ENTIRE RISK AS TO ITS FUNCTION AND IMPLEMENTATION IS WITH YOU. YOU ACKNOWLEDGE AND AGREE THAT YOU HAVE NOT RELIED ON ANY ORAL OR WRITTEN INFORMATION OR ADVICE, WHETHER GIVEN BY XILINX, OR ITS AGENTS OR EMPLOYEES. -

Publication Title 1-1962

publication_title print_identifier online_identifier publisher_name date_monograph_published_print 1-1962 - AIEE General Principles Upon Which Temperature 978-1-5044-0149-4 IEEE 1962 Limits Are Based in the rating of Electric Equipment 1-1969 - IEEE General Priniciples for Temperature Limits in the 978-1-5044-0150-0 IEEE 1968 Rating of Electric Equipment 1-1986 - IEEE Standard General Principles for Temperature Limits in the Rating of Electric Equipment and for the 978-0-7381-2985-3 IEEE 1986 Evaluation of Electrical Insulation 1-2000 - IEEE Recommended Practice - General Principles for Temperature Limits in the Rating of Electrical Equipment and 978-0-7381-2717-0 IEEE 2001 for the Evaluation of Electrical Insulation 100-2000 - The Authoritative Dictionary of IEEE Standards 978-0-7381-2601-2 IEEE 2000 Terms, Seventh Edition 1000-1987 - An American National Standard IEEE Standard for 0-7381-4593-9 IEEE 1988 Mechanical Core Specifications for Microcomputers 1000-1987 - IEEE Standard for an 8-Bit Backplane Interface: 978-0-7381-2756-9 IEEE 1988 STEbus 1001-1988 - IEEE Guide for Interfacing Dispersed Storage and 0-7381-4134-8 IEEE 1989 Generation Facilities With Electric Utility Systems 1002-1987 - IEEE Standard Taxonomy for Software Engineering 0-7381-0399-3 IEEE 1987 Standards 1003.0-1995 - Guide to the POSIX(R) Open System 978-0-7381-3138-2 IEEE 1994 Environment (OSE) 1003.1, 2004 Edition - IEEE Standard for Information Technology - Portable Operating System Interface (POSIX(R)) - 978-0-7381-4040-7 IEEE 2004 Base Definitions 1003.1, 2013 -

Designcon 2004 VHDL-200X and the Future of VHDL

DesignCon 2004 VHDL-200X and the Future of VHDL Jim Lewis, SynthWorks [email protected] Stephen Bailey, Mentor Graphic’s Model Technology Group Erich Marschner, Cadence Design Systems J. Bhasker, eSilicon Corp. Peter Ashenden, Ashenden Designs Pty. Ltd. Abstract VHDL is a critical language for RTL design and is a major component of the $200+ million RTL simulation market1. Many users prefer to use VHDL for RTL design as the language continues to provide desired characteristics in design safety, flexibility and maintainability. While VHDL has provided significant value for digital designers since 1987, it has had only one significant language revision in 1993. It has taken many years for design state-of-practice to catch-up to and, in some cases, surpass the capabilities that have been available in VHDL for over 15 years. Last year, the VHDL Analysis and Standardization Group (VASG), which is responsible for the VHDL standard, received clear indication from the VHDL community that it was now time to look at enhancing VHDL. In response to the user community, VASG initiated the VHDL-200x project2. VHDL-200x will result in at least two revisions of the VHDL standard. The first revision is planned to be completed next year (2004) and will include a C language interface (VHPI); a collection of high user value enhancements to improve designer productivity and modeling capability and potential inclusion of assertion-based verification and testbench modeling enhancements. A second revision is planned to follow about two years later. This paper summarizes VHDL-200X enhancements proposed for the first revision of VHDL. -

Openbsd Gaming Resource

OPENBSD GAMING RESOURCE A continually updated resource for playing video games on OpenBSD. Mr. Satterly Updated August 7, 2021 P11U17A3B8 III Title: OpenBSD Gaming Resource Author: Mr. Satterly Publisher: Mr. Satterly Date: Updated August 7, 2021 Copyright: Creative Commons Zero 1.0 Universal Email: [email protected] Website: https://MrSatterly.com/ Contents 1 Introduction1 2 Ways to play the games2 2.1 Base system........................ 2 2.2 Ports/Editors........................ 3 2.3 Ports/Emulators...................... 3 Arcade emulation..................... 4 Computer emulation................... 4 Game console emulation................. 4 Operating system emulation .............. 7 2.4 Ports/Games........................ 8 Game engines....................... 8 Interactive fiction..................... 9 2.5 Ports/Math......................... 10 2.6 Ports/Net.......................... 10 2.7 Ports/Shells ........................ 12 2.8 Ports/WWW ........................ 12 3 Notable games 14 3.1 Free games ........................ 14 A-I.............................. 14 J-R.............................. 22 S-Z.............................. 26 3.2 Non-free games...................... 31 4 Getting the games 33 4.1 Games............................ 33 5 Former ways to play games 37 6 What next? 38 Appendices 39 A Clones, models, and variants 39 Index 51 IV 1 Introduction I use this document to help organize my thoughts, files, and links on how to play games on OpenBSD. It helps me to remember what I have gone through while finding new games. The biggest reason to read or at least skim this document is because how can you search for something you do not know exists? I will show you ways to play games, what free and non-free games are available, and give links to help you get started on downloading them. -

Introduction

Introduction © Sudhakar Yalamanchili, Georgia Institute of Technology, 2006 (1) VHDL • What is VHDL? V H I S C Æ Very High Speed Integrated Circuit Hardware Description IEEE Standard 1076-1993 Language (2) 1 History of VHDL • Designed by IBM, Texas Instruments, and Intermetrics as part of the DoD funded VHSIC program • Standardized by the IEEE in 1987: IEEE 1076-1987 • Enhanced version of the language defined in 1993: IEEE 1076-1993 • Additional standardized packages provide definitions of data types and expressions of timing data – IEEE 1164 (data types) – IEEE 1076.3 (numeric) – IEEE 1076.4 (timing) (3) Traditional vs. Hardware Description Languages • Procedural programming languages provide the how or recipes – for computation – for data manipulation – for execution on a specific hardware model • Hardware description languages describe a system – Systems can be described from many different points of view • Behavior: what does it do? • Structure: what is it composed of? • Functional properties: how do I interface to it? • Physical properties: how fast is it? (4) 2 Usage • Descriptions can be at different levels of abstraction – Switch level: model switching behavior of transistors – Register transfer level: model combinational and sequential logic components – Instruction set architecture level: functional behavior of a microprocessor • Descriptions can used for – Simulation • Verification, performance evaluation – Synthesis • First step in hardware design (5) Why do we Describe Systems? • Design Specification – unambiguous definition -

DVD-Libre 2005-04 Y 2 Pr W W Pr B - 3 T T T T S De Ca SI 5 Sc Re Ra Q 1 Po 3 Ph I Sa Dic Dic 2 4 W Ex ( H N C T

(continuación) - CDCheck 3.1.4.0 - CDex 1.51 - Celestia 1.3.2 - Centarsia 1.3 - Chain Reaction - Check4me 2.03 - Checky 2.5 - Chomp 1.4.5 - ClamWin 0.83 - Clan Bomber 1.05 - Cobian Backup 6.1.1.264 - Cobian Internet Tools 1.0.0.10 - ColorCop 5.3 - ColorWiz 1.0 - Combinaisons Junior Plus 2.70 - Continental 2.1 - Crack Attack! 1.1.08 - Crimson Editor 3.70 - CubeTest 0.9.3 - DBDesigner 4.0.5.6 - DeepBurner 1.3.6.168 - Deslizzzp 3.3 - Dev-C++ 4.9.9.2 - Dia Win32 0.94 - DirGraph 2.0 - DVD-Libre Disk Imager 1.4 - Domino Puzzle 0.1a - DominOSA 1.71 - DomiSol 1.2 - Doxygen 1.4.1 - Dragonboard 0.8c - Drawing for children 2.0 - DVD Identifier 3.6.2 - e-Counter 3.1.2004 - EasyISO 1.3 - EasyPHP cdlibre.org 1.8 - Eclipse 3.0.1 - Eclipse Language Pack 3.0.x - Eclipse Modeling Framework 2.0.1 - Eclipse Visual Editor 1.0.2 - Emilia Pinball 0.30c - Enigma 0.81 - EQTabla 4.0.050208 - Eraser 5.7 - Everest 2005-04 Dictionary 3.10 beta - Everest Dictionary 3.10 beta Completo - Exact Audio Copy 0.95 prebeta 5 - Exodus 0.9.0.0 - Fall - FileMenu Tools 4.1 - FileZilla 2.2.12a - Find Favorites 1.11 - Firebird 1.5.2 - Flexible Renamer 7.3 - FloboPuyo 0.20 - FolderQuote 1.0 - foobar2000 0.8.3 - FooBilliard 3.0 - Foxit PDF Reader 1.2.0.115 - FractalExplorer 2.02 - FractalForge 2.8.2 - FrameFun 1.0.5.0 - Free Download DVD-Libre es una recopilación de programas para Windows: Manager 1.5.256 - Free Pascal 1.0.10 - FreeCiv 1.14.2 - FreeMind 0.7.1 - Frozen Bubble Enhanced ● libres / gratuitos al menos para uso personal o educativo 1.0 - Gaim 1.1.4 - GanttProject 1.10.3 -

Walnut Creek CDROM Spring 1995 Catalog 1-800-786-9907 • 1-510-674-0821 Fax the Best of Walnut Creek CDROM Is Yours Free*

Walnut Creek CDROM Spring 1995 Catalog 1-800-786-9907 • 1-510-674-0821 Fax The Best of Walnut Creek CDROM is yours Free*. The • You’ll also get fonts, fractals, Best of Walnut Creek CDROM music, clipart, and more. 600 lets you explore in-depth what MegaBytes in total! Walnut Creek CDROM has to offer. • Boot images from our Unix for PC discs so you will With samples from all of our know if your hardware will products, you’ll be able to see boot Slackware Linux or what our CDROM’s will do for FreeBSD you, before you buy. This CDROM contains: • The Walnut Creek CDROM digital catalog - photos and • Index listings of all the descriptions of our all titles programs, photos, and files on all Walnut Creek CDROM If you act now, we’ll include titles $5.00 good toward the purchase of all Walnut Creek CDROM • The best from each disc titles. If you’re only going to including Hobbes OS/2, own one CDROM, this should CICA MS Windows, Simtel be it! March, 1995. MSDOS, Giga Games, Internet Info, Teacher 2000, Call, write, fax, or email your Ultra Mac-Games and Ultra order to us today! Mac-Utilities * The disc is without cost, but the regular shipping charge still applies. • You get applications, games, utilities, photos, gifs, documents, ray-tracings, and animations 2 CALL NOW! 1-800-786-9907 Phone: +1-510-674-0783 • Fax: +1-510-674-0821 • Email: [email protected] • WWW: http://WWW.cdrom.com/ (Alphabetical Index on page 39.) Hi, Sampler - (Best of Walnut Creek) 2 This is Jack and I’ve got another great batch of CICA for Windows 4 Music Workshop 5 CDROM’s for you. -

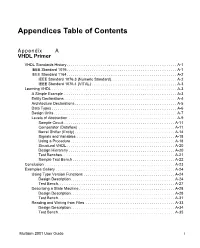

Appendices Table of Contents

Appendices Table of Contents Appendix A VHDL Primer VHDL Standards History. A-1 IEEE Standard 1076. A-1 IEEE Standard 1164. A-2 IEEE Standard 1076.3 (Numeric Standard). A-2 IEEE Standard 1076.4 (VITAL) . A-3 Learning VHDL . A-3 A Simple Example . A-3 Entity Declarations . A-4 Architecture Declarations . A-5 Data Types. A-6 Design Units . A-7 Levels of Abstraction . A-9 Sample Circuit . A-11 Comparator (Dataflow) . A-11 Barrel Shifter (Entity) . A-14 Signals and Variables . A-18 Using a Procedure . A-18 Structural VHDL. A-20 Design Hierarchy . A-20 Test Benches. A-21 Sample Test Bench . A-22 Conclusion . A-23 Examples Gallery . A-24 Using Type Version Functions . A-24 Design Description. A-24 Test Bench. A-27 Describing a State Machine . A-28 Design Description. A-28 Test Bench. A-31 Reading and Writing from Files . A-33 Design Description. A-34 Test Bench. A-35 Multisim 2001 User Guide i Appendix B.1 Verilog Primer Introduction . .B.1-1 What is Verilog? . B.1-2 What is VeriWell? . B.1-2 Why Use Verilog HDL? . B.1-3 The Verilog Language . .B.1-4 A First Verilog Program . B.1-4 Lexical Conventions . B.1-6 Program Structure . B.1-7 Data Types. B.1-10 Physical Data Types . .B.1-10 Abstract Data Types . .B.1-11 Operators . B.1-12 Binary Arithmetic Operators. .B.1-12 Unary Arithmetic Operators . .B.1-12 Relational Operators . .B.1-12 Logical Operators . .B.1-12 Bitwise Operators . .B.1-13 Unary Reduction Operators . -

High-Level Synthesis of Control and Memory Intensive Applications

High-Level Synthesis of Control and Memory Intensive Applications Peeter Ellervee Stockholm 2000 Thesis submitted to the Royal Institute of Technology in partial fulfillment of the requirements for the degree of Doctor of Technology Ellervee, Peeter High-Level Synthesis of Control and Memory Intensive Applications ISRN KTH/ESD/AVH--2000/1--SE ISSN 1104-8697 TRITA-ESD-2000-01 Copyright © 2000 by Peeter Ellervee Royal Institute of Technology Department of Electronics Electronic System Design Laboratory Electrum 229, Isafjordsgatan 22-26 S-164 40 Kista, Sweden URL: http://www.ele.kth.se/ESD Abstract Recent developments in microelectronic technology and CAD technology allow production of larger and larger integrated circuits in shorter and shorter design times. At the same time, the abstraction level of specifications is getting higher both to cover the increased complexity of systems more efficiently and to make the design process less error prone. Although High-Level Synthesis (HLS) has been successfully used in many cases, it is still not as indispensable today as layout or logic synthesis. Various application specific synthesis strategies have been devel- oped to cope with the problems of general HLS strategies. In this thesis solutions for the following sub-tasks of HLS, targeting control and memory inten- sive applications (CMIST) are presented. An internal representation is an important element of design methodologies and synthesis tools. IRSYD (Internal Representation for System Description) has been developed to meet various requirements for internal representations. It is specifically targeted towards representation of heterogeneous systems with multiple front-end languages and to facilitate the integration of several design and validation tools. -

FUEGO – an Open-Source Framework for Board Games and Go Engine Based on Monte-Carlo Tree Search

FUEGO – An Open-source Framework for Board Games and Go Engine Based on Monte-Carlo Tree Search Markus Enzenberger, Martin Muller,¨ Broderick Arneson and Richard Segal Abstract—FUEGO is both an open-source software frame- available source code such as Hoffmann’s FF [20] have had work and a state of the art program that plays the game of a similarly massive impact, and have enabled much followup Go. The framework supports developing game engines for full- research. information two-player board games, and is used successfully in UEGO a substantial number of projects. The FUEGO Go program be- F contains a game-independent, state of the art came the first program to win a game against a top professional implementation of MCTS with many standard enhancements. player in 9×9 Go. It has won a number of strong tournaments It implements a coherent design, consistent with software against other programs, and is competitive for 19 × 19 as well. engineering best practices. Advanced features include a lock- This paper gives an overview of the development and free shared memory architecture, and a flexible and general current state of the FUEGO project. It describes the reusable components of the software framework and specific algorithms plug-in architecture for adding domain-specific knowledge in used in the Go engine. the game tree. The FUEGO framework has been proven in applications to Go, Hex, Havannah and Amazons. I. INTRODUCTION The main innovation of the overall FUEGO framework may lie not in the novelty of any of its specific methods and Research in computing science is driven by the interplay algorithms, but in the fact that for the first time, a state of of theory and practice. -

High-Speed Data Acquisition and Optimal Filtering Based on Programmable Logic for Single-Photoelectron (SPE) Measurement Setup

High-speed data acquisition and optimal filtering based on programmable logic for single-photoelectron (SPE) measurement setup Experiment #7 Herman P. Lima Jr (CBPF), Rafael Nobrega (UFJF) [email protected], [email protected] Challenge library ieee; use ieee.std_logic_1164.all; entity logica is port (A,B,C : in std_logic; D,E,F : in std_logic; SAIDA : out std_logic); end logica; architecture v_1 of logica is begin SAIDA <= (A and B) or (C and D) or (E and F); end v_1; Herman Lima Jr References • Fundamentals of Digital Logic with VHDL Design, Stephen Brown, Zvonko Vranesic, McGraw-Hill, 2000. • The Designer’s Guide to VHDL, Peter Ashenden, 2nd Edition, Morgan Kaufmann, 2002. • VHDL Coding Styles and Methodologies, Ben Cohen, 2nd Edition, Kluwer Academic Publishers, 1999. • Digital Systems Design with VHDL and Synthesis: An Integrated Approach, K. C. Chang, Wiley-IEEE Computer Society Press, 1999. • Application-Specific Integrated Circuits, Michael Smith, Addison-Wesley, 1997. • www.altera.com (datasheets, application notes, reference designs) • www.xilinx.com (datasheets, application notes, reference designs) • www.doulos.com/knowhow/vhdl_designers_guide (The Designer’s Guide to VHDL) • www.acc-eda.com/vhdlref/index.html (VHDL Language Guide) • www.vhdl.org Herman Lima Jr Background required Digital Electronics: logic gates flip-flops multiplexers comparators counters ... Herman Lima Jr Agenda Digital electronics: evolution, current technologies Programmable Logic Introduction to VHDL (for synthesis) Herman Lima Jr Digital Electronics: