Intel® Server Board S3420GP

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

SAMPLE CHAPTER 1 Chapter Personal Computer 1 System Components the FOLLOWING COMPTIA A+ ESSENTIALS EXAM OBJECTIVES ARE COVERED in THIS CHAPTER

SAMPLE CHAPTER 1 Chapter Personal Computer 1 System Components THE FOLLOWING COMPTIA A+ ESSENTIALS EXAM OBJECTIVES ARE COVERED IN THIS CHAPTER: Ûß1.2 Explain motherboard components, types and features Nß Form Factor Nß ATX / BTX, Nß micro ATX Nß NLX Nß I/O interfaces Material Nß Sound Nß Video Nß USB 1.1 and 2.0 Nß Serial Nß IEEE 1394 / FireWire Nß Parallel Nß NIC Nß Modem Nß PS/2 Nß Memory slots Nß RIMM Nß DIMM Nß SODIMM CopyrightedNß SIMM Nß Processor sockets Nß Bus architecture 86498book.indb 1 7/22/09 5:37:17 AM Nß Bus slots Nß PCI Nß AGP Nß PCIe Nß AMR Nß CNR Nß PCMCIA Chipsets Nß BIOS / CMOS / Firmware Nß POST Nß CMOS battery Nß Riser card / daughterboard Nß [Additional subobjectives covered in chapter 2] Ûß1.4 Explain the purpose and characteristics of CPUs and their features Nß Identify CPU types Nß AMD Nß Intel Nß Hyper threading Nß Multi core Nß Dual core Nß Triple core Nß Quad core Nß Onchip cache Nß L1 Nß L2 Nß Speed (real vs. actual) Nß 32 bit vs. 64 bit Ûß1.5 Explain cooling methods and devices Nß Heat sinks Nß CPU and case fans 86498book.indb 2 7/22/09 5:37:18 AM Nß Liquid cooling systems Nß Thermal compound Ûß1.6 Compare and contrast memory types, characteristics and their purpose Nß Types Nß DRAM Nß SRAM Nß SDRAM Nß DDR / DDR2 / DDR3 Nß RAMBUS Nß Parity vs. Non-parity Nß ECC vs. non-ECC Nß Single sided vs. double sided Nß Single channel vs. -

AF IC05 Motherboards Unit 1

AF_IC05_ Motherboards Unit 1 Contents Introduction..................................................................................................................................2 Glossary.......................................................................................................................................3 Form factors.................................................................................................................................4 Common standards:...........................................................................................................5 ATX...........................................................................................................................6 Micro-ATX.................................................................................................................6 Mini-ITX.....................................................................................................................7 Motherboard components............................................................................................................8 CPU socket................................................................................................................9 Memory slots....................................................................................................................11 Chipset.............................................................................................................................12 Traditional chipset...................................................................................................13 -

PDSM4+ 1.0.Indb

PDSM4+ PDSME+ USER’S MANUAL Revision 1.0 The information in this User’s Manual has been carefully reviewed and is believed to be accurate. The vendor assumes no responsibility for any inaccuracies that may be contained in this document, makes no commitment to update or to keep current the information in this manual, or to notify any person or organization of the updates. Please Note: For the most up-to-date version of this manual, please see our web site at www.supermicro.com. SUPERMICRO COMPUTER reserves the right to make changes to the product described in this manual at any time and without notice. This product, including software, if any, and documenta- tion may not, in whole or in part, be copied, photocopied, reproduced, translated or reduced to any medium or machine without prior written consent. IN NO EVENT WILL SUPERMICRO COMPUTER BE LIABLE FOR DIRECT, INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES ARISING FROM THE USE OR INABILITY TO USE THIS PRODUCT OR DOCUMENTATION, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. IN PARTICULAR, THE VENDOR SHALL NOT HAVE LIABILITY FOR ANY HARDWARE, SOFTWARE, OR DATA STORED OR USED WITH THE PRODUCT, INCLUDING THE COSTS OF REPAIRING, REPLACING, INTEGRATING, INSTALLING OR RECOVERING SUCH HARDWARE, SOFTWARE, OR DATA. Any disputes arising between manufacturer and customer shall be governed by the laws of Santa Clara County in the State of California, USA. The State of California, County of Santa Clara shall be the exclusive venue for the resolution of any such disputes. Supermicro's total liability for all claims will not exceed the price paid for the hardware product. -

Desktop 3Rd Generation Intel® Core™ Processor Family, Desktop Intel® Pentium® Processor Family, Desktop Intel® Celeron® Processor Family, and LGA1155 Socket

Desktop 3rd Generation Intel® Core™ Processor Family, Desktop Intel® Pentium® Processor Family, Desktop Intel® Celeron® Processor Family, and LGA1155 Socket Thermal Mechanical Specifications and Design Guidelines (TMSDG) January 2013 Document Number: 326767-005 INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. A “Mission Critical Application” is any application in which failure of the Intel Product could result, directly or indirectly, in personal injury or death. SHOULD YOU PURCHASE OR USE INTEL'S PRODUCTS FOR ANY SUCH MISSION CRITICAL APPLICATION, YOU SHALL INDEMNIFY AND HOLD INTEL AND ITS SUBSIDIARIES, SUBCONTRACTORS AND AFFILIATES, AND THE DIRECTORS, OFFICERS, AND EMPLOYEES OF EACH, HARMLESS AGAINST ALL CLAIMS COSTS, DAMAGES, AND EXPENSES AND REASONABLE ATTORNEYS' FEES ARISING OUT OF, DIRECTLY OR INDIRECTLY, ANY CLAIM OF PRODUCT LIABILITY, PERSONAL INJURY, OR DEATH ARISING IN ANY WAY OUT OF SUCH MISSION CRITICAL APPLICATION, WHETHER OR NOT INTEL OR ITS SUBCONTRACTOR WAS NEGLIGENT IN THE DESIGN, MANUFACTURE, OR WARNING OF THE INTEL PRODUCT OR ANY OF ITS PARTS. Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked “reserved” or “undefined”. -

Pentium II Processor Thermal Design Guidelines

Pentium® II Processor Thermal Design Guidelines February 1999 Order Number: 243331-003 Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications. Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The Pentium® II processor may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request. Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product o rder. Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800- 548-4725 or by visiting Intel's website at http://www.intel.com. Copyright © Intel Corporation, 1997 - 1999 *Third-party brands and names are the property of their respective owners. -

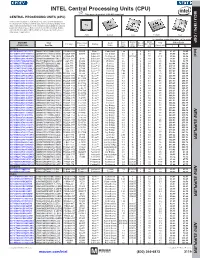

CPU) MCU / MPU / DSP This Page of Product Is Rohs Compliant

INTEL Central Processing Units (CPU) MPU /DSP MCU / This page of product is RoHS compliant. CENTRAL PROCESSING UNITS (CPU) Intel Processor families include the most powerful and flexible Central Processing Units (CPUs) available today. Utilizing industry leading 22nm device fabrication techniques, Intel continues to pack greater processing power into smaller spaces than ever before, providing desktop, mobile, and embedded products with maximum performance per watt across a wide range of applications. Atom Celeron Core Pentium Xeon For quantities greater than listed, call for quote. MOUSER Intel Core Cache Data Price Each Package Processor Family Code Freq. Size No. of Bus Width TDP STOCK NO. Part No. Series Name (GHz) (MB) Cores (bit) (Max) (W) 1 10 Desktop Intel 607-DF8064101211300Y DF8064101211300S R0VY FCBGA-559 D2550 Atom™ Cedarview 1.86 1 2 64 10 61.60 59.40 607-CM8063701444901S CM8063701444901S R10K FCLGA-1155 G1610 Celeron® Ivy Bridge 2.6 2 2 64 55 54.93 52.70 607-RK80532RC041128S RK80532RC041128S L6VR PPGA-478 - Celeron® Northwood 2.0 0.0156 1 32 52.8 42.00 40.50 607-CM8062301046804S CM8062301046804S R05J FCLGA-1155 G540 Celeron® Sandy Bridge 2.5 2 2 64 65 54.60 52.65 607-AT80571RG0641MLS AT80571RG0641MLS LGTZ LGA-775 E3400 Celeron® Wolfdale 2.6 1 2 64 65 54.93 52.70 607-HH80557PG0332MS HH80557PG0332MS LA99 LGA-775 E4300 Core™ 2 Conroe 1.8 2 2 64 65 139.44 133.78 607-AT80570PJ0806MS AT80570PJ0806MS LB9J LGA-775 E8400 Core™ 2 Wolfdale 3.0 6 2 64 65 207.04 196.00 607-AT80571PH0723MLS AT80571PH0723MLS LGW3 LGA-775 E7400 Core™ 2 Wolfdale -

Five9ns T3110 Tower Server

FIVE9NS DATA SHEET Note: This data sheet is for informational purposes. It is not a commitment to deliver hardware features or functionality. The development, release and timing of features and functionality described in this document are at the sole discretion of Five9 Network Systems. FIVE9NS T3110 TOWER SERVER The Five9NS T3110 is an entry-level, single socket, tower server. Powered by an Intel processor, this high-performance system provides I/O slot flexibility that enables seamless integration into a variety of OEM applications. HIGHLIGHTS: Flexible Tower Server Variety of expansion slots The Five9NS T3110 was designed with OEM needs in mind. With its Tower form factor rich feature set – including 7 expansion slots, remote management Supports Windows, Linux and capabilities, and high performance Intel 3400 series processor it’s an Solaris Operating Systems ideal fit for commercial printing and healthcare environments. The Remote system management Five9NS T3110 tower server is on the Oracle Solaris Hardware capabilities ideal for central Compatibility List (HCL). office and other demanding environments Easy to customize and integrate Specialty Services into existing infrastructure Easy to scale out as business OEM customers can choose from a host of services that will accelerate needs grow the integration process and reduce time to market. With our in-house Product Lifecycle Management service, Five9NS is uniquely positioned to architect systems for OEM customers. The Five9NS T3110 tower server is customizable and you can brand it as your own. We also provide free engineering support via experts who understand the unique requirements of OEM customers. The Five9NS Product Lifecycle Management service aims to help you proactively manage your product lifecycle. -

Dell EMC Poweredge R640 Technical Guide

Dell EMC PowerEdge R640 Technical Guide Regulatory Model: E39S Series Regulatory Type: E39S001 June 2021 Rev. A08 Notes, cautions, and warnings NOTE: A NOTE indicates important information that helps you make better use of your product. CAUTION: A CAUTION indicates either potential damage to hardware or loss of data and tells you how to avoid the problem. WARNING: A WARNING indicates a potential for property damage, personal injury, or death. © 2017 - 2021 Dell Inc. or its subsidiaries. All rights reserved. Dell, EMC, and other trademarks are trademarks of Dell Inc. or its subsidiaries. Other trademarks may be trademarks of their respective owners. Contents Chapter 1: Product overview......................................................................................................... 5 Introduction...........................................................................................................................................................................5 New technologies................................................................................................................................................................ 5 Chapter 2: System features...........................................................................................................7 Product comparison............................................................................................................................................................ 7 Technical specifications.................................................................................................................................................... -

TH55 HD Motherboard TH55 HD Specifcation

TH55 HD Motherboard • Supports the Intel Core i7 / i5 / i3 / Pentium Processors in the LGA1156 Package • Intel H55 single chip architecture • 7 Phases Power Design • Support 4-DIMM DDR3- 2000+(OC)/1800(OC)/1600/1333 up to 16G maximum capacity • 100% X.D.C Japanese solid capacitor • Integrated HDMI/DVI interface with HDCP Supporting all HD formats including 720P, 1080i, 1080P. ( Required processors with Intel HD Graphics ) • CPU integrated Graphics performance tunable via BIOS • BIOSTAR G.P.U (Green Power Utility) Technology for Energy Saving • BIOSTAR Toverclocker utility • Optimized to deliver full windows 7 Experience TH55 HD Specifcation CPU SUPPORT Intel® Core™ i7 LGA 1156 Processor Intel® Core™ i5 LGA 1156 Processor Intel® Core™ i3 LGA 1156 Processor BIOSTARIntel® Pentium® LGA 1156 Processor MEMORY Support Dual Channel DDR3 800/1066/1333/1600(OC)/1800(OC)/2000(OC) MHz 4 x DDR3 DIMM Memory Slot Max. Supports up to 16GB Memory INTEGRATED VIDEO By CPU model STORAGE 6 x SATA II Connector 1 x IDE Connector LAN Realtek RTL8111DL - 10/100/1000 Controller AUDIO CODEC Realtek ALC888 8+2 Channel HD Audio USB 4 x USB 2.0 Port 3 x USB 2.0 Header EXPANSION SLOT 1 x PCI-E 2.0 x16 Slot 1 x PCI-E 2.0 x4 Slot 2 x PCI Slot REAR I/O 1 x PS/2 Mouse 1 x PS/2 Keyboard 4 x USB 2.0 Port 1 x HDMI Connector 1 x DVI Connector 1 x VGA Port 1 x LAN Port 6 x Audio Jacks INTERNAL I/O 3 x USB 2.0 Header 6 x SATA II Connector (3Gb/s ) 1 x IDE Connector 1 x Front Audio Header 1 x Front Panel Header 1 x CD-IN Header 1 x S/PDIF-Out Header 1 x CPU Fan Connector 2 x -

Acer Aspire M5811 Service Guide

Acer Aspire M5811 Service Guide Service guide files and updates are available on the ACER/CSD web; for more information, please refer to http://csd.acer.com.tw PRINTED IN TAIWAN Revision History Please refer to the table below for the updates made on this service guide. Date Chapter Updates ii Copyright Copyright © 2009 by Acer Incorporated. All rights reserved. No part of this publication may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language or computer language, in any form or by any means, electronic, mechanical, magnetic, optical, chemical, manual or otherwise, without the prior written permission of Acer Incorporated. iii Disclaimer The information in this guide is subject to change without notice. Acer Incorporated makes no representations or warranties, either expressed or implied, with respect to the contents hereof and specifically disclaims any warranties of merchantability or fitness for any particular purpose. Any Acer Incorporated software described in this manual is sold or licensed "as is". Should the programs prove defective following their purchase, the buyer (and not Acer Incorporated, its distributor, or its dealer) assumes the entire cost of all necessary servicing, repair, and any incidental or consequential damages resulting from any defect in the software. Acer is a registered trademark of Acer Corporation. Intel is a registered trademark of Intel Corporation. Pentium Dual-Core, Celeron Dual-Core, Core 2 Duo, Core 2 Quad, Celeron, and combinations thereof, are trademarks of Intel Corporation. Other brand and product names are trademarks and/or registered trademarks of their respective holders. iv Conventions The following conventions are used in this manual: SCREEN Denotes actual messages that appear on screen. -

Xeon Replaces Pentium Pro: 7/13/98

1997 COMPUTER PRESS ASSOCIATION WINNER ♦ BEST COMPUTER NEWSLETTER VOLUME 12, NUMBER 9 JULY 13,1998 MICROPROCESSOR REPORT THE INSIDERS’ GUIDE TO MICROPROCESSOR HARDWARE Xeon Replaces Pentium Pro Intel Targets Servers and Workstations by Keith Diefendorff sure applied on the low end by AMD, Cyrix, and IDT. The problem for Intel is that it needs a high ASP to fuel the semi- Intel has plugged the gaping hole at the top end of its conductor R&D and fab improvements that keep it ahead of product line—previously served by the aging Pentium Pro— its competitors. with a Deschutes-based processor module the company Having so far failed to stimulate demand for higher labels Pentium II Xeon. As Figure 1 shows, the new processor performance (and higher priced) processors in PCs, Intel family will serve the midrange to high-end server and work- will try to take a larger share of the higher-margin worksta- station markets until the 64-bit Merced processor enters ser- tion and server markets. While these markets are each about vice in 2000. only 1% of the size of the PC market in unit volume, they can Pentium Pro was previously the only processor in easily bear 10 times the processor price. This fact makes these Intel’s lineup capable of addressing this high-end segment, markets immensely profitable and gives Intel an opportunity because it’s the only processor that supports four-way multi- to increase revenue and ASP. processing (MP), memories larger than four gigabytes, and Beyond the desire to prop up revenue and ASP, Intel fast ECC L2 caches larger than 512K—all minimum require- realizes that strategically it needs to own the markets on both ments of the high-end market. -

The Motherboard ‐ Chapter #5

The Motherboard ‐ Chapter #5 Amy Hissom Key Terms Advanced Transfer Cache (ATC)— A type of L2 cache contained within the Pentium processor housing that is embedded on the same core processor die as the CPU itself. Audio/modem riser (AMR) — A specification for a small slot on a motherboard to accommodate an audio or modem riser card. A controller on the motherboard contains some of the logic for the audio or modem functionality. Back side bus — The bus between the CPU and the L2 cache inside the CPU housing. Bus speed — The speed, or frequency, at which the data on the motherboard is moving. Communication and networking riser (CNR) — A specification for a small expansion slot on a motherboard that accommodates a small audio, modem, or network riser card. CISC (complex instruction set computing) — Earlier CPU type of instruction set. Cooler — A combination cooling fan and heat sink mounted on the top or side of a processor to keep it cool. Discrete L2 cache — A type of L2 cache contained within the Pentium processor housing, but on a different die, with a cache bus between the processor and the cache. Dual-voltage CPU — A CPU that requires two different voltages, one for internal processing and the other for I/O processing. Execution Trace Cache — A type of Level 1 cache used by some CPUs to hold decoded operations waiting to be executed. Expansion bus — A bus that does not run in sync with the system clock. EPIC (explicitly parallel instruction computing) — The CPU architecture used by the Intel Itanium chip that bundles programming instructions with instructions on how to use multiprocessing abilities to do two instructions in parallel.