Thomas E. Anderson

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Architectures for Adaptive Low-Power Embedded Multimedia Systems

Architectures for Adaptive Low-Power Embedded Multimedia Systems zur Erlangung des akademischen Grades eines Doktors der Ingenieurwissenschaften der Fakultät für Informatik Karlsruhe Institute of Technology (KIT) (The cooperation of the Universität Fridericiana zu Karlsruhe (TH) and the national research center of the Helmholtz-Gemeinschaft) genehmigte Dissertation von Muhammad Shafique Tag der mündlichen Prüfung: 31.01.2011 Referent: Prof. Dr.-Ing. Jörg Henkel, Karlsruhe Institute of Technology (KIT), Fakultät für Informatik, Lehrstuhl für Eingebettete Systeme (CES) Korreferent: Prof. Dr. Samarjit Chakraborty, Technische Universität München (TUM), Fakultät für Elektrotechnik und Informationtechnik, Lehrstuhl für Realzeit- Computersysteme (RCS) Muhammad Shafique Adlerstr. 3a 76133 Karlsruhe Hiermit erkläre ich an Eides statt, dass ich die von mir vorgelegte Arbeit selbständig verfasst habe, dass ich die verwendeten Quellen, Internet-Quellen und Hilfsmittel vollständig angegeben habe und dass ich die Stellen der Arbeit – einschließlich Tabellen, Karten und Abbildungen – die anderen Werken oder dem Internet im Wortlaut oder dem Sinn nach entnommen sind, auf jeden Fall unter Angabe der Quelle als Entlehnung kenntlich gemacht habe. ____________________________________ Muhammad Shafique Acknowledgements I would like to present my cordial gratitude to my advisor Prof. Dr. Jörg Henkel for his erudite and invaluable supervision with sustained inspirations and incessant motivation. He guided me to explore the challenging research problems while giving me the complete flexibility, which provided the rationale to unleash my ingenuity and creativity along with an in-depth exploration of various research issues. His encouragement and meticulous feedback wrapped in constructive criticism helped me to keep the impetus and to remain streamlined on the road of research that resulted in the triumphant completion of this work. -

PROFESSIONAL ACTIVITIES – Nam Ling

PROFESSIONAL ACTIVITIES – Nam Ling (1) MAJOR PROFESSIONAL LEADERSHIP POSITIONS: 1. General Co-Chair, 12th International Conference on Ubi-Media Computing (Umedia), Bali, Indonesia, August 6-9, 2019. 2. General Co-Chair, 4th International Symposium on Security and Privacy in Social Networks and Big Data (SocialSec), Santa Clara, California, U.S.A, December 10-11, 2018. 3. General Co-Chair, 11th International Conference on Ubi-Media Computing (Umedia), Nanjing, China, August 22 – 25, 2018. 4. Honorary Co-Chair, 10th International Conference on Ubi-Media Computing and Workshops (Umedia), Pattaya, Thailand, August 1 - 4, 2017. 5. General Co-Chair, 9th International Conference on Ubi-Media Computing (Umedia), Moscow, Russia, August 15 - 17, 2016. 6. General Chair, 2015 IEEE Workshop on Signal Processing Systems (SiPS), Hangzhou, China, October 14 - 16, 2015. 7. General Co-Chair, 8th International Conference on Ubi-Media Computing (Umedia), Colombo, Sri Lanka, August 24 – 25, 2015. 8. General Co-Chair, 7th International Conference on Ubi-Media Computing (Umedia), Ulaanbaatar, Mongolia, July 12 – 14, 2014. 9. General Co-Chair, 2nd International Workshop on Video Coding and Video Processing (VCVP), Shenzhen, China, January 21 – 23, 2014. 10. Technical Program Co-Chair, 2013 IEEE Visual Communications and Image Processing Conference (VCIP), Kuching, Sarawak, Malaysia, November 17 - 20, 2013. 11. General Chair, 2013 IEEE International Conference on Multimedia and Expo (ICME), San Jose, California, USA, July 15 – 19, 2013. (ICME is the flagship conference on multimedia research for the IEEE and is sponsored by four of the largest IEEE societies – Computer, Communications, Signal Processing, and Circuits and Systems.) 12. Technical Program Co-Chair, 2010 Asia-Pacific Signal and Information Processing Association Annual Summit and Conference (APSIPA ASC), Singapore, December 14 – 17, 2010. -

Lillian C. Pentecost Lillian [email protected] (732) 533-9504

Lillian C. Pentecost lillian [email protected] (732) 533-9504 EDUCATION Harvard University Cambridge, MA Ph.D. in Computer Science Projected May 2022 Advisors: David Brooks and Gu-Yeon Wei Harvard University Cambridge, MA S.M. (masters in passing) in Computer Science May 2019 Coursework includes: Advanced Machine Learning, Advanced Computer Architecture, Data Visualization, Seminar in Teaching the History of Science and Technology, Algorithms at the End of the Wire, Critical Pedagogy Seminar Colgate University Hamilton, NY Bachelor of Arts May 2016 Double Major: Computer Science and Physics with High Honors GPAs: Cumulative: 3.95/4.00, Physics: 4.03/4.00, Computer Science: 4.05/4.00 RESEARCH EXPERIENCE Harvard University Cambridge, MA Ph.D. Candidate August 2016 - Present Investigating and enabling the design and optimization of memory systems, including inte- gration of emerging and embedded non-volatile memory technologies and specialized hard- ware for machine learning applications, with an emphasis on understanding resilience and evaluating system and application-level implications of technology design choices. NVIDIA Research Westford, MA Ph.D. Research Intern Summer 2020 Conducted design space exploration of memory architecture and floorplanning choices with intensive analysis of efficient workload mappings for highly-distributed on-chip memory by building upon existing, open-source evaluation frameworks. (Virtual internship conducted from Boston, MA, collaborating with NVIDIA Architecture Research Group.) Microsoft Research Redmond, WA Ph.D. Research Intern Summer 2018 Profiled and analyzed deep neural network performance on a variety of hardware platforms with an emphasis on transformer-based models for translation, in addition to surveying and evaluating the state of available profiling tools across several popular ML frameworks, as part of a collaborative project between Microsoft Research and the Silicon, AI, and Performance group under Azure. -

Newsletter-202009.Pdf

1 September 2020, Vol. 50, No. 9 Online archive: http://www.sigda.org/publications/newsletter 1. SIGDA News From: Xiang Chen <[email protected]> 2. SIGDA Local Chapter News From: Yanzhi Wang <[email protected]> 3. "What is" Column Contributing author: Cong (Callie) Hao <[email protected]> From: Xun Jiao <[email protected]> 4. Paper Submission Deadlines From: Xin Zhao <[email protected]> 5. Upcoming Conferences and Symposia From: Xin Zhao <[email protected]> 6. SIGDA Partner Journal From: Matthew Morrison <[email protected]> From: Deming Chen <[email protected]> 7. Call for Nomination -- ACM TCPS EiC From: Krithi Ramamritham <[email protected]> 8. Technical Activities From: Ying Wang <[email protected]> 9. Notice to Authors Comments from the Editors Dear ACM/SIGDA members, We are excited to present to you the September e-newsletter. We encourage you to invite your students and colleagues to be a part of the SIGDA newsletter. The newsletter covers a wide range of information from the upcoming conferences and hot research topics to technical news and activities from our community. From this month, we add a new column titled "SIGDA Partner Journal" where we will introduce the dynamics of SIGDA related journals. For this month, we are introducing the new editorial board of ACM TODAES and announcing a new partnership between SIGDA and ACM TRETS. Get involved and contact us if you want to contribute an article or announcement. The newsletter is evolving, let us know what you think. Happy reading! Debjit Sinha, Keni Qiu, Editors-in-Chief, SIGDA E-News To renew your ACM SIGDA membership, please visit http://www.acm.org/renew or call between the hours of 8:30am to 4:30pm EST at +1-212-626-0500 (Global), or 1-800-342-6626 (US and Canada). -

AI Chips: What They Are and Why They Matter

APRIL 2020 AI Chips: What They Are and Why They Matter An AI Chips Reference AUTHORS Saif M. Khan Alexander Mann Table of Contents Introduction and Summary 3 The Laws of Chip Innovation 7 Transistor Shrinkage: Moore’s Law 7 Efficiency and Speed Improvements 8 Increasing Transistor Density Unlocks Improved Designs for Efficiency and Speed 9 Transistor Design is Reaching Fundamental Size Limits 10 The Slowing of Moore’s Law and the Decline of General-Purpose Chips 10 The Economies of Scale of General-Purpose Chips 10 Costs are Increasing Faster than the Semiconductor Market 11 The Semiconductor Industry’s Growth Rate is Unlikely to Increase 14 Chip Improvements as Moore’s Law Slows 15 Transistor Improvements Continue, but are Slowing 16 Improved Transistor Density Enables Specialization 18 The AI Chip Zoo 19 AI Chip Types 20 AI Chip Benchmarks 22 The Value of State-of-the-Art AI Chips 23 The Efficiency of State-of-the-Art AI Chips Translates into Cost-Effectiveness 23 Compute-Intensive AI Algorithms are Bottlenecked by Chip Costs and Speed 26 U.S. and Chinese AI Chips and Implications for National Competitiveness 27 Appendix A: Basics of Semiconductors and Chips 31 Appendix B: How AI Chips Work 33 Parallel Computing 33 Low-Precision Computing 34 Memory Optimization 35 Domain-Specific Languages 36 Appendix C: AI Chip Benchmarking Studies 37 Appendix D: Chip Economics Model 39 Chip Transistor Density, Design Costs, and Energy Costs 40 Foundry, Assembly, Test and Packaging Costs 41 Acknowledgments 44 Center for Security and Emerging Technology | 2 Introduction and Summary Artificial intelligence will play an important role in national and international security in the years to come. -

Ece Connections

ECE2019/2020 CONNECTIONS BUILDING THE NEW COMPUTER USING REVOLUTIONARY NEW ARCHITECTURES Page 16 ECE CONNECTIONS DIRECTOR’S REFLECTIONS: ALYSSA APSEL Wishna Robyn s I write this, our Cornell scaling alone isn’t the answer to more community is adapting powerful and more efficient computers. to the rapidly evolving We can build chips with upwards of four conditions resulting from billion transistors in a square centimeter the COVID-19 pandemic. (such as Apple’s A11 chip), but when My heart is heavy with attempting to make devices any smaller the distress, uncertainty and anxiety this the electrical properties become difficult to Abrings for so many of us, and in particular control. Pushing them faster also bumps seniors who were looking forward to their up against thermal issues as the predicted last semesters at Cornell. temperatures on-chip become comparable I recognize that these are difficult to that of a rocket nozzle. times and many uncertainties remain, Does that mean the end of innovation very nature of computation by building but I sincerely believe that by working in electronics? No, it’s just the beginning. memory devices, algorithms, circuits, and together as a community, we will achieve Instead of investing in manufacturing devices that directly integrate computation the best possible results for the health and that matches the pace of Moore’s law, even at the cellular level. The work well-being of all of Cornell. Although we major manufacturers have realized highlighted in this issue is exciting in that are distant from each other, our work in that it is cost effective to pursue other it breaks the traditional separation between ECE continues. -

Tushar Krishna

Tushar Krishna 266 Ferst Drive • School of Electrical and Computer Engineering • Atlanta, GA 30332, USA PHONE (+1) 206 601 6213 • E-MAIL [email protected] • WEB http://tusharkrishna.ece.gatech.edu ……………………...…………………….…………………….…………………….…………………….…………………….………………………………...………… RESEARCH INTERESTS Computer Architecture: multicore, parallel, heterogeneous, spatial, AI/ML accelerators Interconnection Networks: Networks-on-Chip, HPC switches, data-centers, FPGA networks ……………………...…………………….…………………….…………………….…………………….…………………….………………………………...………… EDUCATION Feb 2014 Massachusetts Institute of Technology Ph.D. in Electrical Engineering and Computer Science • Advisor: Li-Shiuan Peh • Committee: Srinivas Devadas and Joel Emer • Thesis: “Enabling Dedicated Single-Cycle Connections Over A Shared Network-on-Chip” Sep 2009 Princeton University M.S.E. in Electrical Engineering • Advisor: Li-Shiuan Peh • Thesis: “Networks-on-Chip with Hybrid Interconnects” Aug 2007 Indian Institute of Technology (IIT), Delhi B.Tech. (Honors) in Electrical Engineering ……………………...…………………….…………………….…………………….…………………….…………………….………………………………...………… PROFESSIONAL APPOINTMENTS Sept’19 -- Georgia Institute of Technology, Atlanta, GA, USA present ON Semiconductor Professor (Endowed Junior Professorship) School of Electrical and Computer Engineering Aug ’15 – Georgia Institute of Technology, Atlanta, GA, USA present Assistant Professor School of Electrical and Computer Engineering. School of Computer Science (Adjunct). Jan ’15 – Jul ‘15 Massachusetts Institute of Technology, SMART Center, -

Curriculum Vitae

Caroline Trippel Assistant Professor of Computer Science and Electrical Engineering, Stanford University Stanford University Phone: (574) 276-6171 Computer Science Department Email: [email protected] 353 Serra Mall, Stanford, CA 94305 Home: https://cs.stanford.edu/∼trippel Education 2013–2019 Princeton University, PhD, Computer Science / Computer Architecture Thesis: Concurrency and Security Verification in Heterogeneous Parallel Systems Advisor: Prof. Margaret Martonosi 2013–2015 Princeton University, MA, Computer Science / Computer Architecture 2009–2013 Purdue University, BS, Computer Engineering PhD Dissertation Research Despite parallelism and heterogeneity being around for a long time, the degree to which both are being simultaneously deployed poses grand challenge problems in computer architecture regarding ensuring the accuracy of event orderings and interleavings in system-wide executions. As it turns out, event orderings form the cornerstone of correctness (e.g., memory consistency models) and security (e.g., speculation-based hardware exploits) in modern processors. Thus, my dissertation work creates formal, automated techniques for specifying and verifying the accuracy of event orderings for programs running on heterogeneous, parallel systems to improve their correctness and security. Awards and Honors [1] Recipient of the 2021 VMware Early Career Faculty Grant [2] Recipient of the 2020 CGS/ProQuest Distinguished Dissertation Award [3] Recipient of the 2020 ACM SIGARCH/IEEE CS TCCA Outstanding Dissertation Award [4] CheckMate chosen as an IEEE MICRO Top Pick of 2018 (top 12 computer architecture papers of 2018) [5] Selected for 2018 MIT Rising Stars in EECS Workshop [6] Selected for 2018 ACM Heidelberg Laureate Forum [7] TriCheck chosen as an IEEE MICRO Top Pick of 2017 (top 12 computer architecture papers of 2017) [8] NVIDIA Graduate Fellowship Recipient, Fall 2017–Spring 2018 [9] NVIDIA Graduate Fellowship Finalist, Fall 2016–Spring 2017 [10] Richard E. -

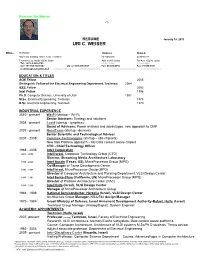

Uri C. Weiser

Resume: Uri Weiser -1- RESUME January 18, 2010 URI C. WEISER Office: Technion Homes 1: Home 2: Mayer EE Building, office: 1232, Technion 13 Hatchelet 20 Meltchet Technion City, Haifa 32000, Israel Atlit, 30300, Israel Tel-Aviv, 65234, Israel Tel: +972-4-829-4763 04-984-0350 03-566-0660 Cell: +972-54-788-0287 US cell 408-425-9021 Fax: 04-984-0950 Fax: 03-566-9367 [email protected] [email protected] [email protected] [email protected] [email protected] EDUCATION & TITLES ACM Fellow 2005 Distinguish Fellow of the Electrical Engineering Department, Technion 2004 IEEE Fellow 2002 Intel Fellow 1996 Ph.D. Computer Science, University of Utah 1981 M.Sc. Electrical Engineering, Technion 1975 B.Sc. Electrical Engineering, Technion 1970 INDUSTRIAL EXPERIENCE 2010 - present We-Fi (startup – Wi-Fi) Senior Advisors: Strategy and solutions 2008 - present Lucid (startup - graphics) Board of Advisors: Power analysis and advantages, new approach to CMP 2007 - present NovaTrans (startup - devices) Senior Scientific and Technological Advisor 2007 - 2008 Commex-Technologies (startup – x86 chipsets) New X86 Platform approach – I/O Data content aware chipset CTO - Chief Technology Officer 1988 - 2006 Intel Corporation 2001 - 2006 Intel Israel, Corporate Technology Group (CTG) Director, Streaming Media Architecture Laboratory 1999 - 2000 Intel Austin (Texas, US), MicroProcessor Group (MPG) Co-Manager of Texas Development Center 1993 - 1998 Intel Israel, MicroProcessor Group (MPG) Director of Computer Architecture and Planning Department, -

Summer/Fall 2015 Newsletter

INCREASING THE SUCCESS & PARTICIPATION OF WOMEN IN COMPUTING RESEARCH CRA-WomenSummer/Fall 2015 Edition NEWSLETTER This Issue: P2 Interview with Dilma Da Silva Highlight on Alum P5 Attend the Inaugural Virtual Undergraduate Sarah Ita Levitan Town Hall! Sarah Ita Levitan is a 3rd year PhD student in the Department of Computer Science at Columbia University. She is a member P7 Nomination Opportunities of the Spoken Language Processing group directed by Dr. Julia Hirschberg. Her research involves identifying spoken cues to deception and examining cultural and gender differences in P8 Alum News communicating and perceiving lies. She received her bachelor’s degree in computer science from Brooklyn College (CUNY). Before her P11-13 Awards senior year, she participated in the Distributed Research Experience for Undergraduates (DREU), studying acoustic and prosodic P14 News of Affiliated Groups entrainment in Supreme Court oral arguments. Sarah Ita is currently funded through an NSF-GRFP fellowship and is an IGERT fellow. continued on page 6 P14 Upcoming Events and Deadlines Natalie Enright Jerger wins Editors: Carla Ellis, Duke University Borg Early Career Award Amanda Stent, Yahoo Labs CRA-Women proudly announces Natalie Enright Jerger as this year’s BECA winner. Natalie is an associate professor in the Department of Electrical and Computer Engineering at the University of Toronto. Her research interests include multi- and many-core computer architectures, on-chip networks, cache coherence protocols, memory systems and approximate computing. Natalie is passionate about mentoring students and is deeply committed to increasing the participation of women in computer science and engineering. Natalie’s contributions to research have been recognized with several awards including the Ontario Ministry of Research and Innovation Early Researcher Award (2012), the Ontario Professional Engineers Young Engineer Medal (2014) and an Alfred P. -

Computing Research Association Annual Report FY 2013-2014

FY 2013-2014 ANNUAL REPORT Computing Research Association Annual Report FY 2013-2014 UNITING INDUSTRY, ACADEMIA AND GOVERNMENT TO ADVANCE COMPUTING RESEARCH AND CHANGE THE WORLD 1 FY 2013-2014 ANNUAL REPORT TaBLE OF CONTENTS Message From the Board Chair 3 Financial Statement 6 Highlights by Mission Area Leadership 7 Policy 11 Talent Development 13 CRA Members 24 Board of Directors 28 Staff 29 Committees and Joint Activities 30 OUR MISSION The mission of the Computing Research Association (CRA) is to enhance innovation by joining with industry, government and academia to strengthen research and advanced education in computing. CRA executes this mission by leading the computing research community, informing policymakers and the public, and facilitating the development of strong, diverse talent in the field. Founded in 1972, CRA’s membership includes more than 200 North American organizations active in computing research: academic departments of computer science and computer engineering, laboratories and centers (industry, government, and academia), and affiliated professional societies (AAAI, ACM, CACS/AIC, IEEE Computer Society, SIAM, and USENIX). Computing Research Association 1828 L St, NW, Suite 800 Washington, DC 20036 P: 202-234-2111 F: 202-667-1066 E: [email protected] W: www.cra.org 2 FY 2013-2014 ANNUAL REPORT MESSAGE FROM THE BOARD CHAIR I am delighted to report that 2013-14 was another very successful year for CRA’s efforts to strengthen research and advanced education in computing -- we have made substantial progress in our programs while ending the year on a positive financial note. The following report gives an excellent overview of CRA’s initiatives and activities in our three mission areas of leadership, talent development and policy during FY 2013-14. -

Margaret R. Martonosi

Margaret R. Martonosi Computer Science Bldg, Room 208 Email: [email protected] 35 Olden St. Phone: 609-258-1912 Princeton, NJ 08540 http://www.princeton.edu/~mrm Hugh Trumbull Adams ’35 Professor of Computer Science, Princeton University Assistant Director for Computer and Information Science and Engineering (CISE) at National Science Foundation. (IPA Rotator). Andrew Dickson White Visiting Professor-At-Large, Cornell University Associated faculty, Dept. of Electrical Engineering; Princeton Environmental Institute, Center for Information Technology Policy, Andlinger Center for Energy and the Environment. Research areas: Computer architectures and the hardware/software interface, particularly power-aware computing and mobile networks. HONORS IEEE Fellow. “For contributions to power-efficient computer architecture and systems design” ACM Fellow. “For contributions in power-aware computing” 2016-2022: Andrew Dickson White Visiting Professor-At-Large. Cornell University. Roughly twenty people worldwide are extended this title based on their professional stature and expertise, and are considered full members of the Cornell faculty during their six-year term appointment. 2019 SRC Aristotle Award, for graduate mentoring. 2018 IEEE Computer Society Technical Achievement Award. 2018 IEEE International Conference on High-Performance Computer Architecture Test-of-Time Paper award, honoring the long-term impact of our HPCA-5 (1999) paper entitled “Dynamically Exploiting Narrow Width Operands to Improve Processor Power and Performance” 2017 ACM SenSys Test-of-Time Paper award, honoring the long-term impact of our SenSys 2004 paper entitled “Hardware Design Experiences in ZebraNet”. 2017 ACM SIGMOBILE Test-of-Time Paper Award, honoring the long-term impact of our ASPLOS 2002 paper entitled “Energy-Efficient Computing for Wildlife Tracking: Design Tradeoffs and Early Experiences with ZebraNet”.