Japanese Semiconductor Industry Service : Volume II, 1986-1989

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

When Is a Microprocessor Not a Microprocessor? the Industrial Construction of Semiconductor Innovation I

Ross Bassett When is a Microprocessor not a Microprocessor? The Industrial Construction of Semiconductor Innovation I In the early 1990s an integrated circuit first made in 1969 and thus ante dating by two years the chip typically seen as the first microprocessor (Intel's 4004), became a microprocessor for the first time. The stimulus for this piece ofindustrial alchemy was a patent fight. A microprocessor patent had been issued to Texas Instruments, and companies faced with patent infringement lawsuits were looking for prior art with which to challenge it. 2 This old integrated circuit, but new microprocessor, was the ALl, designed by Lee Boysel and used in computers built by his start-up, Four-Phase Systems, established in 1968. In its 1990s reincarnation a demonstration system was built showing that the ALI could have oper ated according to the classic microprocessor model, with ROM (Read Only Memory), RAM (Random Access Memory), and I/O (Input/ Output) forming a basic computer. The operative words here are could have, for it was never used in that configuration during its normal life time. Instead it was used as one-third of a 24-bit CPU (Central Processing Unit) for a series ofcomputers built by Four-Phase.3 Examining the ALl through the lenses of the history of technology and business history puts Intel's microprocessor work into a different per spective. The differences between Four-Phase's and Intel's work were industrially constructed; they owed much to the different industries each saw itselfin.4 While putting a substantial part ofa central processing unit on a chip was not a discrete invention for Four-Phase or the computer industry, it was in the semiconductor industry. -

Formerly Streettracks Index Shares Funds

SECURITIES AND EXCHANGE COMMISSION FORM N-CSRS Certified semi-annual shareholder report of registered management investment companies filed on Form N-CSR Filing Date: 2012-06-04 | Period of Report: 2012-03-31 SEC Accession No. 0000950123-12-008860 (HTML Version on secdatabase.com) FILER SPDR INDEX SHARES FUNDS (Formerly streetTRACKS Mailing Address Business Address ONE LINCOLN STREET ONE LINCOLN STREET Index Shares Funds) CPH0326 CPH0326 BOSTON MA 02111 BOSTON MA 02111 CIK:1168164| IRS No.: 421537593 | State of Incorp.:MA | Fiscal Year End: 0930 866-787-2257 Type: N-CSRS | Act: 40 | File No.: 811-21145 | Film No.: 12885812 Copyright © 2012 www.secdatabase.com. All Rights Reserved. Please Consider the Environment Before Printing This Document UNITED STATES SECURITIES AND EXCHANGE COMMISSION Washington, D.C. 20549 FORM N-CSR CERTIFIED SHAREHOLDER REPORT OF REGISTERED MANAGEMENT INVESTMENT COMPANIES Investment Company Act file number: 811-21145 SPDR® INDEX SHARES FUNDS (Exact name of registrant as specified in charter) One Lincoln Street, Boston, Massachusetts 02111 (Address of principal executive offices) (zip code) Ryan M. Louvar, Esq. State Street Bank and Trust Company One Lincoln Street CPH0326 Boston, MA 02111 (Name and address of agent for service) Copy to: W. John McGuire, Esq. Morgan, Lewis & Bockius LLP 1111 Pennsylvania Avenue, N.W. Washington, DC 20004 Registrants telephone number, including area code: (866) 787-2257 Date of fiscal year end: September 30 Date of reporting period: March 31, 2012 Copyright © 2012 www.secdatabase.com. All Rights Reserved. Please Consider the Environment Before Printing This Document Item 1: Report to Shareholders Copyright © 2012 www.secdatabase.com. -

Flexshares 2019 Semiannual Report

FlexShares® Trust Semiannual Report April 30, 2019 Beginning on January 1, 2021, as permitted by regulations adopted by the Securities and Exchange Commission, paper copies of FlexShares® Trust’s shareholder reports like this one will no longer be sent by mail, unless you specifically request paper copies of the reports from FlexShares® Trust or your financial intermediary, such as a broker-dealer or bank. Instead, the reports will be made available on FlexShares® Trust’s website (www.flexshares.com) and you will be notified by mail each time a report is posted and provided with a website link to access the report. If you have already elected to receive your shareholder reports electronically, you will not be affected by this change and you need not take any action. You may elect to receive shareholder reports and other communications from FlexShares® Trust electronically at any time by contacting your financial intermediary. You may elect to receive all future reports in paper free of charge. Please contact your financial intermediary to continue receiving paper copies of your shareholder reports. Your election to receive reports in paper will apply to all funds in FlexShares® Trust that you hold in your account at the financial intermediary. You must provide separate instructions to each of your financial intermediaries. Table of Contents Statements of Assets and Liabilities ................................................ 2 Statements of Operations................................................................. 9 Statements of Changes -

Quarterly Portfolio Disclosure

Schroders 29/05/2020 ASX Limited Schroders Investment Management Australia Limited ASX Market Announcements Office ABN:22 000 443 274 Exchange Centre Australian Financial Services Licence: 226473 20 Bridge Street Sydney NSW 2000 Level 20 Angel Place 123 Pitt Street Sydney NSW 2000 P: 1300 180 103 E: [email protected] W: www.schroders.com.au/GROW Schroder Real Return Fund (Managed Fund) Quarterly holdings disclosure for quarter ending 31 March 2020 Holdings on a full look through basis as at 31 March 2020 Weight Asset Name (%) 1&1 DRILLISCH AG 0.000% 1011778 BC / NEW RED FIN 4.25 15-MAY-2024 144a (SECURED) 0.002% 1011778 BC UNLIMITED LIABILITY CO 3.875 15-JAN-2028 144a (SECURED) 0.001% 1011778 BC UNLIMITED LIABILITY CO 4.375 15-JAN-2028 144a (SECURED) 0.001% 1011778 BC UNLIMITED LIABILITY CO 5.0 15-OCT-2025 144a (SECURED) 0.004% 1MDB GLOBAL INVESTMENTS LTD 4.4 09-MAR-2023 Reg-S (SENIOR) 0.011% 1ST SOURCE CORP 0.000% 21VIANET GROUP ADR REPRESENTING SI ADR 0.000% 2I RETE GAS SPA 1.608 31-OCT-2027 Reg-S (SENIOR) 0.001% 2I RETE GAS SPA 2.195 11-SEP-2025 Reg-S (SENIOR) 0.001% 2U INC 0.000% 360 SECURITY TECHNOLOGY INC A A 0.000% 360 SECURITY TECHNOLOGY INC A A 0.000% 361 DEGREES INTERNATIONAL LTD 0.000% 3D SYSTEMS CORP 0.000% 3I GROUP PLC 0.002% 3M 0.020% 3M CO 1.625 19-SEP-2021 (SENIOR) 0.001% 3M CO 1.75 14-FEB-2023 (SENIOR) 0.001% 3M CO 2.0 14-FEB-2025 (SENIOR) 0.001% 3M CO 2.0 26-JUN-2022 (SENIOR) 0.001% 3M CO 2.25 15-MAR-2023 (SENIOR) 0.001% 3M CO 2.75 01-MAR-2022 (SENIOR) 0.001% 3M CO 3.25 14-FEB-2024 (SENIOR) 0.002% -

The Birth, Evolution and Future of Microprocessor

The Birth, Evolution and Future of Microprocessor Swetha Kogatam Computer Science Department San Jose State University San Jose, CA 95192 408-924-1000 [email protected] ABSTRACT timed sequence through the bus system to output devices such as The world's first microprocessor, the 4004, was co-developed by CRT Screens, networks, or printers. In some cases, the terms Busicom, a Japanese manufacturer of calculators, and Intel, a U.S. 'CPU' and 'microprocessor' are used interchangeably to denote the manufacturer of semiconductors. The basic architecture of 4004 same device. was developed in August 1969; a concrete plan for the 4004 The different ways in which microprocessors are categorized are: system was finalized in December 1969; and the first microprocessor was successfully developed in March 1971. a) CISC (Complex Instruction Set Computers) Microprocessors, which became the "technology to open up a new b) RISC (Reduced Instruction Set Computers) era," brought two outstanding impacts, "power of intelligence" and "power of computing". First, microprocessors opened up a new a) VLIW(Very Long Instruction Word Computers) "era of programming" through replacing with software, the b) Super scalar processors hardwired logic based on IC's of the former "era of logic". At the same time, microprocessors allowed young engineers access to "power of computing" for the creative development of personal 2. BIRTH OF THE MICROPROCESSOR computers and computer games, which in turn led to growth in the In 1970, Intel introduced the first dynamic RAM, which increased software industry, and paved the way to the development of high- IC memory by a factor of four. -

Proposed B.A. in Global Cultural Studies

PROPOSAL: BACHELOR OF ARTS IN GLOBAL CULTURAL STUDIES Department of International Language and Culture Studies Ana Benito CONTENT Global Cultural Studies Proposal ................................................................ 3 Proposed Curriculum .................................................................................. 7 Syllabi of New/Modified Courses .............................................................. 10 Letters of Endorsement ................................................................................ 24 Global Cultural Studies Jobs ........................................................................ 26 International Companies in Indiana ............................................................ 29 Northeast Indiana College and University Majors ....................................... 38 Proposal for a B.A. in Global Cultural Studies Purdue University Fort Wayne May 5, 2018 Ana Benito, Ph.D., Department of International Language and Culture Studies. Introduction: This degree would be offered by the Department of International Language and Culture Studies in the College of Arts and Sciences. The new B.A. degree would cover studies in the areas of international languages and global cultures, with three possible concentrations divided as follows: 1- Global Cultural Studies (33 credits): It will combine the study of two different languages. For example, students might combine the study of German and Japanese or the study of French and Arabic or Spanish and Arabic. Students in this track are encouraged to -

Avm 40 | 50 Operatingmanual

AVM 40 | 50 OPERATING MANUAL UPDATES: www.anthemAV.com SOFTWARE VERSION 1.3x ™ SAFETY PRECAUTIONS READ THIS SECTION CAREFULLY BEFORE PROCEEDING! WARNING RISK OF ELECTRIC SHOCK DO NOT OPEN WARNING: TO REDUCE THE RISK OF ELECTRIC SHOCK, DO NOT REMOVE COVER (OR BACK). NO USER-SERVICEABLE PARTS INSIDE. REFER SERVICING TO QUALIFIED SERVICE PERSONNEL. The lightning flash with arrowpoint within an equilateral triangle warns of the presence of uninsulated “dangerous voltage” within the product’s enclosure that may be of sufficient magnitude to constitute a risk of electric shock to persons. The exclamation point within an equilateral triangle warns users of the presence of important operating and maintenance (servicing) instructions in the literature accompanying the appliance. WARNING: TO REDUCE THE RISK OF FIRE OR ELECTRIC SHOCK, DO NOT EXPOSE THIS PRODUCT TO RAIN OR MOISTURE AND OBJECTS FILLED WITH LIQUIDS, SUCH AS VASES, SHOULD NOT BE PLACED ON THIS PRODUCT. CAUTION: TO PREVENT ELECTRIC SHOCK, MATCH WIDE BLADE OF PLUG TO WIDE SLOT, FULLY INSERT. CAUTION: FOR CONTINUED PROTECTION AGAINST RISK OF FIRE, REPLACE THE FUSE ONLY WITH THE SAME AMPERAGE AND VOLTAGE TYPE. REFER REPLACEMENT TO QUALIFIED SERVICE PERSONNEL. WARNING: UNIT MAY BECOME HOT. ALWAYS PROVIDE ADEQUATE VENTILATION TO ALLOW FOR COOLING. DO NOT PLACE NEAR A HEAT SOURCE, OR IN SPACES THAT CAN RESTRICT VENTILATION. IMPORTANT SAFETY INSTRUCTIONS 1. Read Instructions – All the safety and operating instructions should be read before the product is operated. 2. Retain Instructions – The safety and operating instructions should be retained for future reference. 3. Heed Warnings – All warnings on the product and in the operating instructions should be adhered to. -

Microprocessors in the 1970'S

Part II 1970's -- The Altair/Apple Era. 3/1 3/2 Part II 1970’s -- The Altair/Apple era Figure 3.1: A graphical history of personal computers in the 1970’s, the MITS Altair and Apple Computer era. Microprocessors in the 1970’s 3/3 Figure 3.2: Andrew S. Grove, Robert N. Noyce and Gordon E. Moore. Figure 3.3: Marcian E. “Ted” Hoff. Photographs are courtesy of Intel Corporation. 3/4 Part II 1970’s -- The Altair/Apple era Figure 3.4: The Intel MCS-4 (Micro Computer System 4) basic system. Figure 3.5: A photomicrograph of the Intel 4004 microprocessor. Photographs are courtesy of Intel Corporation. Chapter 3 Microprocessors in the 1970's The creation of the transistor in 1947 and the development of the integrated circuit in 1958/59, is the technology that formed the basis for the microprocessor. Initially the technology only enabled a restricted number of components on a single chip. However this changed significantly in the following years. The technology evolved from Small Scale Integration (SSI) in the early 1960's to Medium Scale Integration (MSI) with a few hundred components in the mid 1960's. By the late 1960's LSI (Large Scale Integration) chips with thousands of components had occurred. This rapid increase in the number of components in an integrated circuit led to what became known as Moore’s Law. The concept of this law was described by Gordon Moore in an article entitled “Cramming More Components Onto Integrated Circuits” in the April 1965 issue of Electronics magazine [338]. -

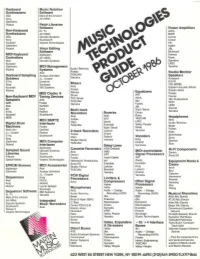

B~F";, Roland Patch Librarian Software Power Amplifiers Non-Keyboard Dr

Keyboard Music Notation Synthesizers Software Akai Mark 01 the Unicorn Korg Jim Miller Oberheim B~f";, Roland Patch Librarian Software Power Amplifiers Non-Keyboard Dr. Ts Ashly Synthesizers Jim Miller C ~O BGW Akai Opcode Systems Carver Korg Southworth Crown Kurzweil Voyelra Technologies HH Oberheim Haller Roland Voice Editing JBL Software Mcintosh MIDI Keyboard digidesign Ramsa Controllers Jim Miller Rane ~OoQ~ Symetrix Akai Opcode Systems Kurzwell UREI Oberheim MIDI Management Yamaha Roland Systems AudiO-Technlca Akai Fostex Studio Monitor Keyboard Sampling Axxess Unlimited TASCAM Speakers Systems J.L. Cooper Yamaha Auratone E-mu Drawmer B&W Korg Sycologic Mixers CSI (M DM) Kurzweil 360 Systems Akai Eastern Acoustic Works Roland Fostex Electro-Voice Ramsa Fostex MIDI Clocks & ART Shure Fourier Non-Keyboard MIDI Timing Devices Ashly TAC/Amek JBL Professional Samplers AXE dbx TASCAM ROR AMS Fostex Fostex Yamaha UREI Akai Gartield JBL Visonik bel Korg Klark-Teknik Multi-track Yamaha E-mu Roland Recorders Reverbs Orban Kurzweil Southworth Akai AKG Rane Headphones MDB TASCAM Fostex ART AKG MIDI /SMPTE UREI Otari Alesis Audio-Technica Digital Drum Interfaces Valley People TASCAM Eventide Beyer Machines Fostex White Klark-Teknik Fostex Akai-Linn Garfield 2-track Recorders Lexicon Yamaha J.L. Cooper Roland Koss Fostex Orban E-mu Southworth Sennheiser Olari Roland Vocoders Sony Korg Korg Studer/ Revox Yamaha Stanton Oberheim MIDI /Computer Roland TASCAM Stax Roland Interfaces Delay Lines Syntovox digidesign ADSlDeltalab Sampled Sound Cassette Recorders Hi-Fi Components Opcode Systems Akai AMS MIDI-controllable Libraries Roland Denon Denon ART Signal Processors Sony ES K-Muse Southworth Fostex Audio Digital ART Optical Media Voyetra Technologies Nakamichi Professional bel Alesis Equipment Racks & Sony ES Eventide Eventide Cases EPROM Burners MIDI Accessories Lexicon Korg Studer/ Revox Anvil digidesign Akai Lexicon TASCAM Marshall Bud Oberheim Axxess Unlimited Roland Yamaha Calzone J.L. -

DIRECTV® Universal Remote Control User's Guide

DirecTV-M2081A.qxd 12/22/2004 3:44 PM Page 1 ® DIRECTV® Universal Remote Control User’s Guide DirecTV-M2081A.qxd 12/22/2004 3:44 PM Page 2 TABLE OF CONTENTS Introduction . .3 Features and Functions . .4 Key Charts . .4 Installing Batteries . .8 Controlling DIRECTV® Receiver. .9 Programming DIRECTV Remote . .9 Setup Codes for DIRECTV Receivers . .10 Setup Codes for DIRECTV HD Receivers . .10 Setup Codes for DIRECTV DVRs . .10 Programming to Control Your TV. .11 Programming the TV Input Key . .11 Deactivate the TV Input Select Key . .11 Programming Other Component Controls . .12 Manufacturer Codes . .13 Setup Codes for TVs . .13 Setup Codes for VCRs . .16 Setup Codes for DVD Players . .19 Setup Codes for Stereo Receivers . .20 Setup Codes for Stereo Amplifiers . .22 Searching For Your Code in AV1 or AV2 Mode . .23 Verifying The Codes . .23 Changing Volume Lock . .24 Restore Factory Default Settings . .25 Troubleshooting . .26 Repair or Replacement Policy . .27 Additional Information . .28 2 DirecTV-M2081A.qxd 12/22/2004 3:44 PM Page 3 INTRODUCTION Congratulations! You now have an exclusive DIRECTV® Universal Remote Control that will control four components, including a DIRECTV Receiver, TV, and two stereo or video components (e.g 2nd TV, DVD, or stereo). Moreover, its sophisticated technology allows you to consolidate the clutter of your original remote controls into one easy-to-use unit that's packed with features such as: z Four-position slide switch for easy component selection z Code library for popular video and stereo components z Code search to help program control of older or discon- tinued components z Memory protection to ensure you will not have to re- program the remote when the batteries are replaced Before using your DIRECTV Universal Remote Control, you may need to program it to operate with your particular com- ponent. -

Superior Performance Co-Ni Alloy Product (SPRON)® Creating Time - Optimizing Time - Enriching Time

Superior performance Co-Ni Alloy Product (SPRON)® Creating Time - Optimizing Time - Enriching Time Seiko Instruments Inc. (SII), founded in 1937 as a member of the Seiko Group specializing in the manufacture of watches, has leveraged its core competency in high precision watches to create a wide range of new products and technologies. Over the years SII has developed high-precision processed parts and machine tools that pride themselves on their sub-micron processing capability, quartz crystals that came about as a result of our quartz watch R&D, and electronic components such as micro batteries. Optimizing our extensive experience and expertise, we have since diversified into such new fields as compact, lightweight, exceedingly quiet thermal printers, and inkjet printheads, a key component in wide format inkjet printers for corporate use. SII, in the years to come, will maintain an uncompromised dedication to its time-honored technologies and innovations of craftsmanship, miniaturization, and efficiency that meet the needs of our changing society and enrich the lives of those around us. SEIKO HOLDINGS GROUP 1881 1917 1983 1997 2007 K. Hattori K. Hattori & Co., Ltd. Hattori Seiko Co., Ltd. Seiko Corporation Seiko Holdings Corporation 2005 Today’s Seiko NPC Corporation 2001 Seiko Watch Corporation 1993 Today’s Seiko Time Systems Inc. 1947 Wako Co., Ltd. 1996 Seiko Clock Inc. 1892 1970 Seikosha Seikosha Co., Ltd. 1996 Seiko Precision Inc. 2013 Seiko Solutions Inc. 1983 1937 Seiko Instruments & 1997 Daini Seikosha Co., Ltd. Electronics Ltd. -

VIDEO GAME SUBCULTURES Playing at the Periphery of Mainstream Culture Edited by Marco Benoît Carbone & Paolo Ruffino

ISSN 2280-7705 www.gamejournal.it Published by LUDICA Issue 03, 2014 – volume 1: JOURNAL (PEER-REVIEWED) VIDEO GAME SUBCULTURES Playing at the periphery of mainstream culture Edited by Marco Benoît Carbone & Paolo Ruffino GAME JOURNAL – Peer Reviewed Section Issue 03 – 2014 GAME Journal A PROJECT BY SUPERVISING EDITORS Antioco Floris (Università di Cagliari), Roy Menarini (Università di Bologna), Peppino Ortoleva (Università di Torino), Leonardo Quaresima (Università di Udine). EDITORS WITH THE PATRONAGE OF Marco Benoît Carbone (University College London), Giovanni Caruso (Università di Udine), Riccardo Fassone (Università di Torino), Gabriele Ferri (Indiana University), Adam Gallimore (University of Warwick), Ivan Girina (University of Warwick), Federico Giordano (Università per Stranieri di Perugia), Dipartimento di Storia, Beni Culturali e Territorio Valentina Paggiarin, Justin Pickard, Paolo Ruffino (Goldsmiths, University of London), Mauro Salvador (Università Cattolica, Milano), Marco Teti (Università di Ferrara). PARTNERS ADVISORY BOARD Espen Aarseth (IT University of Copenaghen), Matteo Bittanti (California College of the Arts), Jay David Bolter (Georgia Institute of Technology), Gordon C. Calleja (IT University of Copenaghen), Gianni Canova (IULM, Milano), Antonio Catolfi (Università per Stranieri di Perugia), Mia Consalvo (Ohio University), Patrick Coppock (Università di Modena e Reggio Emilia), Ruggero Eugeni (Università Cattolica del Sacro Cuore, Milano), Roy Menarini (Università di Bologna), Enrico Menduni (Università di