Apple ][ Emulation on an AVR Microcontroller

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

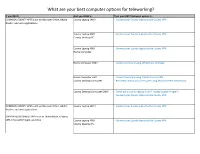

What Are Your Best Computer Options for Teleworking?

What are your best computer options for teleworking? If you NEED… And you HAVE a… Then your BEST telework option is… COMMON COUNTY APPS such as Microsoft Office, Adobe County Laptop ONLY - Connect your County laptop to the County VPN Reader, and web applications County Laptop AND - Connect your County laptop to the County VPN County Desktop PC County Laptop AND - Connect your County laptop to the County VPN Home Computer Home Computer ONLY - Connect remotely using VDI (Virtual Desktop) Home Computer AND - Connect remotely using Dakota County VPN County Desktop Computer - Remotely control your computer using Windows Remote Desktop County Desktop Computer ONLY - Check out a County laptop from IT Laptop Loaner Program - Connect your County laptop to the County VPN COMMON COUNTY APPS such as Microsoft Office, Adobe County Laptop ONLY - Connect your County laptop to the County VPN Reader, and web applications SUPPORTED BUSINESS APPS such as OneSolution, OnBase, SIRE, Microsoft Project, and Visio County Laptop AND - Connect your County laptop to the County VPN County Desktop PC If you NEED… And you HAVE a… Then your BEST telework option is… County Laptop AND - Connect your County laptop to the County VPN Home Computer Home Computer ONLY - Contact the County IT Help Desk at 651/438-4346 Home Computer AND - Connect remotely using Dakota County VPN County Desktop Computer - Remotely control your computer using Windows Remote Desktop County Desktop Computer ONLY - Check out a County laptop from IT Laptop Loaner Program - Connect your County laptop -

"Bob" Schreiner

Oral History of Robert “Bob” Schreiner Interviewed by: Stephen Diamond Recorded: June 10, 2013 Mountain View, California CHM Reference number: X6873.2014 © 2013 Computer History Museum Oral History of Robert “Bob” Schreiner Stephen Diamond: We're here at the Computer History Museum with Bob Schreiner. It's June 10th, 2013, and we're going to talk about the oral history of Synertek and the 6502. Welcome, Bob. Thanks for being here. Can you introduce yourself to us? Robert “Bob” Schreiner: Okay. My name is Bob Schreiner. I'm an ex-Fairchilder, one of the Fairchildren in the valley, and then involved in running a couple of other small semiconductor companies, and I started a semiconductor company. Diamond: So that would be Synertek. Schreiner: Synertek. Diamond: Tell us about that. Schreiner: Okay. As you know from an earlier session I left Fairchild Semiconductor around 1971. And at the time I left I was running the LSI program at Fairchild, and I was a big believer that the future marketplace for MOS technology would be in the custom area. And since Fairchild let that whole thing fall apart, I decided there's got to be room for a company to start up to do that very thing, work with big producers of hardware and develop custom chips for them so they would have a propriety product that would be difficult to copy. So I wrote a business plan, and I went around to a number of manufacturers. I had a computer guy [General Automation], and I had Bulova Watch Company, and I had a company that made electronic telephones [American Telephones], and who was the fourth guy? Escapes my memory right now, but the pitch basically was, "Your business, which now you manufacture things with discrete components, it's going to change. -

Scaling the Digital Divide: Home Computer Technology and Student Achievement

Scaling the Digital Divide Home Computer Technology and Student Achievement J a c o b V i g d o r a n d H e l e n l a d d w o r k i n g p a p e r 4 8 • j u n e 2 0 1 0 Scaling the Digital Divide: Home Computer Technology and Student Achievement Jacob L. Vigdor [email protected] Duke University Helen F. Ladd Duke University Contents Acknowledgements ii Abstract iii Introduction 1 Basic Evidence on Home Computer Use by North Carolina Public School Students 5 Access to home computers 5 Access to broadband internet service 7 How Home Computer Technology Might Influence Academic Achievement 10 An Adolescent's time allocation problem 10 Adapting the rational model to ten-year-olds 13 Estimation strategy 14 The Impact of Home Computer Technology on Test Scores 16 Comparing across- and within-student estimates 16 Extensions and robustness checks 22 Testing for effect heterogeneity 25 Examining the mechanism: broadband access and homework effort 29 Conclusions 34 References 36 Appendix Table 1 39 i Acknowledgements The authors are grateful to the William T. Grant Foundation and the National Center for Analysis of Longitudinal Data in Education Research (CALDER), supported through Grant R305A060018 to the Urban Institute from the Institute of Education Sciences, U.S. Department of Education for research support. They wish to thank Jon Guryan, Jesse Shapiro, Tim Smeeding, Andrew Leigh, and seminar participants at the University of Michigan, the University of Florida, Cornell University, the University of Missouri‐ Columbia, the University of Toronto, Georgetown University, Harvard University, the University of Chicago, Syracuse University, the Australian National University, the University of South Australia, and Deakin University for helpful comments on earlier drafts. -

Setup Outlook on Your Home Computer

Setup Outlook on your Home Computer Office 2010: 1. Run Microsoft Outlook 2010 2. When the startup wizard opens click Next. 3. When prompted to configure an E-mail Account select Yes and then click Next. 4. The Auto Account Setup will display next, select E-mail Account and fill in the information. Your password is your network password, the same one you use to log into computers on campus. After you fill the information in click Next. 5. Outlook will begin to setup your account; it may take a few minutes before the next window pops up. 6. You will be prompted with some sort of login screen. The one shown here offers 3 choices (Select the middle one if this is the case), but others may only offer 1. Type in the same username you use to login to campus computers but precede it with sdsmt\ Your password will be the same one you use to login on campus. Click OK to continue. 7. Outlook will finish setting up your account; this may take a few minutes. When it is done press the Finish button. 8. Outlook will start up and will begin to download your emails, contacts, and calendar from the server. This may take several minutes; there will be a green loading bar at the bottom of the window. Office 2007: 1. Run Microsoft Outlook 2007 2. When the startup wizard opens click Next. 3. When prompted to configure an E-mail Account select Yes and then click Next. 4. The Auto Account Setup will display next, select E-mail Account and fill in the information. -

The Cost of Using Computers

Summary: Students calculate and compare electrical costs of computers in various modes. Cost of Computers Grade Level: 5-8 Subject Areas: English Objectives puters, lights, and monitors when they’re not (Media and Technology, Research By the end of this activity, students will be in use reduces the number of comfort com- and Inquiry), Mathematics, able to plaints and air conditioning costs. Science (Physical) • explain that different types of computers use different amounts of electricity; There are many computer myths that have been dispelled over the years. One myth is Setting: Classroom • compare and contrast computer mode settings and their electricity use; and that screen-savers save energy. In fact, it Time: • identify ways to conserve electricity when takes the same amount of electricity to move that fish around your screen as it does to do Preparation: 1 hour using computers. any word processing. Activity: two 50-minute periods Rationale Vocabulary: Another myth is that it takes more energy to Calculating the cost of computers will help turn off and restart your computer than it Blended rate, CPU, Electric rate, students realize potential energy savings both does to just leave it on all the time. It is more Kilowatt-hour, Sleep mode, at school and at home. likely that your computer will be outdated Standby consumption, Watt, Watt before it is worn out by turning it off and on. meter Materials There are some school districts that require • Copies of Calculating Computer Costs Major Concept Areas: computers to be left on at night for software Activity Sheet upgrades and network maintenance; these • Quality of life • Calculator (optional) units are often automatically shut down after • Management of energy the upgrades are complete. -

Professor Won Woo Ro, School of Electrical and Electronic Engineering Yonsei University the Intel® 4004 Microprocessor, Introdu

Professor Won Woo Ro, School of Electrical and Electronic Engineering Yonsei University The 1st Microprocessor The Intel® 4004 microprocessor, introduced in November 1971 An electronics revolution that changed our world. There were no customer‐ programmable microprocessors on the market before the 4004. It propelled software into the limelight as a key player in the world of digital electronics design. 4004 Microprocessor Display at New Intel Museum A Japanese calculator maker (Busicom) asked to design: A set of 12 custom logic chips for a line of programmable calculators. Marcian E. "Ted" Hoff Recognized the integrated circuit technology (of the day) had advanced enough to build a single chip, general purpose computer. Federico Faggin to turn Hoff's vision into a silicon reality. (In less than one year, Faggin and his team delivered the 4004, which was introduced in November, 1971.) The world's first microprocessor application was this Busicom calculator. (sold about 100,000 calculators.) Measuring 1/8 inch wide by 1/6 inch long, consisting of 2,300 transistors, Intel’s 4004 microprocessor had as much computing power as the first electronic computer, ENIAC. 2 inch 4004 and 12 inch Core™2 Duo wafer ENIAC, built in 1946, filled 3000‐cubic‐ feet of space and contained 18,000 vacuum tubes. The 4004 microprocessor could execute 60,000 operations per second Running frequency: 108 KHz Founders wanted to name their new company Moore Noyce. However the name sounds very much similar to “more noise”. "Only the paranoid survive". Moore received a B.S. degree in Chemistry from the University of California, Berkeley in 1950 and a Ph.D. -

NMOS 6510 Unintended Opcodes No More Secrets (V0.95 - 24/12/20)

NMOS 6510 Unintended Opcodes no more secrets (v0.95 - 24/12/20) (w) 2013-2020 groepaz/solution, all rights reversed Contents Preface...................................................................................................................................................I Scope of this Document....................................................................................................................I Intended Audience............................................................................................................................I License..............................................................................................................................................I What you get...................................................................................................................................II Naming Conventions.....................................................................................................................III Address-Mode Abbreviations...................................................................................................III Mnemonics................................................................................................................................III Processor Flags.........................................................................................................................IV Opcode Matrix......................................................................................................................................1 Unintended -

6502 Introduction

6502 Introduction Philipp Koehn 18 September 2019 Philipp Koehn Computer Systems Fundamentals: 6502 Introduction 18 September 2019 1 some history Philipp Koehn Computer Systems Fundamentals: 6502 Introduction 18 September 2019 1971 2 • First microprocessor on an integrated circuit: Intel 4004 • 4-bit central processing unit, 12 bit address space (4KB) Philipp Koehn Computer Systems Fundamentals: 6502 Introduction 18 September 2019 1975 3 • MOS Technology 6502 • Dominant CPU in home computers for a decade (Atari, Apple II, Nintendo Entertainment System, Commodore PET) Philipp Koehn Computer Systems Fundamentals: 6502 Introduction 18 September 2019 1977 4 • Atari 2600 • Video game console: Pong, Pac Man, ... connected to TV Philipp Koehn Computer Systems Fundamentals: 6502 Introduction 18 September 2019 1980 5 • Commodore VIC20 • 1 MHz, 5KB RAM, BASIC, 3.5KB RAM, 176x184 3 bit color video Philipp Koehn Computer Systems Fundamentals: 6502 Introduction 18 September 2019 1982 6 • Commodore C64 • 64KB RAM, 320x200 4 bit color video Philipp Koehn Computer Systems Fundamentals: 6502 Introduction 18 September 2019 Commodore C64 7 • BASIC programming language, but serious programs written in assembly • No fancy stuff like multi-process, user accounts, virtual memory, etc. • Machine itself had no mass storage - had to buy tape drive, then floppy disk drive, machine was obsolete once hard drives came around Philipp Koehn Computer Systems Fundamentals: 6502 Introduction 18 September 2019 BASIC Demo 8 • Commands get executed (just like Python interpreter) -

Malware Detection Advances in Information Security

Malware Detection Advances in Information Security Sushil Jajodia Consulting Editor Center for Secure Information Systems George Mason University Fairfax, VA 22030-4444 email: ja jodia @ smu.edu The goals of the Springer International Series on ADVANCES IN INFORMATION SECURITY are, one, to establish the state of the art of, and set the course for future research in information security and, two, to serve as a central reference source for advanced and timely topics in information security research and development. The scope of this series includes all aspects of computer and network security and related areas such as fault tolerance and software assurance. ADVANCES IN INFORMATION SECURITY aims to publish thorough and cohesive overviews of specific topics in information security, as well as works that are larger in scope or that contain more detailed background information than can be accommodated in shorter survey articles. The series also serves as a forum for topics that may not have reached a level of maturity to warrant a comprehensive textbook treatment. Researchers, as well as developers, are encouraged to contact Professor Sushil Jajodia with ideas for books under this series. Additional titles in the series: ELECTRONIC POSTAGE SYSTEMS: Technology, Security, Economics by Gerrit Bleumer; ISBN: 978-0-387-29313-2 MULTIVARIATE PUBLIC KEY CRYPTOSYSTEMS by Jintai Ding, Jason E. Gower and Dieter Schmidt; ISBN-13: 978-0-378-32229-2 UNDERSTANDING INTRUSION DETECTION THROUGH VISUALIZATION by Stefan Axelsson; ISBN-10: 0-387-27634-3 QUALITY OF PROTECTION: Security Measurements and Metrics by Dieter Gollmann, Fabio Massacci and Artsiom Yautsiukhin; ISBN-10; 0-387-29016-8 COMPUTER VIRUSES AND MALWARE by John Aycock; ISBN-10: 0-387-30236-0 HOP INTEGRITY IN THE INTERNET by Chin-Tser Huang and Mohamed G. -

Installing the Educational Combo Disks

Installing the Educational Combo Disks Print this page out for reference while installing the emulator program and the Educational Combo Disks. Install AppleWin (Apple II Emulation Program for Windows) You may skip this page if you already have AppleWin properly installed. 1 - In your Documents Library create a new folder named “AppleWin” 2 - Click to follow this link: https://github.com/AppleWin/AppleWin 3 - Click download Version 1.25.0.3 (or latest version) 4 - When asked whether to download or save, click on “save.” The program will be saved in your Downloads file. 5 - Click “open” – a zipped folder will open 6 - Click “Extract all files”” – this will create a sub-folder AppleWin (+ version #) in your Documents folder. 7 - From this folder you may right-click the AppleWin application and then pin it to your start menu or Taskbar. You could also copy the shortcut and paste it to your desktop. 8 - Launch AppleWin by double-clicking on the AppleWin application. 9 - Read the GNU Public License information and click “I accept.” Install Educational Combo Disk Image 1 - In your AppleWin folder, open a new folder named “Educational Combo.” 2 - Use your Internet browser to go to http://www.Bible- prophecy.com/ron/software/educationalcombo/ 3 - A remote folder will open displaying two disk files. 4 - Click on the file (innerglo_educationalcombo_s1_dos33.dsk) 5 - A dialog box will open on the bottom of the page. Use the down-arrow next to “Save” to select “Save as.” 6 - Navigate to your Educational Combo folder and open it. Click “Save.” 7 - Return to the remote folder to transfer the other disk file. -

Appendix A: Microprocessor Data Sheets

Appendix A: Microprocessor Data Sheets Intel8085 Zilog Z80 MOS Technology 6502 Motorola 6809 Microcontrollers (Single-chip Microcomputers) Intel 8086 ( & 80186 & 80286) Zilog Z8000 Motorola 68000 32-bit Microprocessors lnmos Transputer 184 Appendix A 185 Intel 8085 Followed on from the 8080, which was a two-chip equivalent of the 8085. Not used in any home computers, but was extremely popular in early (late 1970s) industrial control systems. A15-A8 A B c D E Same register AD7-ADO H L set is used in SP 8080 PC ALE Flags Multiplexed d ata bus and lower half of address bus (require 8212 to split data and address buses) Start addresses of Interrupt P/Os Service Routines: 8155- 3 ports, 256 bytes RAM RESET-()()()(J 8255 - 3 ports TRAP- 0024 8355 - 2 ports, 2K ROM RST5.5- 002C 8755 - 2 ports, 2K EPROM RST6.5 - ()(J34 RST7.5- <XJ3C INTR - from interrupting device Other 8251- USART 8202 - Dynamic RAM controller support 8253- CTC (3 counters) 8257 - DMA controller devices: 8271 - FDC 8257 - CRT controller Intel DMA Control System Character CPU buses de-multiplexed Video signal to CRT 186 Microcomputer Fault-finding and Design Zilog Z80 Probably the most popular 8-bit microprocessor. Used in home computers (Spectrum, Amstrad, Tandy), office computers and industrial controllers. A F A' F' B c B' C' D E D' E' H L H' L' 8 data Interrupt Memory lines vector I refresh R Index register IX Index register IY (to refresh dynamic RAMI Stack pointer Based on the Intel 8085, but possesses second set of registers. -

Gbbs-Tcpser-Howto-01

This is a basic how-to on setting up an Internet-connected BBS using GBBS Pro and either a real or emulated Apple IIe or IIgs computer. For AppleWin users, the minimum required version is 1.26.3.0 – this version has an ACIA behavior fix that’s needed for GBBS Pro (or any other BBS package) to operate properly. You can find the latest version of AppleWin here: https://github.com/AppleWin/AppleWin In order to connect your real or virtual Apple IIe to the Internet, you’re going to need to set up a “modem emulator”. There’s a number of different choices out there, but for this how-to I’m going to cover one called tcpser. What tcpser does is act as a bridge between the Internet and your Apple IIe (or other vintage computer). As far as your Apple IIe is concerned, it’s talking to a real modem. Setting up a host for tcpser is pretty simple. I’m going to cover two methods that I’ve used myself. Note that tcpser can be built for Linux, Windows, and pretty much any BSD-derived operating system (OpenBSD, FreeBSD, NetBSD, Darwing, etc.) First will be a Raspberry Pi configuration and the second will be a Windows configuration. For the Raspberry Pi option, you’ll need the following items: • Raspberry Pi 3 • USB to Serial adapter – units that use the Prolific PL-2303 chipset are preferred and are known to work well. You can search Amazon for “Prolific PL2303” to see some good examples from the likes of Sabrent and Trendnet.