TMS320C6000 EMIF to USB Interfacing Using Cypress EZ-USB SX2

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

TJR-1197 Goodbye.Pdf

CYPRESS SEMICONDUCTOR CORPORATION Internal Correspondence Date: August 19, 2016 WW: 3316 To: All Cypress Employees Author: T.J. Rodgers Author File#: TJR#1197 Subject: Goodbye cc: BoD, Jim Collins, Larry Sonsini It’s 2:30 in the afternoon on August 17, my last official day at Cypress. After packing my stuff, I realized there were goodbyes to write. So, this won’t be a typical “TJ memo,” revised 10 times, logical and filled with fact-checked data; it will be more stream-of-consciousness in style. In a way, writing this memo is like talking to your wife of 34 years, while she’s on her deathbed. What do you say? I’ve enjoyed being with you? We’ve done a lot of good things together? There are really no appropriate words. But, perhaps there are. In the 1970 movie Patton, as the General leaves his command, he says, “Gentlemen, all good things must come to an end. And the best thing that has happened to me in my life has been the honor and privilege of commanding the 3rd Army. Goodbye, and God bless you.” This is the way I feel about Cypress. We have a lot to be proud of. Cypress was founded in December 1982, when there were 59 publically traded American chip companies. Today, only 15 of them are left—and we are one of the 15. That statement applies to every Cypress employee, whether you came from old Cypress, Spansion, Fujitsu, Broadcom or Ramtron. Each of us has made it in the industry for a long time; we all now fight together under one flag; and we’re all still around because we’ve earned the right to be. -

Pcn Wafer Foundry Site Qualification Template

Cypress Semiconductor Corporation, 198 Champion Court, San Jose, CA 95134. Tel: (408) 943-2600 PRODUCT CHANGE NOTIFICATION PCN: PCN170501 Date: February 28, 2017 Subject: Qualification of Texas Instruments’ DMOS6 as an Additional Wafer Fab Site, Cypress’ Test 25 as an Additional Wafer Sort Site for 2Mb F-RAM Serial Product Family To: FUTURE ELECTRONICS FUTURE ELE [email protected] Change Type: Major Description of Change: Cypress announces the qualification of Texas Instruments DMOS6 as an additional wafer fab site and Test 25 as an additional wafer sort site for its 2Mb F-RAM Serial Product Family. This qualification is part of the flexible manufacturing initiative which allows Cypress to meet its delivery commitments in dynamic, changing market conditions. Benefit of Change: By adding the DMOS6 and Test 25 sites, Cypress will have the added capability to meet upside market demand, and ensure consistent and reliable delivery to customers. Affected Parts: 6 Part Numbers Affected: See the attached ‘Affected Parts List’ file for a list of all part numbers affected by this change. Note that any new parts that are introduced after the publication of this PCN will include all changes outlined in this PCN. Qualification Status: The changes listed in this PCN have been qualified through a series of tests documented in the Qualification Test Plan (QTP) reports indicated in the table below. These qualification reports can be found as attachments to this notification or by visiting www.cypress.com and typing the QTP number in the keyword search window. Qualification QTP Report Number TI DMOS6 Wafer Fab for 64Kb F-RAM Serial Industrial-Grade 143905 FRAM Wafer Sort at Test 25 Site Sample Status: Qualification samples are not built ahead of time for all part numbers affected by this change. -

Exhibit 21.1 SUBSIDIARIES of CYPRESS SEMICONDUCTOR

Exhibit 21.1 SUBSIDIARIES OF CYPRESS SEMICONDUCTOR CORPORATION Name Jurisdiction of Incorporation Cypress Semiconductor Corporation United States Of America Cascade Semiconductor Corporation United States Of America CY Holding One LLC United States Of America CY Holding Two LLC United States Of America CY Support Mexico Cyland Corporation Philippines Cypress Manufacturing, Ltd. Cayman Islands Cypress Microsystems, Inc. United States Of America Cypress Semiconductor (China) Company Limited China Cypress Semiconductor (Luxembourg) Sarl Luxembourg Lara (CSC) -Mauritius LLC Mauritius Cypress Semiconductor (Minnesota) Inc. United States Of America Cypress Semiconductor (Scandinavia) AB Sweden Cypress Semiconductor (Switzerland) Sarl Switzerland Cypress Semiconductor (Texas) Inc. United States Of America Cypress Semiconductor (Thailand) Co., Ltd. Thailand Cypress Semiconductor (UK) Limited United Kingdom Cypress Semiconductor Canada Canada Cypress Semiconductor Corporation (Belgium) Belgium Cypress Semiconductor GmbH Germany Cypress Semiconductor Holding One LLC United States Of America Cypress Semiconductor International (Hong Kong) Limited Hong Kong Cypress Semiconductor International Sales B.V. Netherlands Cypress Semiconductor Intl Inc. United States Of America Cypress Semiconductor Ireland Ireland Cypress Semiconductor Italia S.r.l. Italy Cypress Semiconductor K.K. Japan Japan Cypress Semiconductor Korea Ltd. Korea Cypress Semiconductor Phil. Headquarters Ltd. Cayman Islands Cypress Semiconductor Procurement LLC United States Of America Cypress Semiconductor Round Rock, Inc. United States Of America Cypress Semiconductor SARL France Cypress Semiconductor Singapore Pte. Ltd Singapore Cypress Semiconductor Solutions Mexico Cypress Semiconductor Taiwan Taiwan Cypress Semiconductor Tech. India Ltd. India Cypress Semiconductor Technology (Shanghai) Co., Ltd. China Cypress Semiconductor Technology Ltd. Cayman Islands Cypress Semiconductor World Trade Corp. Cayman Islands Cypress EnviroSystems Corporation United States Of America Cypress Venture Fund I, L.L.C. -

Cadence Design Systems, Inc. 2020 Proxy Statement

NOTICE OF 2020 ANNUAL MEETING OF STOCKHOLDERS The 2020 Annual Meeting of Stockholders of CADENCE DESIGN SYSTEMS, INC., a Delaware corporation, will be held as follows: When: Where: April 30, 2020 Cadence San Jose Campus 1:00 p.m. Pacific Time 2655 Seely Avenue, Building 10 San Jose, California 95134 Items of Business: The purpose of the 2020 Annual Meeting of Stockholders is to consider and take action on the following: 1. To elect the nine directors named in the proxy statement to serve until the 2021 Annual Meeting of Stockholders and until their successors are elected and qualified, or until the directors’ earlier death, resignation or removal. 2. To approve the amendment of the Omnibus Equity Incentive Plan. 3. To vote on an advisory resolution to approve named executive officer compensation. 4. To ratify the selection of PricewaterhouseCoopers LLP as the independent registered public accounting firm of Cadence for its fiscal year ending January 2, 2021. 5. To vote on a stockholder proposal regarding special stockholder meetings, if properly presented at the meeting. 6. To transact such other business as may properly come before the meeting or any adjournment or postponement thereof. These items of business are more fully described in the proxy statement accompanying this notice. Record Date: Holders of Cadence Design Systems, Inc. common stock at the close of business on March 2, 2020 are entitled to notice of and to vote at the 2020 Annual Meeting of Stockholders and any adjournment or postponement thereof. How to Vote: Your vote is important to us. Please cast your vote promptly via the internet, telephone or mail. -

Cypress Semiconductor Corporation Corporate

CYPRESS SEMICONDUCTOR CORPORATION CORPORATE GOVERNANCE GUIDELINES A. RESPONSIBILITIES OF THE BOARD OF DIRECTORS 1. The primary responsibilities of the Board of Directors (the “Board”) are oversight, counseling and direction to the management of Cypress Semiconductor Corporation (also herein referred to as the “Corporation” or “Company”) in the interest and for the benefit of the Corporation's stockholders, and overseeing the Company’s adherence to corporate standards. The Board’s detailed responsibilities include: a. Selecting, regularly evaluating the performance of, and approving the compensation of the Chief Executive Officer and Section 16 senior executives; b. Planning for succession with respect to the position of Chief Executive Officer and monitoring management's succession planning for Section 16 senior executives; c. Reviewing and, where appropriate, approving the Corporation's major financial objectives, strategic and operating plans and actions; d. Overseeing the conduct of the Corporation's business to evaluate whether the business is being properly managed; and e. Overseeing the processes for maintaining the integrity of the Corporation with regards to its financial statements and other public disclosures, and compliance with law and ethics. The Board has delegated to the Chief Executive Officer, working with the other executive officers of the Corporation (herein referred to collectively as “Management”), the authority and responsibility for managing the business of the Corporation in a manner consistent with the standards and practices of the Corporation, and in accordance with any specific plans, instructions or directions of the Board. The Chief Executive Officer and Management are responsible to seek the advice and, in appropriate situations, the approval of the Board with respect to extraordinary actions to be undertaken by the Corporation. -

UNITED STATES DISTRICT COURT DISTRICT of DELAWARE XPOINT TECHNOLOGIES, INC., Plaintiff, V. MICROSOFT CORP., INTEL CORP., MARVEL

Case 1:09-cv-00628-SLR Document 925 Filed 07/28/11 Page 1 of 58 PageID #: 11799 UNITED STATES DISTRICT COURT DISTRICT OF DELAWARE XPOINT TECHNOLOGIES, INC., Plaintiff, v. MICROSOFT CORP., INTEL CORP., MARVELL TECHNOLOGY GROUP LTD., MARVELL SEMICONDUCTOR, INC., HEWLETT-PACKARD CO., CYPRESS SEMICONDUCTOR CORP., QUICKLOGIC CORP., QUALCOMM INC., FREESCALE SEMICONDUCTOR HOLDINGS I, LTD., FREESCALE SEMICONDUCTOR, INC., T- MOBILE USA, INC., HTC CORP., HTC AMERICA, INC., APPLE INC., SONY Civil Action No. 09-CV-00628 (SLR) ERICSSON MOBILE COMMUNICATIONS AB, SONY ERICSSON MOBILE DEMAND FOR JURY TRIAL COMMUNICATIONS (USA), INC., KONINKLIJKE PHILIPS ELECTRONICS N.V., PHILIPS ELECTRONICS NORTH THIRD AMENDED COMPLAINT FOR AMERICA CORP., LG ELECTRONICS, PATENT INFRINGEMENT INC., LG ELECTRONICS MOBILECOMM USA, INC., RESEARCH IN MOTION LTD., RESEARCH IN MOTION CORP., MOTOROLA, INC., PALM, INC., NVIDIA CORP., ADVANCED MICRO DEVICES, INC., DELL INC., TOSHIBA CORP., TOSHIBA AMERICA INFORMATION SYSTEMS, INC., ASUSTEK COMPUTER INC., ASUS COMPUTER INTERNATIONAL, ACER INC., ACER AMERICA CORP., CISCO SYSTEMS, INC., ZORAN CORP., AT&T MOBILITY LLC, CELLCO PARTNERSHIP, and SPRINT SPECTRUM, LP and NEXTEL OPERATIONS, INC., Defendants. {BMF-W0217694.} Case 1:09-cv-00628-SLR Document 925 Filed 07/28/11 Page 2 of 58 PageID #: 11800 1. Plaintiff Xpoint Technologies, Inc. (“Xpoint” or “Plaintiff”), by and through its attorneys, for its Complaint against Defendants Microsoft Corporation (“Microsoft”), Intel Corporation (“Intel”), Marvell Technology Group Ltd. (“Marvell Technology”), Marvell Semiconductor, Inc. (“Marvell Semiconductor”), Hewlett-Packard Company (“HP”), Cypress Semiconductor Corp. (“Cypress Semiconductor”), QuickLogic Corporation (“QuickLogic”), Qualcomm Inc. (“Qualcomm”), Freescale Semiconductor Holdings I, Ltd. (“Freescale Holdings”), Freescale Semiconductor, Inc. (“Freescale Semiconductor”), T-Mobile USA, Inc. -

Interfacing QDR II SRAM Devices with Virtex-6 Fpgas Author: Olivier Despaux XAPP886 (V1.0) December 2, 2010

Application Note: Virtex-6 Family Interfacing QDR II SRAM Devices with Virtex-6 FPGAs Author: Olivier Despaux XAPP886 (v1.0) December 2, 2010 Summary With an increasing need for lower latency and higher operating frequencies, memory interface IP is becoming more complex and needs to be tailored based on a number of factors such as latency, burst length, interface width, and operating frequency. The Xilinx® Memory Interface Generator (MIG) tool enables the creation of a large variety of memory interfaces for devices such as the Virtex®-6 FPGA. However, in the Virtex-6 FPGA, QDR II SRAM is not one of the options available by default. Instead, the focus has been on the QDR II+ technology using four-word burst access mode. This application note presents a Verilog reference design that has been simulated, synthesized, and verified on hardware using Virtex-6 FPGAs and QDR II SRAM two-word burst devices. Design Table 1 shows the salient features of the reference design. Characteristics Table 1: Reference Design Characteristics Parameter Description RTL language Verilog QDR SRAM part reference number Cypress Semiconductor CY7C1412BV18, Samsung Electronics K7R321882C Reference design LUT utilization for 18-bit 1,247 read/write Slice register utilization for 18-bit read/write 1,866 Synthesis XST 12.2 Simulation ISim 12.2 Implementation tools ISE® Design Suite 12.2 MIG software version MIG 3.4 Total number of I/O blocks (IOBs) for complete 72 (data, address, control, clock, and test reference design signals) XPower Analyzer power estimation 1.04W dynamic power Design The reference design is based on a MIG 3.4 QDR II+ four-word burst design. -

A Decade of Semiconductor Companies : 1988 Edition

1988 y DataQuest Do Not Remove A. Decade of Semiconductor Companies 1988 Edition Components Division TABLE OF CONTENTS Page I. Introduction 1 II. Venture Capital 11 III. Strategic Alliances 15 IV. Product Analysis 56 Emerging Technology Companies 56 Analog ICs 56 ASICs 58 Digital Signal Processing 59 Discrete Semiconductors 60 Gallium Arsenide 60 Memory 62 Microcomponents 64 Optoelectronics 65 Telecommunication ICs 65 Other Products 66 Bubble Memory 67 V. Company Profiles (139) 69 A&D Co., Ltd. 69 Acrian Inc. 71 ACTEL Corporation 74 Acumos, Inc. 77 Adaptec, Inc. 79 Advanced Linear Devices, Inc. 84 Advanced Microelectronic Products, Inc. 87 Advanced Power Technology, Inc. 89 Alliance Semiconductor 92 Altera Corporation 94 ANADIGICS, Inc. 100 Applied Micro Circuits Corporation 103 Asahi Kasei Microsystems Co., Ltd. 108 Aspen Semiconductor Corporation 111 ATMEL Corporation 113 Austek Microsystems Pty. Ltd. 116 Barvon Research, Inc. 119 Bipolar Integrated Technology 122 Brooktree Corporation 126 California Devices, Ihc. 131 California Micro Devices Corporation 135 Calmos Systems, Inc. 140 © 1988 Dataquest Incorporated June TABLE OF CONTENTS (Continued) Pagg Company Profiles (Continued) Calogic Corporation 144 Catalyst Semiconductor, Inc. 146 Celeritek, Inc. ISO Chartered Semiconductor Pte Ltd. 153 Chips and Technologies, Inc. 155 Cirrus Logic, Inc. 162 Conductus Inc. 166 Cree Research Inc. 167 Crystal Semiconductor Corporation 169 Custom Arrays Corporation 174 Custom Silicon Inc. 177 Cypress Semiconductor Corporation 181 Dallas Semiconductor Corporation 188 Dolphin Integration SA 194 Elantec, Inc. 196 Electronic Technology Corporation 200 Epitaxx Inc. 202 European Silicon Structures 205 Exel Microelectronics Inc. 209 G-2 Incorporated 212 GAIN Electronics 215 Gazelle Microcircuits, Inc. 218 Genesis Microchip Inc. -

Patent Landscape Shifts from M&A in the Semiconductor Industry

® Patent Landscape Shifts from M&A in the Semiconductor Industry George Park Great things 8 April 2021 happen when ideas prosper Property of IPValue Management Inc. – All rights reserved. The views expressed do not necessarily represent the views of IPValue. Semiconductor industry experienced a boom in M&A in the last two years Technology area of company or business Date deal Buyer Seller Deal Value unit being acquired announced Renesas Dialog Semiconductor $5.9B Internet of Things, Mixed Signal Feb-21 Qualcomm Nuvia $1.4B Custom CPU core design for servers Jan-21 AMD Xilinx $35B Programmable chips Oct-20 SK hynix Intel NAND/SSD business unit $9B NAND/SSD Oct-20 High-speed interconnect and mixed- Marvell Inphi $10B Oct-20 signal IC Nvidia ARM (owned by Softbank) $40B Processor design technology Sep-20 Analog Devices Maxim $21B Analog & mixed signal products Jul-20 AMS OSRAM €4.6B Lighting technology Dec-19 Apple Intel business unit $1B Smartphone modem Jul-19 MCUs, software, connectivity Infineon Cypress Semiconductor €9B Jun-19 components Marvell wireless connectivity NXP Semiconductors $1.76B WiFi and Bluetooth May-19 business unit ON Semiconductor Quantenna $1B WiFi Mar-19 Nvidia Mellanox $7B High performance networking technology Mar-19 Note: certain deals, including Nvidia-ARM, remain subject to governmental approval Source: IAM-Media; press releases Property of IPValue Management Inc. – All rights reserved. 2 SOXX Performance: Jan 2019 to Dec 2020 Source: Yahoo Property of IPValue Management Inc. – All rights reserved. 3 Total 2020 M&A deals in the semiconductor space has been estimated at ~$100B Source: Press releases Property of IPValue Management Inc. -

Cypress Semiconductor Corp.)

Case Study for Valuing a Cyclical Stock (Cypress Semiconductor Corp.) A good overview of the business circa 2002 with price/sales graphs and industry statistics placed into context: http://www.cypress.com/?rID=34960 Cypress President T.J. Rodgers Communicates to Shareholders and Employees Regarding Cypress Share Price Last Updated: 05/24/2012 Contact: Joe McCarthy VP Communications (408) 943-2902 [email protected] For Immediate Release Cypress President T.J. Rodgers Communicates to Shareholders and Employees Regarding Cypress Share Price SAN JOSE, Calif., October 8, 2002 – Cypress Semiconductor Corporation (NYSE: CY) President and CEO T. J. Rodgers today released a communication to Cypress shareholders and employees providing details about the recent fluctuations in Cypress’ share price. A copy of that communication follows. A SPECIAL LETTER TO CYPRESS SHAREHOLDERS AND EMPLOYEES To Our Shareholders: www.csinvesting.wordpress.com studying/teaching/investing Page 1 Case Study for Valuing a Cyclical Stock (Cypress Semiconductor Corp.) Last Friday, Cypress shares dropped to an unprecedented $4 per share. As you might imagine we had numerous phone calls and emails. I have decided that this unprecedented event warrants a special shareholder letter. I have enclosed two emails I received along with my response to them. The first email is from an investor whose retirement fund contains Cypress stock. Subject: Concerned Shareholder Dear Mr. Rodgers, I own 10,000 shares of Cypress in my retirement account. The shares were purchased at $11/share. Having the vast majority of my IRA invested in Cypress, I’m naturally concerned with the huge drop in the stock price. What is your level of confidence that the shares will recover in value over the next few years? Does Cypress have the financial strength to survive until the economy recovers? You have always struck me as an honest business leader. -

Semiconductors

SEMICONDUCTORS MCU/MPU/DSP Murata .................................371 Infineon ............................560, 561 Analog Devices Inc. ...........187, 188, 189, 190 NXP Semiconductor ............. 372, 373, 374, MA-COM ...............................562 Cypress Semiconductor .......191, 192, 193, 194 . 375, 376, 377 NXP Semiconductor ..................563, 564 Freescale Semiconductor ..... 195, 196, 197, 198, ON Semiconductor ...............378, 379, 380 ON Semiconductor ...........565, 566, 567, 568 . 199, 200, 201, 202, 203, Plessey ................................381 Panasonic Semiconductor ..........569, 570, 571 . 204, 205, 206, 207, 208 Silicon Labs .............................382 Power Integrations. 572 FTDI ...................................209 Vishay / Siliconix .................410, 411, 412 Skyworks ...........................573, 574 Intel ...........................210, 211, 212 Skyworks ...........................383, 384 STMicroelectronics ...................575, 576 Microchip Technology ............ 213, 214, 215, STMicroelectronics .......385, 386, 387, 388, 389 Vishay General Semiconductor ......... 577, 578, . 216, 217, 218 Texas Instruments ........... 390, 391, 392, 393, . 579, 580 NXP Semiconductors .........219, 220, 221, 222 . 394, 395, 396, 397, 398, 399, 400, 401, Vishay Semiconductors. 581, 582, 583, Silicon Labs .........223, 224, 225, 226, 227, 228 . 402, 403, 404, 405, 406, 407, 408, 409 . 584, 585, 586 STMicroelectronics ...............229, 230, 231 Amplifier ICs Transistors Olimex Ltd ..............................232 -

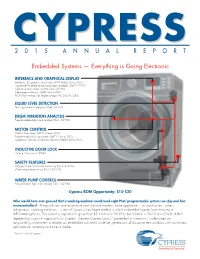

2 0 1 5 a N N U a L R E P O

2015 ANNUAL REPORT Embedded Systems — Everything is Going Electronic INTERFACE AND GRAPHICAL DISPLAY Hardware 2D graphics accelerator (FM4 S6E2D Series MCU) CapSense® enabled buttons and rotary encoder (PSoC® 4200L) CapSense touchscreen control (PSoC 4100S) Stable power delivery (S6AP Series PMIC) NOR Flash memory for display images (FL128S/KL128S) LIQUID LEVEL DETECTION Fourth-generation CapSense (PSoC 4100S) DRUM VIBRATION ANALYSIS Programmable digital and analog (PSoC 4200M) MOTOR CONTROL Multi-function timers (S6E2H Series MCU) Programmable pulse generators (S6E2H Series MCU) Quadrature position/revolution counters (S6E2H Series MCU) INDUCTIVE DOOR LOCK Analog Coprocessor (PSoC) SAFETY FEATURES Voltage/Current hardware monitoring (PSoC 4200M) Water temperature sensor (PSoC 4200M) WATER PUMP CONTROL Programmable digital and analog (PSoC 4200M) Cypress BOM Opportunity: $15-$20 Who would have ever guessed that a washing machine would need eight PSoC programmable systems-on-chip and four microcontrollers? Along with our core automotive and industrial markets, home appliances—air conditioners, stoves, refrigerators, washing machines—is one of Cypress’s key target markets in which embedded systems have become a differentiating factor. This market is expected to grow from $3.1 billion in 2015 to $4.3 billion in 2019 at a CAGR of 8%*, representing a growth opportunity for Cypress. The new Cypress brand, “Embedded in Tomorrow,” underscores our longstanding commitment to enable our embedded customers to deliver generations of disruptive new products with world-class performance, reliability and time to market. *Source: IHS and Cypress CYPRESS USB TYPE-C: MAKING USB UNIVERSAL® The USB Type-C standard enables the transfer of power, display and data to PCs, smartphones and tablets and replaces multiple connectors with a single connector.