Cadence Design Systems, Inc. 2020 Proxy Statement

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Cadence SPB / Orcad 17.4 System Requirements

A Parallel Systems Technical Note Cadence SPB / OrCAD 17.4 System Requirements Supported Operating Systems Windows 10 (64-bit) Professional, including Dark Theme mode Windows Server 2012 (All Service Packs) Windows Server 2012 R2 Windows Server 2016 Note: Cadence Allegro and OrCAD products do not support Windows 10 Starter and Home Basic. In addition, Windows Server support does not include support for Windows Remote Desktop. Windows RT and Tablets/Phones, including Windows 10 Phone, are not supported. Note: 64-bit Windows require 64-bit Flex software dongle drivers if using dongle-based licensing. Recommended Hardware Intel® Core™ i7 4.30 GHz or AMD Ryzen™ 7 4.30 GHz with at least 4 cores Note: Faster processors are preferred. 16 GB RAM 50 GB free disk space (SSD drive is recommended) 1920 x 1200 display resolution with true color (at least 32bit colour) A dedicated graphics card supporting OpenGL, minimum 2GB (with additional support for DX11 for 3D Canvas) Dual monitors (For physical design) Broadband Internet connection for some service Ethernet port/card (for network communications and security hostID) Three-button Microsoft-compatible mouse Supported MATLAB Version R2019A-64Bit (For the PSpice-MATLAB interface) Microsoft SharePoint for Allegro Pulse Cadence® Allegro® Pulse supports an interface to Microsoft SharePoint. Following are the requirements for SharePoint: • Windows Server 2012 (64-bit) • SharePoint Foundation 2013 • Microsoft SQL Server 2012 (64-bit) • Following 64-bit browsers: • Microsoft® Internet Explorer® 11.0 on windows • Mozilla Firefox 52.0 ESR on Windows • Mozilla Firefox 52.0 on Linux • Google Chrome 58.0 on Windows Using Spaces in File and Directory Names Support for spaces in file and directory names applies only to Windows. -

The Evolving Role of Semiconductor Consortia in the United States and Japan

Portland State University PDXScholar Business Faculty Publications and Presentations The School of Business Fall 1998 The Evolving Role of Semiconductor Consortia in the United States and Japan Rose Marie Ham University of California - Berkeley Greg Linden University of California - Berkeley Melissa M. Appleyard Portland State University, [email protected] Follow this and additional works at: https://pdxscholar.library.pdx.edu/busadmin_fac Part of the Business Administration, Management, and Operations Commons Let us know how access to this document benefits ou.y Citation Details Ham, R., Linden, G., & Appleyard, M. M. (1998). The Evolving Role of Semiconductor Consortia in the United States and Japan. California Management Review, 41(1), 137-163. This Article is brought to you for free and open access. It has been accepted for inclusion in Business Faculty Publications and Presentations by an authorized administrator of PDXScholar. Please contact us if we can make this document more accessible: [email protected]. The Evolving Role of Semiconductor Consortia in the United States and Japan Rose Marie Ham Greg Linden Melissa M. Appleyard ince the late 1970s, governments throughout the industrialized economics have proclaimed the benefits of research consortia. In the United States, tor example, ihe 1984 National Cooperative Research SAct (NCRA) relaxed U.S. antitrust laws to encourage the formation of research consortia hy firms in the same industry; by the end of 1995, over 575 consortia had heen registered under the NCRA in a variety of -

Portfolio Holdings Listing Select Semiconductors Portfolio As of June

Portfolio Holdings Listing Select Semiconductors Portfolio DUMMY as of August 31, 2021 The portfolio holdings listing (listing) provides information on a fund’s investments as of the date indicated. Top 10 holdings information (top 10 holdings) is also provided for certain equity and high income funds. The listing and top 10 holdings are not part of a fund’s annual/semiannual report or Form N-Q and have not been audited. The information provided in this listing and top 10 holdings may differ from a fund’s holdings disclosed in its annual/semiannual report and Form N-Q as follows, where applicable: With certain exceptions, the listing and top 10 holdings provide information on the direct holdings of a fund as well as a fund’s pro rata share of any securities and other investments held indirectly through investment in underlying non- money market Fidelity Central Funds. A fund’s pro rata share of the underlying holdings of any investment in high income and floating rate central funds is provided at a fund’s fiscal quarter end. For certain funds, direct holdings in high income or convertible securities are presented at a fund’s fiscal quarter end and are presented collectively for other periods. For the annual/semiannual report, a fund’s investments include trades executed through the end of the last business day of the period. This listing and the top 10 holdings include trades executed through the end of the prior business day. The listing includes any investment in derivative instruments, and excludes the value of any cash collateral held for securities on loan and a fund’s net other assets. -

GS40 0.11-Μm CMOS Standard Cell/Gate Array

GS40 0.11-µm CMOS Standard Cell/Gate Array Version 1.0 January 29, 2001 Copyright Texas Instruments Incorporated, 2001 The information and/or drawings set forth in this document and all rights in and to inventions disclosed herein and patents which might be granted thereon disclosing or employing the materials, methods, techniques, or apparatus described herein are the exclusive property of Texas Instruments. No disclosure of information or drawings shall be made to any other person or organization without the prior consent of Texas Instruments. IMPORTANT NOTICE Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability. TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI’s standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this war- ranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements. Certain applications using semiconductor products may involve potential risks of death, personal injury, or severe property or environmental damage (“Critical Applications”). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WAR- RANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. -

LPC47N267 Product Brief

LPC47N267 100-Pin LPC Super I/O with X-Bus Interface Product Features • Enhanced Digital Data Separator - 2 Mbps, 1 Mbps, 500 Kbps, 300 Kbps, 250 • 3.3 Volt Operation (5V tolerant) Kbps Data Rates • Programmable Wakeup Event Interface - Programmable Precompensation Modes (IO_PME# Pin) • Serial Ports • SMI Support (IO_SMI# Pin) - Two Full Function Serial Ports • GPIOs (29) - High Speed NS16C550 Compatible UARTs • Four IRQ Input Pins with Send/Receive 16-Byte FIFOs • X-Bus Interface - Supports 230k and 460k Baud - Supports up to 4 external components - Programmable Baud Rate Generator - Supports I/O cycles (No Memory Support) - Modem Control Circuitry - 8-Bit Data Transfer • Infrared Communications Controller - 16-Bit Address Qualification - IrDA v1.2 (4Mbps), HPSIR, ASKIR, Con- - Write Protection for each component sumer IR Support • XNOR Chain -2 IR Ports • PC99 and ACPI 1.0b Compliant - 96 Base I/O Address, 15 IRQ Options and 3 • 100-pin STQFP Package DMA Options • Intelligent Auto Power Management • Multi-Mode Parallel Port with ChiProtect • 2.88MB Super I/O Floppy Disk Controller - Standard Mode IBM PC/XT, PC/AT, and PS/2 - Licensed CMOS 765B Floppy Disk Controller Compatible Bidirectional Parallel Port - Software and Register Compatible with - Enhanced Parallel Port (EPP) Compatible - Microchip's Proprietary 82077AA Compatible EPP 1.7 and EPP 1.9 (IEEE 1284 Compliant) Core - IEEE 1284 Compliant Enhanced Capabilities - Supports One Floppy Drive Directly Port (ECP) - Configurable Open Drain/Push-Pull Output - ChiProtect Circuitry for -

Microchip Technology Announces Financial Results for Third Quarter of Fiscal Year 2020

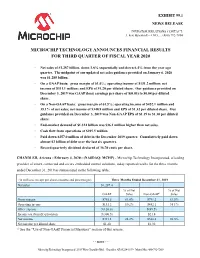

EXHIBIT 99.1 NEWS RELEASE INVESTOR RELATIONS CONTACT: J. Eric Bjornholt -- CFO..... (480) 792-7804 MICROCHIP TECHNOLOGY ANNOUNCES FINANCIAL RESULTS FOR THIRD QUARTER OF FISCAL YEAR 2020 ◦ Net sales of $1.287 billion, down 3.8% sequentially and down 6.4% from the year ago quarter. The midpoint of our updated net sales guidance provided on January 6, 2020 was $1.285 billion. ◦ On a GAAP basis: gross margin of 61.0%; operating income of $131.2 million; net income of $311.1 million; and EPS of $1.20 per diluted share. Our guidance provided on December 3, 2019 was GAAP (loss) earnings per share of $(0.03) to $0.04 per diluted share. ◦ On a Non-GAAP basis: gross margin of 61.5%; operating income of $452.1 million and 35.1% of net sales; net income of $340.8 million and EPS of $1.32 per diluted share. Our guidance provided on December 3, 2019 was Non-GAAP EPS of $1.19 to $1.30 per diluted share. ◦ End-market demand of $1.324 billion was $36.1 million higher than net sales. ◦ Cash flow from operations of $395.5 million. ◦ Paid down $257.0 million of debt in the December 2019 quarter. Cumulatively paid down almost $2 billion of debt over the last six quarters. ◦ Record quarterly dividend declared of 36.70 cents per share. CHANDLER, Arizona - February 4, 2020 - (NASDAQ: MCHP) - Microchip Technology Incorporated, a leading provider of smart, connected and secure embedded control solutions, today reported results for the three months ended December 31, 2019 as summarized in the following table: (in millions, except per share amounts and percentages) Three Months Ended December 31, 2019 Net sales $1,287.4 % of Net % of Net GAAP Sales Non-GAAP1 Sales Gross margin $785.5 61.0% $791.2 61.5% Operating income $131.2 10.2% $452.1 35.1% Other expense $(120.6) $(89.5) Income tax (benefit) provision $(300.5) $21.8 Net income $311.1 24.2% $340.8 26.5% Net income per diluted share $1.20 $1.32 (1) See the "Use of Non-GAAP Financial Measures" section of this release. -

AN2534 PAC193X Integration Notes for Microsoft® Windows® 10 Driver Support Author: Razvan Ungureanu TABLE 2: REVISION HISTORY Microchip Technology Inc

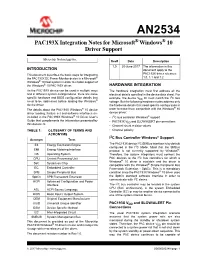

AN2534 PAC193X Integration Notes for Microsoft® Windows® 10 Driver Support Author: Razvan Ungureanu TABLE 2: REVISION HISTORY Microchip Technology Inc. Rev# Date Description 1.0 20-June-2017 The information in this INTRODUCTION document apply to the This document describes the basic steps for integrating PAC193X driver releases: the PAC193X DC Power Monitor device in a Microsoft® 1.0, 1.1 and 1.2 Windows® 10 host system in order to enable support of the Windows® 10 PAC193X driver. HARDWARE INTEGRATION As the PAC193X device can be used in multiple ways The hardware integration must first address all the and in different system configurations, there are some electrical details specified in the device data sheet. For 2 specific hardware and BIOS configuration details that example, the device VDD IO must match the I C bus need to be addressed before loading the Windows® voltage. But the following hardware notes address only device driver. the hardware details that need specific configuration in ® The details about the PAC193X Windows® 10 device order to make them compatible with the Windows 10 driver loading, feature set and software interfaces are device driver: included in the PAC193X Windows® 10 Driver User’s •I2C bus controller Windows® support Guide that complements the information presented by • PAC193X VDD and SLOW/ALERT pin connections this document. • Channel shunt resistor values . TABLE 1: GLOSSARY OF TERMS AND • Channel polarity ACRONYMS I2C Bus Controller Windows® Support Acronym Term 2 E3 Energy Estimation Engine The PAC193X device I C/SMBus interface is by default configured in the I2C Mode. Mind that the SMBus EMI Energy Metering Interface protocol is not currently supported by Windows®. -

Stoxx® Global Automation & Robotics Index

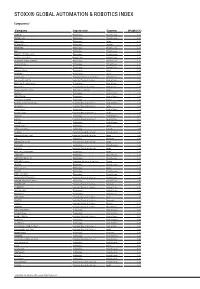

STOXX® GLOBAL AUTOMATION & ROBOTICS INDEX Components1 Company Supersector Country Weight (%) SNAP 'A' Technology United States 4.24 NVIDIA Corp. Technology United States 2.80 Nidec Corp. Technology Japan 2.42 HEXAGON B Technology Sweden 2.38 TERADYNE Technology United States 2.31 KLA Technology United States 2.23 MARVELL TECHNOLOGY Technology United States 2.16 Intuitive Surgical Inc. Health Care United States 2.12 ADVANCED MICRO DEVICES Technology United States 2.12 Qualcomm Inc. Technology United States 2.09 Apple Inc. Technology United States 2.06 Advantest Corp. Technology Japan 2.05 LASERTEC Technology Japan 2.04 Garmin Ltd. Consumer Products & Services United States 2.02 Emerson Electric Co. Industrial Goods & Services United States 2.02 Microchip Technology Inc. Technology United States 1.98 Ametek Inc. Industrial Goods & Services United States 1.96 Toyota Industries Corp. Automobiles & Parts Japan 1.96 Xilinx Inc. Technology United States 1.95 SERVICENOW Technology United States 1.88 DASSAULT SYSTEMS Technology France 1.82 Rockwell Automation Corp. Industrial Goods & Services United States 1.74 Fanuc Ltd. Industrial Goods & Services Japan 1.74 Autodesk Inc. Technology United States 1.68 Keyence Corp. Industrial Goods & Services Japan 1.63 Ansys Inc. Technology United States 1.61 HALMA Industrial Goods & Services Great Britain 1.56 PTC INC Technology United States 1.53 Omron Corp. Technology Japan 1.52 OPEN TEXT (NAS) Technology Canada 1.49 COGNEX Industrial Goods & Services United States 1.48 Yaskawa Electric Corp. Industrial Goods & Services Japan 1.40 SAP Technology Germany 1.40 MINEBEA MITSUMI Industrial Goods & Services Japan 1.24 Intel Corp. -

TJR-1197 Goodbye.Pdf

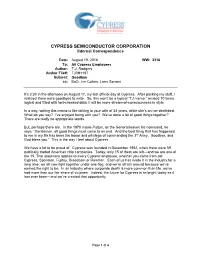

CYPRESS SEMICONDUCTOR CORPORATION Internal Correspondence Date: August 19, 2016 WW: 3316 To: All Cypress Employees Author: T.J. Rodgers Author File#: TJR#1197 Subject: Goodbye cc: BoD, Jim Collins, Larry Sonsini It’s 2:30 in the afternoon on August 17, my last official day at Cypress. After packing my stuff, I realized there were goodbyes to write. So, this won’t be a typical “TJ memo,” revised 10 times, logical and filled with fact-checked data; it will be more stream-of-consciousness in style. In a way, writing this memo is like talking to your wife of 34 years, while she’s on her deathbed. What do you say? I’ve enjoyed being with you? We’ve done a lot of good things together? There are really no appropriate words. But, perhaps there are. In the 1970 movie Patton, as the General leaves his command, he says, “Gentlemen, all good things must come to an end. And the best thing that has happened to me in my life has been the honor and privilege of commanding the 3rd Army. Goodbye, and God bless you.” This is the way I feel about Cypress. We have a lot to be proud of. Cypress was founded in December 1982, when there were 59 publically traded American chip companies. Today, only 15 of them are left—and we are one of the 15. That statement applies to every Cypress employee, whether you came from old Cypress, Spansion, Fujitsu, Broadcom or Ramtron. Each of us has made it in the industry for a long time; we all now fight together under one flag; and we’re all still around because we’ve earned the right to be. -

Timeline of the Semiconductor Industry in South Portland

Timeline of the Semiconductor Industry in South Portland Note: Thank you to Kathy DiPhilippo, Executive Director/Curator of the South Portland Historical Society and Judith Borelli, Governmental Relations of Texas Inc. for providing some of the information for this timeline below. Fairchild Semiconductor 1962 Fairchild Semiconductor (a subsidiary of Fairchild Camera and Instrument Corp.) opened in the former Boland's auto building (present day Back in Motion) at 185 Ocean Street in June of 1962. They were there only temporarily, as the Western Avenue building was still being constructed. 1963 Fairchild Semiconductor moves to Western Avenue in February 1963. 1979 Fairchild Camera and Instrument Corp. is acquired/merged with Schlumberger, Ltd. (New York) for $363 million. 1987 Schlumberger, Ltd. sells its Fairchild Semiconductor Corp. subsidiary to National Semiconductor Corp. for $122 million. 1997 National Semiconductor sells the majority ownership interest in Fairchild Semiconductor to an investment group (made up of Fairchild managers, including Kirk Pond, and Citcorp Venture Capital Ltd.) for $550 million. Added Corporate Campus on Running Hill Road. 1999 In an initial public offering in August 1999, Fairchild Semiconductor International, Inc. becomes a publicly traded corporation on the New York Stock Exchange. 2016 Fairchild Semiconductor International, Inc. is acquired by ON Semiconductor for $2.4 billion. National Semiconductor 1987 National Semiconductor acquires Fairchild Semiconductor Corp. from Schlumberger, Ltd. for $122 million. 1995 National Semiconductor breaks ground on new 200mm factory in December 1995. 1996 National Semiconductor announces plans for a $600 million expansion of its facilities in South Portland; construction of a new wafer fabrication plant begins. 1997 Plant construction for 200mm factory completed and production starts. -

Pcn Wafer Foundry Site Qualification Template

Cypress Semiconductor Corporation, 198 Champion Court, San Jose, CA 95134. Tel: (408) 943-2600 PRODUCT CHANGE NOTIFICATION PCN: PCN170501 Date: February 28, 2017 Subject: Qualification of Texas Instruments’ DMOS6 as an Additional Wafer Fab Site, Cypress’ Test 25 as an Additional Wafer Sort Site for 2Mb F-RAM Serial Product Family To: FUTURE ELECTRONICS FUTURE ELE [email protected] Change Type: Major Description of Change: Cypress announces the qualification of Texas Instruments DMOS6 as an additional wafer fab site and Test 25 as an additional wafer sort site for its 2Mb F-RAM Serial Product Family. This qualification is part of the flexible manufacturing initiative which allows Cypress to meet its delivery commitments in dynamic, changing market conditions. Benefit of Change: By adding the DMOS6 and Test 25 sites, Cypress will have the added capability to meet upside market demand, and ensure consistent and reliable delivery to customers. Affected Parts: 6 Part Numbers Affected: See the attached ‘Affected Parts List’ file for a list of all part numbers affected by this change. Note that any new parts that are introduced after the publication of this PCN will include all changes outlined in this PCN. Qualification Status: The changes listed in this PCN have been qualified through a series of tests documented in the Qualification Test Plan (QTP) reports indicated in the table below. These qualification reports can be found as attachments to this notification or by visiting www.cypress.com and typing the QTP number in the keyword search window. Qualification QTP Report Number TI DMOS6 Wafer Fab for 64Kb F-RAM Serial Industrial-Grade 143905 FRAM Wafer Sort at Test 25 Site Sample Status: Qualification samples are not built ahead of time for all part numbers affected by this change. -

Designcon 2016 Needs and Capabilities for Modeling Of

DesignCon 2016 Needs and Capabilities for Modeling of Capacitor Derating Panel discussion Brad Brim, Cadence Design Systems Istvan Novak, Oracle Tim Michalka, Qualcomm Technologies Wilmer Companioni, KEMET Electronics Shoji Tsubota, Murata Manufacturing Sam Chitwood, Cadence Design Systems Abstract Capacitors vary with temperature, bias voltage and age; a phenomenon typically referred to as derating. Libraries of SPICE or S-parameter models are provided by component manufacturers for non-derated components - new capacitors at a specific temperature and bias. Detailed derating data and related methodologies are often considered manufacturer-proprietary. Some manufacturers provide software to generate and display derated models while others specify general derating behavior in data sheets. OEMs have expressed a desire for more detailed and automated power integrity analyses to consider derating effects. Representatives from component manufacturers, OEMs and EDA will discuss these analysis needs and the electrical models required to support such. Audience participation is strongly encouraged to help judge the breadth of industry need in this area and help influence future contributions. TITLE Needs and Capabilities for Modeling of Capacitor Derating Moderator: Image Brad Brim (Cadence) Participants: Istvan Novak (Oracle) Tim Michalka (Qualcomm) Wilmer Companioni (KEMET) Shoji Tsubota (Murata) Sam Chitwood (Cadence) Needs and Capabilities for Modeling of Capacitor Derating Brad Brim (Cadence) 1 Moderator Brad Brim Product Engineering Architect, Cadence Design Systems [email protected] Brad has been in the EDA industry for more than 25 years. His graduate studies and initial commercial contributions were in the area of electromagnetic simulation and passive component modeling for circuit simulation. Some of the products he has worked on include: Momentum, ADS, HFSS, PowerSI and OptimizePI.