ON Semiconductor Is an Equal Opportunity/Affirmative Action Employer

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Designcon 2013

DesignCon 2013 Dramatic Noise Reduction using Guard Traces with Optimized Shorting Vias Eric Bogatin, Bogatin Enterprises [email protected] Lambert (Bert) Simonovich, Lamsim Enterprises Inc. [email protected] 1 Abstract Guard traces are sometimes used in high-speed digital and mixed signal applications to reduce the noise coupled from an aggressor transmission line to a victim line. Sometimes guard traces are effective, and sometime they are not, depending on the topology and end connections to the guard trace. Optimized design guidelines for using guard traces in both microstrip and stripline transmission line topologies are identified based on the mechanisms by which they reduce cross talk. By correct management of the ends of the guard trace, a guard trace can reduce coupled noise on a victim line by an order of magnitude over not having the guard trace present. However, if the guard trace is not optimized, the cross talk on the victim line can also be larger with the guard trace, than without. Author(s) Biography Eric Bogatin received his BS in physics from MIT and MS and PhD in physics from the University of Arizona in Tucson. He has held senior engineering and management positions at Bell Labs, Raychem, Sun Microsystems, Ansoft and Interconnect Devices. Eric has written 6 books on signal integrity and interconnect design and over 300 papers. His latest book, Signal and Power Integrity- Simplified, was published in 2009 by Prentice Hall. He is currently a signal integrity evangelist with Bogatin Enterprises, a wholly owned subsidiary of Teledyne LeCroy. He is also an Adjunct Associate Professor in the ECEE department of University of Colorado, Boulder. -

Modeling of the Substrate Coupling Path for Direct Power Injection in Integrated Circuits

Modeling of the Substrate Coupling Path for Direct Power Injection in Integrated Circuits Ali Alaeldine∗†, Richard Perdriau∗, Mohamed Ramdani∗, Etienne Sicard‡, M’hamed Drissi† and Ali M. Haidar§ ∗ESEO-LATTIS - 4, rue Merlet-de-la-Boulaye - BP 30926 - 49009 Angers Cedex 01 - France (e-mail : [email protected]) †IETR - INSA de Rennes - 20, avenue des Buttes de Coësmes - 35043 Rennes Cedex - France ‡LATTIS - INSA de Toulouse - 135, avenue de Rangueil - 31077 Toulouse Cedex 04 - France §Dept. of Computer Eng. and Informatics - Faculty of Engineering - Beirut Arab University - PO Box 11-5020 - Lebanon Abstract—This paper presents a substrate coupling path model Therefore, this paper aims at introducing suitable simulation for the direct power injection (DPI) of EMI disturbances into models for different EMI protection strategies in ICs, with the substrate of an integrated circuit (IC). This modeling is comparisons between simulations and measurements. For that achieved on a 0.18 µm test chip composed of several functionally identical cores, differing only by their EMI protection strategies purpose, a special test chip (CESAME) [8] will be used. (RC protection, isolated substrate), and takes into account these The paper is organized as follows. First of all, the internal different strategies. The comparison between simulation results structure of the CESAME test chip is introduced in Sect. and related measurements demonstrates that, once combined II. Then, Sect. III presents the DPI measurement set-up used with the complete model of the injection set-up itself, these in this study, along with its simulation model. The different models are helpful to choose the best protection strategy against electromagnetic disturbances. -

Substrate Crosstalk Suppression Using Wafer-Level Packaging: Metalized Through-Substrate Trench Approach

Substrate Crosstalk Suppression Using Wafer-Level Packaging: Metalized Through-Substrate Trench Approach Saoer Maniur SINAGA Substrate Crosstalk Suppression Using Wafer-Level Packaging Technique: Metalized Through-Substrate Trench Approach PROEFSCHRIFT ter verkrijging van de graad van doctor aan de Technische Universiteit Delft, op gezag van de Rector Magni¯cus Prof. ir. K. Ch. A. M. Luyben, voorzitter van het College voor Promoties, in het openbaar te verdedigen op woensdag 6 oktober 2010 om 10.00 uur door Saoer Maniur SINAGA Master of Science in Communication Engineering, UniversitÄatKassel, geboren te Medan, IndonesiÄe. Dit proefschrift is goedgekeurd door de promotor: Prof. dr. J. N. Burghartz Samenstelling promotiecommissie: Rector Magni¯cus, voorzitter Prof. dr. J. N. Burghartz, Technische Universiteit Delft, promotor Dr. M. Bartek, Technische Universiteit Delft, co-promotor Prof. dr. P. M. Sarro, Technische Universiteit Delft Prof. dr. P. J. French, Technische Universiteit Delft Prof. dr. E. Charbon, Technische Universiteit Delft Prof. dr. ir. M. K. Smit, Technische Universiteit Eindhoven Dr. S. Wane, NXP Semiconductors Prof. dr. K. A. A. Makinwa, Technische Universiteit Delft, reservelid Copyright °c 2010 by S.M. Sinaga All rights reserved. No part of the material protected by this copyright notice may be reproduced or utilized in any form or by any means, electronic or mechanical, including photocopying, recording or by any information storage and retrieval system, without the prior permission of the author. ISBN 978-90-8570-600-7 Author email: [email protected] Surely goodness and mercy shall follow me all the days of my life; and I will dwell in the house of the Lord forever (Psalm 23:6). -

Solving Electromagnetic Coupling Problems by Spatial Component Placement

Guillaume Girard LCR Electronics Inc. 1 Solving Electromagnetic Coupling Problems by Spatial Component Placement. Guillaume Girard EMC Engineer LCR Electronics Inc. 9 Forest Avenue Norristown, PA, 19401 United States Telephone: (610) 278-0840 Fax: (610) 278-0935 E-Mail: [email protected] Web Address: www.lcr-inc.com Guillaume Girard LCR Electronics Inc. 2 ABSTRACT Many CAD software and design processes include Layout and More and more demand is being placed component placement rules to help on The Appliance Industry to meet achieve signal integrity and EMC. Global Electromagnetic Compatibility performance standards. The The Design review process is divided sophistication of these appliances with into 3 phases, which are considered the use of electronic controls and crucial in the development of an switching power supplies increases the electronic circuit. challenge of solving EMC problems. The most effective way of solving EMC They are; problems is to intervene at the interference sources, i.e. to tackle · Schematic review, them at the component placement level. · Component Placement review Several EMC phenomena take place in · Layout review. electronic circuits, which can be minimized by using simple placement Costly, Electromagnetic problems can rules. be avoided by using guidelines outlined in this article. In this article, guidance is given on component placement considerations SCHEMATIC REVIEW that affect the performance of shielding and filtering. These are in the form of Clock proximity rules that govern spacing between noisy integrated circuit devices Select the slowest clock rate and and ventilation screens, internal the slowest technology that the circuit connectors and filter devices. Special function allows. This will also minimize attention is given to Filter component the cost. -

Electrical and Layout Considerations for 1553 Terminal Design

AN/B- 27 ELECTRICAL AND LAYOUT CONSIDERATIONS FOR 1553 TERMINAL DESIGN INTRODUCTION Table 1 lists the characteristics of the required isola- tion transformers for the various ACE hybrids and MIL-STD-I553B defines a terminal as "The electronic lists the DDC and Beta Transformer Technology module necessary to interface the data bus with the Corporation (BTTC) corresponding part numbers, as subsystem and the subsystem to the data bus… ." well as the MIL (DESC) drawing number (if applica- By definition, the terminal includes the isolation ble).BTTC is a direct subsidiary of Data Device transformer as well as the analog transmitter/receiver Corporation. and the digital protocol section. For both coupling configurations.the transformer that Design of the terminal, therefore, includes selection interfaces directly to the ACE component is called the and interconnection of the isolation transformer.In isolation transformer.As stated above, this is defined order to ensure proper terminal operation in compli- to be part of the terminal.For the transformer (long ance with the 1553 standard, there are a number of stub) coupling configuration.the transformer that issues that need to be considered in this area. interfaces the stub to the bus is the coupling trans- Since most current terminal designs use integrated former. components such as a Small Terminal Interface Circuit The turns ratio of the isolation transformer varies, (STIC) or Advanced Communications Engine (ACE), depending upon the peak-to-peak output voltage of this application note will concentrate on the electrical the specific ACE or STIC terminal.MIL-STD-1553B and layout issues between the hybrid transceiver pins, specifies that the turns ratio of the coupling trans- the isolation transformers, and the system connector. -

On Reduction of Substrate Noise in Mixed-Signal Circuits

Linköping Studies in Science and Technology Thesis No. 1178 ON REDUCTION OF SUBSTRATE NOISE IN MIXED-SIGNAL CIRCUITS Erik Backenius LiU-Tek-Lic-2005:33 Department of Electrical Engineering Linköpings universitet, SE-581 83 Linköping, Sweden Linköping, June 2005 On Reduction of Substrate Noise in Mixed-Signal Circuits Copyright © 2005 Erik Backenius Department of Electrical Engineering Linköpings universitet SE-581 83 Linköping Sweden ISBN 91-85299-78-2 ISSN 0280-7971 Printed in Sweden by UniTryck, Linköping 2005 ABSTRACT Microelectronics is heading towards larger and larger systems implemented on a single chip. In wireless communication equipment, e.g., cellular phones, handheld computers etc., both analog and digital circuits are required. If several integrated circuits (ICs) are used in a system, a large amount of the power is consumed by the communication between the ICs. Furthermore, the communication between ICs is slow compared with on-chip communication. Therefore, it is favorable to integrate the whole system on a single chip, which is the objective in the system-on-chip (SoC) approach. In a mixed-signal SoC, analog and digital circuits share the same chip. When digital circuits are switching, they produce noise that is spread through the silicon substrate to other circuits. This noise is known as substrate noise. The performance of sensitive analog circuits is degraded by the substrate noise in terms of, e.g., lower signal-to-noise ratio and lower spurious-free dynamic range. Another problem is the design of the clock distribution net, which is challenging in terms of obtaining low power consumption, sharp clock edges, and low simultaneous switching noise. -

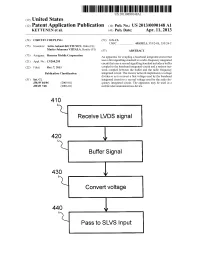

Receive LVDS Signal Buffer Signal 1 Convert Voltage

US 20130090148A1 (19) United States (12) Patent Application Publication (10) Pub. No.: US 2013/0090148 A1 KETTUNEN et al. (43) Pub. Date: Apr. 11, 2013 (54) CIRCUIT COUPLING (52) US. Cl. USPC ................... .. 455/5521; 333/24 R; 333/24 C (75) Inventors: Arttu Aukusti KETTUNEN, Oulu (Fl); Marko Johannes VIITALA, Kontio (Fl) (57) ABSTRACT (73) Asslgneei Renesas Moblle corporatlon An apparatus for coupling a baseband integrated circuit that _ uses a ?rst signalling standard to a radio frequency integrated (21) Appl' NO" 13/268,295 circuit that uses a second signalling standard includes a buffer (22) Filed: Oct 7’ 2011 coupled to the baseband integrated circuit and a resistor net Work coupled between the buffer and the radio frequency Publication Classi?cation integrated circuit. The resistor network implements a voltage divider so as to convert a ?rst voltage used by the baseband (51) Int. Cl. integrated circuit to a second voltage used by the radio fre H04 W 88/06 (2009.01) quency integrated circuit. The apparatus may be used in a H03H 7/06 (2006.01) mobile telecommunications device. 410 1 Receive LVDS signal 420 I Buffer Signal 430 1 Convert voltage 440 1 Pass to SLVS Input Patent Application Publication Apr. 11, 2013 Sheet 1 0f 6 US 2013/0090148 A1 _ _ _I IIilIII __"H .... _ "0E19mm _/ L1_J/_.1xk ON?_Q:OS 02 \+_\Jqfmmv__ n_nW_NE_X: MM_??a; Fl|3;|| xmi.xh. _ n __o2_ IIN_.I|IIlIiI i lI l I Ii ||l <_\.0_"_ Q2 xm_ Patent Application Publication Apr. 11, 2013 Sheet 2 0f 6 US 2013/0090148 A1 ~ _ r|l|||I | |. -

Section D7: Amplifier Coupling& Multistage Analysis

Section D7: Amplifier Coupling& Multistage Analysis So far, we‘ve talked about coupling in terms of using capacitors on the signal source and load in our single stage amplifier configurations. These capacitors (which we assumed were ideal) provided us with complete dc isolation for biasing purposes and acted as ideal shorts under ac conditions. In this section, we‘re going to focus on amplifiers that are composed of more than one stage. For these systems, it is necessary to connect, or couple, the individual stages to each other. Specifically, we will be looking at capacitive, direct, and transformer coupling between transistor stages, in addition to the input and output. Capacitive Coupling Capacitive coupling is exactly what we‘ve been doing so far. It is the simplest and most effective way to remove the effects of any dc levels between amplifier stages, since the capacitor removes the dc component from the ac signal. This is particularly important in multistage amplifiers because we want to be sure not to amplify any dc levels, which may drive our amplifier into saturation and render the output useless. Capacitive coupling allows us to treat each stage as an individual in terms of biasing. We will continue to assume that the capacitors used are large so we can say that they are essentially short circuits for the frequency range of interest. (Practically, this will never be the case and capacitors should be chosen such that the signal is not significantly changed, but we‘ll get into that later.) A two stage, capacitive coupled ER-CE amplifier is shown to the right. -

3 Amplifiers Coupling

Electrical, Electronic and Digital Principles (EEDP) Lecture 5 • Multistage Amplifiers and Coupling And Amplifier Classes د. باسم ممدوح الحلوانى Two or more amplifiers can be connected in a cascaded arrangement with the output of one amplifier driving the input of the next. The basic purpose of using multistage is to increase the overall voltage gain. Amplifier voltage gain is often expressed in decibels (dB) as follows: Total gain in dB is given by: EEDP - Basem ElHalawany 2 Amplifiers Coupling 1. RC-Coupling 2. Transformer Coupling 3. Direct Coupling EEDP - Basem ElHalawany 3 Capacitively-Coupled (R-C Coupling) 4 The output of the first stage capacitively coupled to the input of the 2nd stage. Capacitive coupling prevents the dc bias of one stage from affecting that of the other but allows the ac signal to pass without attenuation Identical Stages Because the coupling capacitor C3 effectively appears as a short at the signal frequency, the total input resistance of the second stage presents an ac load to the first stage. Capacitively-Coupled (R-C Coupling) 5 DC Analysis of each stage (Identical and capacitively coupled) = 25 mv/IE = B re Capacitively-Coupled (R-C Coupling) 6 AC equivalent of first stage showing loading from second stage input resistance. The ac collector resistance of the first stage is The second stage has no load resistor, so the ac collector resistance is R7, and the gain is Compare this to the gain of the first stage (Identical stages) , and Notice how much the loading from the second stage reduced the gain. Direct-Coupled Multistage Amplifiers There are no coupling or bypass capacitors The dc collector voltage of the first stage provides the base-bias voltage for the second stage. -

Dominant Coupling Mechanism for Integrated Circuit Immunity of SOIC Packages up to 10 Ghz Sjoerd Op ’T Land, Mohamed Ramdani, Richard Perdriau

Dominant Coupling Mechanism for Integrated Circuit Immunity of SOIC Packages Up To 10 GHz Sjoerd Op ’T Land, Mohamed Ramdani, Richard Perdriau To cite this version: Sjoerd Op ’T Land, Mohamed Ramdani, Richard Perdriau. Dominant Coupling Mechanism for Integrated Circuit Immunity of SOIC Packages Up To 10 GHz. IEEE Transactions on Electro- magnetic Compatibility, Institute of Electrical and Electronics Engineers, 2018, 60 (4), pp.965-970. 10.1109/TEMC.2017.2756915. hal-01698776 HAL Id: hal-01698776 https://hal.archives-ouvertes.fr/hal-01698776 Submitted on 1 Feb 2018 HAL is a multi-disciplinary open access L’archive ouverte pluridisciplinaire HAL, est archive for the deposit and dissemination of sci- destinée au dépôt et à la diffusion de documents entific research documents, whether they are pub- scientifiques de niveau recherche, publiés ou non, lished or not. The documents may come from émanant des établissements d’enseignement et de teaching and research institutions in France or recherche français ou étrangers, des laboratoires abroad, or from public or private research centers. publics ou privés. 1 Dominant Coupling Mechanism for Integrated Circuit Immunity of SOIC Packages up to 10 GHz † † † Sjoerd Op ’t Land∗ , Member, IEEE, Mohamed Ramdani∗ , Senior Member, IEEE, Richard Perdriau∗ , Senior Member, IEEE ∗RF-EMC Research Group, ESEO-TECH, Angers, France Email: [email protected], richard.perdriau, mohamed.ramdani @eseo.fr f g †ADH, IETR Rennes, France Abstract—As the frequency of functional signals and interfer- a significant effort. However, the authors suspect there is no ing fields is rising beyond 1 GHz, the immunity of integrated significant effort, because it is not yet necessary for industry to circuits (ICs) against these higher frequencies is interesting. -

BJT Amplifiers 6

BJT AMPLIFIERS 6 CHAPTER OUTLINE VISIT THE WEBSITE 6–1 Amplifier Operation Study aids, Multisim, and LT Spice files for this chapter are 6–2 Transistor AC Models available at https://www.pearsonhighered.com 6–3 The Common-Emitter Amplifier /careersresources/ 6–4 The Common-Collector Amplifier 6–5 The Common-Base Amplifier IntroDUCTION 6–6 Multistage Amplifiers The things you learned about biasing a transistor in Chapter 5 6–7 The Differential Amplifier are now applied in this chapter where bipolar junction tran- 6–8 Troubleshooting sistor (BJT) circuits are used as small-signal amplifiers. The term small-signal refers to the use of signals that take up Device Application a relatively small percentage of an amplifier’s operational range. Additionally, you will learn how to reduce an ampli- CHAPTER OBJECTIVES fier to an equivalent dc and ac circuit for easier analysis, and you will learn about multistage amplifiers. The differential ◆◆ Describe amplifier operation amplifier is also covered. ◆◆ Discuss transistor models ◆◆ Describe and analyze the operation of common-emitter DEVICE Application PREVIEW amplifiers The Device Application in this chapter involves a preampli- ◆◆ Describe and analyze the operation of common-collector amplifiers fier circuit for a public address system. The complete system includes the preamplifier, a power amplifier, and a dc power ◆◆ Describe and analyze the operation of common-base supply. You will focus on the preamplifier in this chapter amplifiers and then on the power amplifier in Chapter 7. ◆◆ Describe -

HIGH SPEED ADC APPLICATIONS Walt Kester, Brad Brannon, Paul Hendricks

SECTION 5 HIGH SPEED ADC APPLICATIONS Walt Kester, Brad Brannon, Paul Hendricks DRIVING ADC INPUTS FOR LOW DISTORTION AND WIDE DYNAMIC RANGE In order to achieve wide dynamic range in high speed ADC applications, careful attention must be given to the analog interface. Many ADCs are designed so that analog signals can be interfaced directly to their inputs without the necessity of a drive amplifier. This is especially true in ADCs such as the AD9220/21/23 family and the AD9042, where even a low distortion drive amplifier may result in some degradation in AC performance. If a buffer amplifier is required, it must be carefully selected so that its distortion and noise performance is better than that of the ADC. Single-supply ADCs generally yield optimum AC performance when the common- mode input voltage is centered between the supply rails (although the optimum common-mode voltage may be skewed slightly in either direction about this point depending upon the particular design). This also eases the drive requirement on the input buffer amplifier (if required) since even "rail-to-rail" output op amps give best distortion performance if their output is centered about mid-supply, and the peak signals are kept at least 1V from either rail. Typical high speed single-supply ADC peak-to-peak input voltage ranges may vary from about 0.5V to 5V, but in most cases, 1V to 2V peak-to-peak represents the optimum tradeoff between noise and distortion performance. In single-supply applications requiring DC coupling, careful attention must be given to the input and output common-mode range of the driving amplifier.