Operational Amplifiers and Linear Integrated Circuits, 3E

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Transistor Circuit Guidebook Byron Wels TAB BOOKSBLUE RIDGE SUMMIT, PA

TAB BOOKS No. 470 34.95 By Byron Wels TransistorCircuit GuidebookByronWels TABBLUE RIDGE BOOKS SUMMIT,PA. 17214 Preface beforemeIa supposepioneer (along the my withintransistor firstthe many field.experiencewith wasother Weknown. World were using WarUnlike solid-stateIIsolid-state GIs) today's asdevices somewhat experimen- receivers marks of FIRST EDITION devicester,ownFirst, withsemiconductors! youwith a choice swipedwhichor tank. ofto a sealed,Here'sexperiment, pairThen ofhow encapsulated, you earphones we carefullywe did had it: from totookand construct the veryonenearest exoticof our the THIRDSECONDFIRST PRINTING-SEPTEMBER PRINTING-AUGUST PRINTING-JANUARY 1972 1970 1968 plane,wasyouAnphonesantenna. emptywound strung jeep,apart After toiletfull outand ofclippingas paper wire,unwoundhigh closelyrollandthe servedascatchthe far spaced.wire offas as itfrom a thewouldsafetyThe thecoil remaining-pin,magnetreach-for form, you inside.which stuckwire the Copyright © 1968by TAB BOOKS coatedNext,it into youneeded,a hunkribbons of -ofwooda razor -steel, soblade.the but point Oh,aItblued was noneprojected placedblade of the -quenchat so fancy right the pointplastic-bluedangles.of -, Reproduction or publicationPrinted inof the ofAmerica the United content States in any manner, with- themindfoundphoneground pin you,the was couldserved right not wired contact lacquerspotas toa onground blade, it. theblued.blade'sAconnector, pin,bayonet bluing,and stuck antennaand you hilt thecould coil.-deep other actuallyIfin ear- youthe isoutherein. assumed express -

Run Capacitor Info-98582

Run Cap Quiz-98582_Layout 1 4/16/15 10:26 AM Page 1 ® Run Capacitor Info WHAT IS A CAPACITOR? Very simply, a capacitor is a device that stores and discharges electrons. While you may hear capacitors referred to by a variety of names (condenser, run, start, oil, etc.) all capacitors are comprised of two or more metallic plates separated by an insulating material called a dielectric. PLATE 1 PLATE 2 A very simple capacitor can be made with two plates separated by a dielectric, in this PLATE 1 PLATE 2 case air, and connected to a source of DC current, a battery. Electrons will flow away from plate 1 and collect on plate 2, leaving it with an abundance of electrons, or a “charge”. Since current from a battery only flows one way, the capacitor plate will stay BATTERY + – charged this way unless something causes current flow. If we were to short across the plates with a screwdriver, the resulting spark would indicate the electrons “jumping” from plate 2 to plate 1 in an attempt to equalize. As soon as the screwdriver is removed, plate 2 will again collect a PLATE 1 PLATE 2 charge. + BATTERY – Now let’s connect our simple capacitor to a source of AC current and in series with the windings of an electric motor. Since AC current alternates, first one PLATE 1 PLATE 2 MOTOR plate, then the other would be charged and discharged in turn. First plate 1 is charged, then as the current reverses, a rush of electrons flow from plate 1 to plate 2 through the motor windings. -

Design of a Low Voltage Class-AB CMOS Super Buffer Amplifier with Sub Threshold and Leakage Control Rakesh Gupta

International Journal of Engineering Trends and Technology (IJETT) – Volume 7 Number 1- Jan 2014 Design of a Low Voltage Class-AB CMOS Super Buffer Amplifier with Sub Threshold and Leakage Control Rakesh Gupta Assistant Professor, Electrical and Electronic Department, Uttar Pradesh Technical University, Lucknow Uttar Pradesh, India Abstract-- common problems like input common mode range, This paper describes a CMOS analogy voltage supper output swing, and linearity of the device. In the buffer designed to have extremely low static current resulting form to implement the desired analogue Consumption as well as high current drive capability. A device we apply the CMOS technology with low new technique is used to reduce the leakage power of voltage and low power techniques. Voltage supper class-AB CMOS buffer circuits without affecting dynamic power dissipation. The name of applied buffers are essential building blocks in analog and technique is TRANSISTOR GATING TECHNIQUE, mixed-signal circuits and processing systems, which gives the high speed buffer with the reduced low especially for applications where the weak signal power dissipation (1.105%), low leakage and reduced needs to be delivered to a large capacitive load area (3.08%) also. The proposed buffer is simulated at without being distorted To achieve higher density and 45nm CMOS technology and the circuit is operated at performance and lower power consumption, CMOS 3.3V supply[11]. Consumption is comparable to the devices have been scaled for more than 30 years. switching component. Reports indicate that 40% or Transistor delay times have decreased by more than even higher percentage of the total power consumption 30% per technology generation resulting in doubling is due to the leakage of transistors. -

Chapter 7: AC Transistor Amplifiers

Chapter 7: Transistors, part 2 Chapter 7: AC Transistor Amplifiers The transistor amplifiers that we studied in the last chapter have some serious problems for use in AC signals. Their most serious shortcoming is that there is a “dead region” where small signals do not turn on the transistor. So, if your signal is smaller than 0.6 V, or if it is negative, the transistor does not conduct and the amplifier does not work. Design goals for an AC amplifier Before moving on to making a better AC amplifier, let’s define some useful terms. We define the output range to be the range of possible output voltages. We refer to the maximum and minimum output voltages as the rail voltages and the output swing is the difference between the rail voltages. The input range is the range of input voltages that produce outputs which are not at either rail voltage. Our goal in designing an AC amplifier is to get an input range and output range which is symmetric around zero and ensure that there is not a dead region. To do this we need make sure that the transistor is in conduction for all of our input range. How does this work? We do it by adding an offset voltage to the input to make sure the voltage presented to the transistor’s base with no input signal, the resting or quiescent voltage , is well above ground. In lab 6, the function generator provided the offset, in this chapter we will show how to design an amplifier which provides its own offset. -

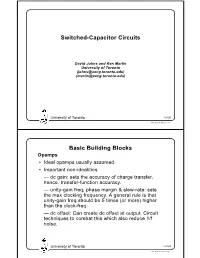

Switched-Capacitor Circuits

Switched-Capacitor Circuits David Johns and Ken Martin University of Toronto ([email protected]) ([email protected]) University of Toronto 1 of 60 © D. Johns, K. Martin, 1997 Basic Building Blocks Opamps • Ideal opamps usually assumed. • Important non-idealities — dc gain: sets the accuracy of charge transfer, hence, transfer-function accuracy. — unity-gain freq, phase margin & slew-rate: sets the max clocking frequency. A general rule is that unity-gain freq should be 5 times (or more) higher than the clock-freq. — dc offset: Can create dc offset at output. Circuit techniques to combat this which also reduce 1/f noise. University of Toronto 2 of 60 © D. Johns, K. Martin, 1997 Basic Building Blocks Double-Poly Capacitors metal C1 metal poly1 Cp1 thin oxide bottom plate C1 poly2 Cp2 thick oxide C p1 Cp2 (substrate - ac ground) cross-section view equivalent circuit • Substantial parasitics with large bottom plate capacitance (20 percent of C1) • Also, metal-metal capacitors are used but have even larger parasitic capacitances. University of Toronto 3 of 60 © D. Johns, K. Martin, 1997 Basic Building Blocks Switches I I Symbol n-channel v1 v2 v1 v2 I transmission I I gate v1 v p-channel v 2 1 v2 I • Mosfet switches are good switches. — off-resistance near G: range — on-resistance in 100: to 5k: range (depends on transistor sizing) • However, have non-linear parasitic capacitances. University of Toronto 4 of 60 © D. Johns, K. Martin, 1997 Basic Building Blocks Non-Overlapping Clocks I1 T Von I I1 Voff n – 2 n – 1 n n + 1 tTe delay 1 I fs { --- delay V 2 T on I Voff 2 n – 32e n – 12e n + 12e tTe • Non-overlapping clocks — both clocks are never on at same time • Needed to ensure charge is not inadvertently lost. -

Power Electronics

Diodes and Transistors Semiconductors • Semiconductor devices are made of alternating layers of positively doped material (P) and negatively doped material (N). • Diodes are PN or NP, BJTs are PNP or NPN, IGBTs are PNPN. Other devices are more complex Diodes • A diode is a device which allows flow in one direction but not the other. • When conducting, the diodes create a voltage drop, kind of acting like a resistor • There are three main types of power diodes – Power Diode – Fast recovery diode – Schottky Diodes Power Diodes • Max properties: 1500V, 400A, 1kHz • Forward voltage drop of 0.7 V when on Diode circuit voltage measurements: (a) Forward biased. (b) Reverse biased. Fast Recovery Diodes • Max properties: similar to regular power diodes but recover time as low as 50ns • The following is a graph of a diode’s recovery time. trr is shorter for fast recovery diodes Schottky Diodes • Max properties: 400V, 400A • Very fast recovery time • Lower voltage drop when conducting than regular diodes • Ideal for high current low voltage applications Current vs Voltage Characteristics • All diodes have two main weaknesses – Leakage current when the diode is off. This is power loss – Voltage drop when the diode is conducting. This is directly converted to heat, i.e. power loss • Other problems to watch for: – Notice the reverse current in the recovery time graph. This can be limited through certain circuits. Ways Around Maximum Properties • To overcome maximum voltage, we can use the diodes in series. Here is a voltage sharing circuit • To overcome maximum current, we can use the diodes in parallel. -

Electronic Circuit Design and Component Selecjon

Electronic circuit design and component selec2on Nan-Wei Gong MIT Media Lab MAS.S63: Design for DIY Manufacturing Goal for today’s lecture • How to pick up components for your project • Rule of thumb for PCB design • SuggesMons for PCB layout and manufacturing • Soldering and de-soldering basics • Small - medium quanMty electronics project producMon • Homework : Design a PCB for your project with a BOM (bill of materials) and esMmate the cost for making 10 | 50 |100 (PCB manufacturing + assembly + components) Design Process Component Test Circuit Selec2on PCB Design Component PCB Placement Manufacturing Design Process Module Test Circuit Selec2on PCB Design Component PCB Placement Manufacturing Design Process • Test circuit – bread boarding/ buy development tools (breakout boards) / simulaon • Component Selecon– spec / size / availability (inventory! Need 10% more parts for pick and place machine) • PCB Design– power/ground, signal traces, trace width, test points / extra via, pads / mount holes, big before small • PCB Manufacturing – price-Mme trade-off/ • Place Components – first step (check power/ground) -- work flow Test Circuit Construc2on Breadboard + through hole components + Breakout boards Breakout boards, surcoards + hookup wires Surcoard : surface-mount to through hole Dual in-line (DIP) packaging hap://www.beldynsys.com/cc521.htm Source : hap://en.wikipedia.org/wiki/File:Breadboard_counter.jpg Development Boards – good reference for circuit design and component selec2on SomeMmes, it can be cheaper to pair your design with a development -

Diode Limiters Or Clipper Circuits

Diode Limiters or Clipper Circuits Circuits which are used to clip off portions of signal voltages above or below certain levels are called limiters or clippers. Types of Clippers • Positive Clipper • Negative Clipper Positive Clipper • The circuit that limits or clips the positive part of the input voltage, is called a positive limiter or positive clipper. Working of Positive Clipper • As the input voltage goes positive, the diode becomes forward-biased and conducts current. • Since the cathode is at ground potential (0V), the anode cannot exceed 0.7V (for Si). • So point A is limited to +0.7V when the input voltage exceeds this value. • When the input voltage goes back below 0.7V, the diode is reverse-biased and appears as an open. • The output voltage looks like the negative part of the input voltage, but with magnitude determined by the voltage divider formed by R1 and load resistor RL; Negative Clipper • The circuit that limits or clips the negative part of the input voltage, is called a negative limiter or negative clipper. Working of Negative Clipper • If the diode is turned around, the negative part of the input voltage is clipped off. • When the diode is forward-biased during the negative part of the input voltage, point A is held at -0.7V by the diode drop. • When the input voltage goes above –0.7V, the diode is no longer forward- biased; and a voltage appears across RL proportional to input voltage. Practical Problem • What will be the output waveform across RL in the limiter circuit shown in figure Clamper Circuits Clamping is the process of introducing a dc level into an ac signal. -

Chapter 10 Differential Amplifiers

Chapter 10 Differential Amplifiers 10.1 General Considerations 10.2 Bipolar Differential Pair 10.3 MOS Differential Pair 10.4 Cascode Differential Amplifiers 10.5 Common-Mode Rejection 10.6 Differential Pair with Active Load 1 Audio Amplifier Example An audio amplifier is constructed as above that takes a rectified AC voltage as its supply and amplifies an audio signal from a microphone. CH 10 Differential Amplifiers 2 “Humming” Noise in Audio Amplifier Example However, VCC contains a ripple from rectification that leaks to the output and is perceived as a “humming” noise by the user. CH 10 Differential Amplifiers 3 Supply Ripple Rejection vX Avvin vr vY vr vX vY Avvin Since both node X and Y contain the same ripple, their difference will be free of ripple. CH 10 Differential Amplifiers 4 Ripple-Free Differential Output Since the signal is taken as a difference between two nodes, an amplifier that senses differential signals is needed. CH 10 Differential Amplifiers 5 Common Inputs to Differential Amplifier vX Avvin vr vY Avvin vr vX vY 0 Signals cannot be applied in phase to the inputs of a differential amplifier, since the outputs will also be in phase, producing zero differential output. CH 10 Differential Amplifiers 6 Differential Inputs to Differential Amplifier vX Avvin vr vY Avvin vr vX vY 2Avvin When the inputs are applied differentially, the outputs are 180° out of phase; enhancing each other when sensed differentially. CH 10 Differential Amplifiers 7 Differential Signals A pair of differential signals can be generated, among other ways, by a transformer. -

Differential Amplifiers

www.getmyuni.com Operational Amplifiers: The operational amplifier is a direct-coupled high gain amplifier usable from 0 to over 1MH Z to which feedback is added to control its overall response characteristic i.e. gain and bandwidth. The op-amp exhibits the gain down to zero frequency. Such direct coupled (dc) amplifiers do not use blocking (coupling and by pass) capacitors since these would reduce the amplification to zero at zero frequency. Large by pass capacitors may be used but it is not possible to fabricate large capacitors on a IC chip. The capacitors fabricated are usually less than 20 pf. Transistor, diodes and resistors are also fabricated on the same chip. Differential Amplifiers: Differential amplifier is a basic building block of an op-amp. The function of a differential amplifier is to amplify the difference between two input signals. How the differential amplifier is developed? Let us consider two emitter-biased circuits as shown in fig. 1. Fig. 1 The two transistors Q1 and Q2 have identical characteristics. The resistances of the circuits are equal, i.e. RE1 = R E2, RC1 = R C2 and the magnitude of +VCC is equal to the magnitude of �VEE. These voltages are measured with respect to ground. To make a differential amplifier, the two circuits are connected as shown in fig. 1. The two +VCC and �VEE supply terminals are made common because they are same. The two emitters are also connected and the parallel combination of RE1 and RE2 is replaced by a resistance RE. The two input signals v1 & v2 are applied at the base of Q1 and at the base of Q2. -

Ee320l 05 Experiment 5.Pdf

EE320L Electronics I Laboratory Laboratory Exercise #5 Clipping and Clamping Circuits By Angsuman Roy Department of Electrical and Computer Engineering University of Nevada, Las Vegas Objective: The purpose of this lab is to understand the operation of clipping and clamping circuits and their applications. Equipment Used: Power Supply Oscilloscope Function Generator Breadboard Jumper Wires TL082 or LF412 Dual JFET Input Operational Amplifiers 10x Scope Probes Various Resistors and Capacitors Background: Clipping and Clamping Circuits Diodes, despite being two terminals devices have more uses than it may seem. While the application most commonly associated with diodes is rectification for power supplies and radio frequency detection, diodes are also used for clipping and clamping signals. Clipping is simply bounding a signal to limited amplitude. Clamping is shifting the center of an AC signal to a different value. Both of these operations can be implemented with a diode and a few passive components. Active versions of these circuits are implemented with op-amps. As is commonly the case, using op-amps allows the performance of a circuit to approach theoretical ideals. Clipping and clamping circuits find widespread use in audio and video circuitry. A brief digression into the types of diodes is important for designing clipping and clamping circuits. Diodes can be classified based on their material type, application and structure. Most diodes today are made out of silicon. These diodes have a forward voltage drop of around 0.6V. In the past, germanium diodes were more common and had a forward voltage drop of 0.3V. They can still be purchased if one looks hard enough. -

50 Simple L.E.D. Circuits

50 Simple L.E.D. Circuits R.N. SOAR r de Historie v/d Radi OTH'IEK 50 SIMPLE L.E.D. CIRCUITS by R. N. SOAR BABANI PRESS The Publishing Division of Babani Trading and Finance Co. Ltd. The Grampians Shepherds Bush Road London W6 7NI- England Although every care is taken with the preparation of this book, the publishers or author will not be responsible in any way for any errors that might occur. © 1977 BA BAN I PRESS I.S.B.N. 0 85934 043 4 First Published December 1977 Printed and Manufactured in Great Britain by C. Nicholls & Co. Ltd. f t* -i. • v /“ ..... tr> CONTENTS U.V.H.R* Circuit Page No. 1 LED Pilot Light......................................... 7 2 LED Stereo Beacon.................................... 8 3 Stereo Decoder Mono/Sterco Indicator . 9 4 Subminiature LED Torch........................... 10 5 Low Voltage Low Current Supply............ 11 6 Microlight Indicator .................................. 12 7 Ultra Low Current LED Switching Indicator 13 8 LED Stroboscope....................................... 14 9 12 Volt Car Circuit Tester........................... 15 10 Two Colour LED......................................... 16 11 12 Volt Car “Fuse Blown” Indicator.......... 17 12 LED Continuity Tester............................... 17 13 LED Current Overload Indicator.............. 18 14 LED Current Range Indicator................... 20 15 1.5 Volt LED “Zener”................. '............ 22 16 Extending Zener Voltage........................... 22 17 Four Voltage Regulated Supply................. 23 18 PsychaLEDic Display.................................. 24 .19 Dual Colour Display.................................... 25 20 Dual Signal Device....................................... 26 21 LED Triple Signalling.................................. 27 22 Sub-Miniature Light Source for Model Railways . 28 23 Portable Television Protection Circuit . 29 24 Improved Portable TV Protection Circuit 30 25 LED Battery Tester..............................