Occam User Group Newsletter

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Newsletter • Bulletin Winter 2005 Hiver

NATIONAL CAPITAL OPERA SOCIETY • SOCIÉTÉ D'OPÉRA DE LA CAPITALE NATIONALE Newsletter • Bulletin Winter 2005 Hiver P.O. Box 8347, Main Terminal, Ottawa, Ontario K1G 3H8 • C.P. 8347, Succursale principale, Ottawa (Ontario) K1G 3H8 Outstanding Finalists for the Brian Law Competition At the end of November 2004 the preliminary jury consisting of The Barbara Clark, Garth Hampson and Charlotte Stewart met to National Capital Opera Society choose the finalists from the large number of applicants received. presents Many thanks to Barbara, Garth and Charlotte for once again help- ing our organization. The Brian Law We are pleased to announce that Joyce El-Khoury, Brian Estabrooks, Liliana Piazza and Maghan Stewart will be vying for Opera Scholarship top spot in the 2005 Brian Law Opera Scholarship Competition. Competition The first prize is $2,000 as usual but this year we are delighted to announce that, due to the generosity of NCOS Board Member Cavaliere Pat Adamo, a second prize of $300 and a third prize of under the Patronage of Maureen Forrester, C.C. for a $200 will also be given. Full details of each of the finalists education $2000 first prize and musical experience is given on pages 4 & 5. The contest will be held in the First Unitarian Congregation, Finalists: 30 Cleary Avenue (off Richmond Road) on Saturday January 29, Joyce El-Khoury - soprano 2005 starting at 7:30 pm. The four finalists will each sing three arias Bryan Estabrooks - baritone (one with recitative) and will be judged by our distinguished panel Liliana Piazza - mezzo-soprano consisting of Roxalana Roslak and Darryl Edwards of Toronto and Maghan Stewart – soprano Christiane Riel of Montreal. -

Emerging Technologies Multi/Parallel Processing

Emerging Technologies Multi/Parallel Processing Mary C. Kulas New Computing Structures Strategic Relations Group December 1987 For Internal Use Only Copyright @ 1987 by Digital Equipment Corporation. Printed in U.S.A. The information contained herein is confidential and proprietary. It is the property of Digital Equipment Corporation and shall not be reproduced or' copied in whole or in part without written permission. This is an unpublished work protected under the Federal copyright laws. The following are trademarks of Digital Equipment Corporation, Maynard, MA 01754. DECpage LN03 This report was produced by Educational Services with DECpage and the LN03 laser printer. Contents Acknowledgments. 1 Abstract. .. 3 Executive Summary. .. 5 I. Analysis . .. 7 A. The Players . .. 9 1. Number and Status . .. 9 2. Funding. .. 10 3. Strategic Alliances. .. 11 4. Sales. .. 13 a. Revenue/Units Installed . .. 13 h. European Sales. .. 14 B. The Product. .. 15 1. CPUs. .. 15 2. Chip . .. 15 3. Bus. .. 15 4. Vector Processing . .. 16 5. Operating System . .. 16 6. Languages. .. 17 7. Third-Party Applications . .. 18 8. Pricing. .. 18 C. ~BM and Other Major Computer Companies. .. 19 D. Why Success? Why Failure? . .. 21 E. Future Directions. .. 25 II. Company/Product Profiles. .. 27 A. Multi/Parallel Processors . .. 29 1. Alliant . .. 31 2. Astronautics. .. 35 3. Concurrent . .. 37 4. Cydrome. .. 41 5. Eastman Kodak. .. 45 6. Elxsi . .. 47 Contents iii 7. Encore ............... 51 8. Flexible . ... 55 9. Floating Point Systems - M64line ................... 59 10. International Parallel ........................... 61 11. Loral .................................... 63 12. Masscomp ................................. 65 13. Meiko .................................... 67 14. Multiflow. ~ ................................ 69 15. Sequent................................... 71 B. Massively Parallel . 75 1. Ametek.................................... 77 2. Bolt Beranek & Newman Advanced Computers ........... -

Lehman Brothers Holdings

SECURITIES AND EXCHANGE COMMISSION FORM 13F-HR/A Initial quarterly Form 13F holdings report filed by institutional managers [amend] Filing Date: 2004-12-01 | Period of Report: 2004-09-30 SEC Accession No. 0000806085-04-000212 (HTML Version on secdatabase.com) FILER LEHMAN BROTHERS HOLDINGS INC Mailing Address Business Address LEHMAN BROTHERS LEHMAN BROTHERS CIK:806085| IRS No.: 133216325 | State of Incorp.:DE | Fiscal Year End: 1130 745 SEVENTH AVENUE 745 SEVENTH AVENUE Type: 13F-HR/A | Act: 34 | File No.: 028-03182 | Film No.: 041177215 NEW YORK NY 10019 NEW YORK NY 10019 SIC: 6211 Security brokers, dealers & flotation companies 2125267000 Copyright © 2012 www.secdatabase.com. All Rights Reserved. Please Consider the Environment Before Printing This Document NON-CONFIDENTIAL <TABLE> <CAPTION> TITLE OF VALUE SHRS OR SH/ PUT/ INVESTMENT OTHER VOTING AUTHORITY NAME OF ISSUER CLASS CUSIP (X$1000) PRN AMT PRN CALL DISCRETION MANAGERS SOLE SHARED NONE <S> <C> <C> <C> <C> <C> <C> -------------------------------- -------- --------- -------- ------- --- ---- ---------- -------- -------- -------- -------- ***DAIMLERCHRYSLER A.G. COMMON D1668R123 9514 227843 SH DEFINED 01 227843 0 0 ***SANOFI AVENTIS COMMON F5548N101 34013 491666 SH DEFINED 01 491666 0 0 PNM RESOURCES COMMON GKD49H100 0 50000 SH DEFINED 01 0 0 50000 PNM RESOURCES COMMON GKD49H100 0 200000 SH DEFINED 01 200000 0 0 ***ACE LTD-ORD COMMON G0070K103 9964 248616 SH DEFINED 01 0 0 248616 ***ASPEN INSURANCE HOLDINGS COMMON G05384105 3950 171680 SH DEFINED 01 171680 0 0 ***ASSURED GUARANTY -

FEI COMPANY 5350 NE Dawson Creek Drive Hillsboro, Oregon 97124-5793

FEI COMPANY 5350 NE Dawson Creek Drive Hillsboro, Oregon 97124-5793 NOTICE OF ANNUAL MEETING OF SHAREHOLDERS To Be Held On May 7, 2015 To the Shareholders of FEI Company: Notice is hereby given that the Annual Meeting of Shareholders of FEI Company, an Oregon corporation, will be held on Thursday, May 7, 2015, at 9:00 a.m. local time, at our corporate headquarters located at 5350 NE Dawson Creek Drive, Hillsboro, Oregon 97124-5793. The purposes of the annual meeting will be: 1. To elect members of FEI's Board of Directors to serve for the following year and until their successors are duly elected and qualified; 2. To consider and vote on a proposal to amend FEI's 1995 Stock Incentive Plan to increase the number of shares of our common stock reserved for issuance under the plan by 250,000 shares; 3. To consider and vote on a proposal to amend FEI's Employee Share Purchase Plan to increase the number of shares of our common stock reserved for issuance under the plan by 250,000 shares; 4. To approve, on an advisory basis, the appointment of KPMG LLP as FEI's independent registered public accounting firm for the year ending December 31, 2015; 5. To approve, on an advisory basis, FEI's executive compensation; and 6. To transact such other business as may properly come before the meeting or at any and all postponements or adjournments of the meeting. Only shareholders of record at the close of business on March 2, 2015 and their proxies will be entitled to vote at the annual meeting and any adjournment or postponement of the meeting. -

The Communicant News & Notices for the Diocese of Edinburgh 24Th January 2018

21A Grosvenor Crescent Edinburgh EH12 5EL [email protected] 0131 538 7033 Charity Number: SC001214 The Communicant News & Notices for the Diocese of Edinburgh 24th January 2018 Published by the Diocesan Office fortnightly, and circulated to all Clergy, Lay Readers, Treasurers & Vestry Secretaries, and Diocesan Synod Lay & Alternate Lay Representatives NEXT EDITION: 7th February 2018 NOTICES VESTRY Annual Return Forms SECRETARIES A reminder that Annual Return Forms should be completed by 31st January and sent or emailed to the office. They are all available online at: http://edinburgh.anglican.org/resources-diocesan-office-forms/ With one week to go, only 53% of the forms have been received. We do realise that all of you have limited time to get such tasks done, but your urgent attention would be hugely appreciated, especially this year, with the backlog of work we are dealing with, in the office here. Thank you ALL News from Bishops Enabler of Mission Mission Shaped Intro in the Borders DATE: Two Saturdays, 27th Jan and 24th Feb TIME: 10.15am - 2.30pm with a simple lunch VENUE: St John’s Community Centre, The Pleasance, Jedburgh, TD8 6DJ Ideally come with others from your church or individuals welcome too. Our world and our lives are changing at an ever faster pace, but how can our churches respond to this change? Are new ways of engaging with people and being church in the 21st century possible? If so, what might they look like? Using some of the material from the Mission Shaped Intro course we will explore together mission and church life in our current context. -

Caecilia V63n08 1936

Founded A.D. 1874 by John Singenherger • REVI EW OF SUMMER EVENTS • PRINCIPLES OF ARTISTIC CHORAL ATTAINMENT Rev. J. Ribeyron • ANALYSIS OF LOUIS VIERNE MUSIC Dom Adelard Bouvilliers • HOW TO SELECT CHURCH MUSIC Joseph Clokey • Vol. 63 SEPTEMBER 1936 ORATE FRATRES A ReYiew Devoted to the Liturgical Apoatolate TS first purpose is to foster an intelligent and whole-hearted participation I the liturgical life of the Church, which Pius X has called "the primary a indispensable source of the true Christian spirit." Secondarily it also considers the liturgy in its literary, artistic, musical, social, educational and historical aspects. From a Letter Signed By His Eminence Cardinal Gasparri "The Holy Father is greatly pleased that St. John's Abbey is continuing the glorious tradition, and that there is emanating from this abbey an inspiration that tends to elevate the piety of the faithful by leading them back to the pure fountain of the sacred liturgy." Published every fOUf weeks, beginning with Advent, twelve issues the year. Forty-eight pages. Two dollars the year in the United States. Write for sample copy and descriptive leaflet. THE LITURGICAL PRESS CoUegeville Minnesota Entered as second class mat ter, October 20, 1931, at the Post Office at Boston, Mass•• ~aetilia under the Act of March 3, 1879. Qfl1r Formerly published in St. Francis, Wisconsin. Now issued Monthly Magazine of Catholic Church and School Music monthly, except in July. Subscription: $3 per year, pay.. able in advance. Single copies September 1936 No.8 SOc. Vol. 63 EDITOR V. REV. GREGORY HUGLE, O.S.B. • Prior, Conception Abbey Conception, Mo. -

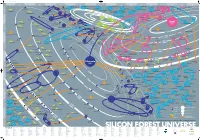

Silicon Forest Universe

15239 Poster 9/16/02 1:03 PM Page 1 AB CDE FGH I JKL M N O P Q R S Pearlsoft COMSAT General Integrated Systems Ashwood Group '85 Qualis Design fka CPU International Nel-Tech Development '98 Qsent '01 Briefsmart.com '00 Relyent TrueDisk Trivium Systems '80 '74 '99 '90 Gearbeat '81 Relational Systems Galois 3DLand Teradyne in 2001 '85 '00 '98 Solution Logic SwiftView Imagenation '89 Metro One IronSpire '84 Smart Mediary Systems Connections 13 Telecommunications WireX GenRad in 1996 '00 CyberOptics E-Core Salu Logiplex '79 MyHealthBank Semiconductor Cotelligent Technologies Fujitsu America Barco Metheus '77 '99 Group Knowledge fka United Data Biotronik Timlick & Associates in 1999 Gadget Labs Adaptive Solutions Wave International Processing Cascade Laser '98 Webridge Axis Clinical Software Mitron Basicon '91 GemStone fka Servio Logic Source Services '83 Integra Telecom Accredo FaxBack Polyserve Metheus Intersolv Babcock & Jenkins Electro '79 Informedics Scientific Sliceware Graphic Software Systems Industries IBM 12 in 1999 Atlas Telecom 1944 Sequent Computer ProSight Credence in 2001 19 ADC Kentrox '78 Oracle '69 Merant Datricon 60s Informix Systems FEI Sage Software fka Polytron MKTX 197 Mikros Nike 0s Etec Systems '63 19 Sentrol in 1995 Intel 80s SEH America Teseda Oregon Graduate Institute Flight Dynamics 1976 '97 1990 Purchasing Solutions Fluence ~ Relcom Vidco Mushroom Resources Cunningham & Cunningham '99 Myteam.com Praegitzer Industries Integrated Measurement Systems Zicon Digital World Lucy.Com Nonbox in 2001 ATEQ 11 Software Access -

Technology Transfer Joint Hearing

TECHNOLOGY TRANSFER JOINT HEARING BEFORE THE COMMITTEE ON SCIENCE AND TECHNOLOGY HOUSE OF REPRESENTATIVES AND THE SUBCOMMITTEE ON ENERGY RESEARCH AND DEVELOPMENT OF THE COMMITTEE ON ENERGY AND NATURAL RESOURCES U.S. SENATE NINETY-NINTH CONGRESS SECOND SESSION SEPTEMBER 4, 1986 [No. 161] Printed for the use of the Committee on Science and Technology, and the Committee on Energy and Natural Resources, U.S. Senate U.S. GOVERNMENT PRINTING OFFICE 67-150 0 WASHINGTON : 1987 For sale by the Superintendent of Documents, Congressional Sales Office US. Government Printing Office, Washington, DC 20402 rX K ' .., ;.- .,,... COMMITTEE ON SCIENCE AND TECHNOLOGY DON FUQUA, Florida, Chairman ROBERT A. ROE, New Jersey MANUEL LUJAN, JR., New Mexico* GEORGE E. BROWN, JH., California ROBERT S. WALKER, Pennsylvania JAMES H. SCHEUER, New York F. JAMES SENSENBRENNER, JR., MARILYN LLOYD, Tennessee Wisconsin TIMOTHY <E. WIRTH, Colorado CLAUDINE SCHNEIDER, Rhode Island DOUG WALGREN, Pennsylvania SHERWOOD L. BOEHLERT, New York DAN GLICKMAN, Kansas TOM LEWIS, Florida ROBERT A. YOUNG, Missouri DON RTTTER, Pennsylvania HAROLD L. VOLKMER, Missouri SID W. MORRISON, Washington BILL NELSON, Florida RON PACKARD, California STAN LUNDINE, New York JAN MEYERS, Kansas RALPH M. HALL, Texas ROBERT C. SMITH, New Hampshire DAVE McCURDY, Oklahoma PAUL B. HENRY, Michigan NORMAN Y. MINETA, California HARRIS W. FAWELL, Illinois BUDDY MACKAY, Florida" WILLIAM W. COBEY, JR., North Carolina TIM VALENTINE, North Carolina JOE BARTON, Texas HARRY M. REID, Nevada D. FRENCH SLAUGHTER, JR., Virginia ROBERT G. TORRICELLI, New Jersey DAVID S. MONSON, Utah RICK BOUCHER, Virginia TERRY BRUCE, Illinois RICHARD H. STALLINGS, Idaho BART GORDON, Tennessee JAMES A. TRAFICANT, JR., Ohio JIM CHAPMAN, Texas HAROLD P. -

Lehman Brothers Holdings

SECURITIES AND EXCHANGE COMMISSION FORM 13F-HR/A Initial quarterly Form 13F holdings report filed by institutional managers [amend] Filing Date: 2005-02-17 | Period of Report: 2004-12-31 SEC Accession No. 0000806085-05-000044 (HTML Version on secdatabase.com) FILER LEHMAN BROTHERS HOLDINGS INC Mailing Address Business Address LEHMAN BROTHERS LEHMAN BROTHERS CIK:806085| IRS No.: 133216325 | State of Incorp.:DE | Fiscal Year End: 1130 745 SEVENTH AVENUE 745 SEVENTH AVENUE Type: 13F-HR/A | Act: 34 | File No.: 028-03182 | Film No.: 05624078 NEW YORK NY 10019 NEW YORK NY 10019 SIC: 6211 Security brokers, dealers & flotation companies 2125267000 Copyright © 2012 www.secdatabase.com. All Rights Reserved. Please Consider the Environment Before Printing This Document <TABLE> <CAPTION> TITLE OF VALUE SHRS OR SH/ PUT/ INVESTMENT OTHER VOTING AUTHORITY NAME OF ISSUER CLASS CUSIP (X$1000) PRN AMT PRN CALL DISCRETION MANAGERS SOLE SHARED NONE <S> <C> <C> <C> <C> <C> <C> -------------------------------- -------- --------- -------- ------- --- ---- ---------- -------- -------- -------- -------- ***DAIMLERCHRYSLER A.G. COMMON D1668R123 226 4707 SH DEFINED 01 4707 0 0 ***DEUTSCHE BANK AG COMMON D18190898 397 4463 SH DEFINED 01 4463 0 0 ***ACE LTD-ORD COMMON G0070K103 6966 162834 SH DEFINED 01 0 0 162834 ***AMDOCS LIMITED COMMON G02602103 547 20661 SH DEFINED 01 0 0 20661 ***ARCH CAPITAL GROUP LTD COMMON G0450A105 230 5957 SH DEFINED 01 5957 0 0 ***ARLINGTON TANKERS LTD COMMON G04899103 1038 45250 SH DEFINED 01 45250 0 0 ***ASPEN INSURANCE HOLDINGS COMMON -

The Communicant 7 February 2018

21A Grosvenor Crescent Edinburgh EH12 5EL [email protected] 0131 538 7033 Charity Number: SC001214 The Communicant News & Notices for the Diocese of Edinburgh 7th February 2018 Published by the Diocesan Office fortnightly, and circulated to all Clergy, Lay Readers, Treasurers & Vestry Secretaries, and Diocesan Synod Lay & Alternate Lay Representatives st NEXT EDITION: 21 February 2018 NOTICES Diocesan Office Development Day The Diocesan Office will be closed on Tuesday 20th February , for a Staff Development Day. We will reopen at 9am on Wednesday 21st February. VESTRY SECRETARIES Annual Return Forms The deadline for the Annual Return Forms was 31st January To date, only 78% of the forms have been received – 61 forms still to come in. We do realise that all of you have limited time to get such tasks done, but your urgent attention would be hugely appreciated, especially this year, with the backlog of work we are dealing with, in the office here. They are all available online at: http://edinburgh.anglican.org/resources-diocesan-office-forms/ ALL News from the Youth and Children Officer REFRESH! Training for Sunday School Leaders [pic of poster attached] Places are still available for this free training event, which will equip, encourage and inspire new and established Sunday School leaders. Further details and booking here Contact Claire Benton-Evans for further details at [email protected] TREASURERS QUOTA & PAYROLL As we currently have no Diocesan Treasurer, we have been re- arranging many of the tasks in that role. One of these is the oversight of Direct Debits for quota and payroll. -

Follies Collection of Anthony J

Follies Collection of Anthony J. Mazzaschi Inventory Updated February 28, 2017 Frame Description Year Company/Theatre City State Country Notes Number Display Script of 2011 Kennedy Center Washington DC USA Signed by entire cast. Box Bernadette Peters Purchased from Broadway Cares/Equity Fights AIDS via E-Bay auction. Display Conductor’s Score 1971 Original Production New York NY USA Custom Bound; gift of Box Mathilda Pincus, copyist, to Thomas Z. Shepherd, producer; inscribed with a personal note from Pincus to Shepherd 1 Program 1998 Signature Theatre Arlington VA USA 2 Flyer 1987 Shaftesbury Theatre London UK 3 Album 1971 Original Cast New York NY USA 4 Program 2007 Key West Pops Key West FL USA Also one page cast insert 5 Poster 2009 Arlington Players Arlington VA USA Printed from a PDF 5 Program 2009 Arlington Players Arlington VA USA 6 Magazine 2001 Sondheim Review Chicago IL USA Spring issue 7 Book Dust Jacket 2003 Everything Was USA By Ted Chapin, published by Possible Knopf 8 Poster 2007 Encores! New York NY USA Standard version 9 Poster 1971 Original Production New York NY USA Original. Some damage. 10 Poster 2004 California Irvine CA USA Autographed by cast Conservatory of the Arts 11 Album 1987 Original London London UK Silver version, Shaftesbury Cast cast 1 Frame Description Year Company/Theatre City State Country Notes Number 12 Album 1985 Lincoln Center New York NY USA Autographed by Sondheim, Concert Cook, and Stritch 13 Invitation 1987 First night party at London UK Numbered (but not visible) Tony’s 13 Invitation 1987 First night party at London UK Numbered (but not visible) Tony’s Book Invitation 1987 First night party at London UK Tony’s 14 Brochure 1987 Shaftesbury Theatre London UK Framed with front and back covers visible 15 Program 1987 Shaftesbury Theatre London UK White curtain (preview) version- Marked “18-7-87” – three days before official opening. -

Take Your Place 2016

FOR PERFORMERS AND THOSE WHO MAKE PERFORMANCE POSSIBLE THE PLACE THE PROGRAMMES THE PATHWAY THE PASSION TAKE YOUR PLACE 2016 Backstage in our Paul McCartney Auditorium, you can see some of our degree level students in the integrated roles needed to make a performance happen. Oliver Bush working as the lighting designer (studying Theatre and Performance Technology) Katy Lord providing stage management (studying Theatre and Performance Technology) Alfie Heywood assisting costume design and make-up (studying Theatre and Performance Design) Connor Dye one of the performers in the show (studying Acting) Alice Smith working as the costume designer (studying Theatre and Performance Design) Sophia Hardman working on live sound (studying Sound Technology) Guy Turner playing in the pit band (studying Music) Sophie Lane working as the manager for the musician (studying Music, Theatre and Entertainment Management) THE PLACE 02 Contents The Place What was our challenge and what is yours? 03 How did we respond to the challenge initially? 03 Hearing from the best 04 What do we do now? 05 Our curriculum 05 Our teachers 08 Our resources 10 Do we meet the challenge? 14 Will you join us? 16 An international outlook 17 Student support 18 Doing your own thing 19 Life in Liverpool 20 Where you live 22 The Programmes Foundation Certificates Acting and Musical Theatre 25 Commercial Dance 27 Popular Music and Sound Technology 29 Degrees Acting 31 Applied Theatre and Community Drama 33 Dance 35 Music 37 Music, Theatre and Entertainment 39 Management Sound Technology 41 Theatre and Performance Design 43 Theatre and Performance Technology 45 These programmes are awarded by The Pathway Entry requirements 49 How and when to apply 54 What happens after you have applied 58 What it costs 59 How to find us 61 Open days 61 Supporters 62 03 THE PLACE Our Founding Principal/CEO, Mark Featherstone-Witty, explains what we do and what we can offer you from this page to page 16 1 Sustained work for performers and those who make What was our performance possible.