EE 5211 Analog Integrated Circuit Design

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Chapter 7: AC Transistor Amplifiers

Chapter 7: Transistors, part 2 Chapter 7: AC Transistor Amplifiers The transistor amplifiers that we studied in the last chapter have some serious problems for use in AC signals. Their most serious shortcoming is that there is a “dead region” where small signals do not turn on the transistor. So, if your signal is smaller than 0.6 V, or if it is negative, the transistor does not conduct and the amplifier does not work. Design goals for an AC amplifier Before moving on to making a better AC amplifier, let’s define some useful terms. We define the output range to be the range of possible output voltages. We refer to the maximum and minimum output voltages as the rail voltages and the output swing is the difference between the rail voltages. The input range is the range of input voltages that produce outputs which are not at either rail voltage. Our goal in designing an AC amplifier is to get an input range and output range which is symmetric around zero and ensure that there is not a dead region. To do this we need make sure that the transistor is in conduction for all of our input range. How does this work? We do it by adding an offset voltage to the input to make sure the voltage presented to the transistor’s base with no input signal, the resting or quiescent voltage , is well above ground. In lab 6, the function generator provided the offset, in this chapter we will show how to design an amplifier which provides its own offset. -

Electronic Circuit Design and Component Selecjon

Electronic circuit design and component selec2on Nan-Wei Gong MIT Media Lab MAS.S63: Design for DIY Manufacturing Goal for today’s lecture • How to pick up components for your project • Rule of thumb for PCB design • SuggesMons for PCB layout and manufacturing • Soldering and de-soldering basics • Small - medium quanMty electronics project producMon • Homework : Design a PCB for your project with a BOM (bill of materials) and esMmate the cost for making 10 | 50 |100 (PCB manufacturing + assembly + components) Design Process Component Test Circuit Selec2on PCB Design Component PCB Placement Manufacturing Design Process Module Test Circuit Selec2on PCB Design Component PCB Placement Manufacturing Design Process • Test circuit – bread boarding/ buy development tools (breakout boards) / simulaon • Component Selecon– spec / size / availability (inventory! Need 10% more parts for pick and place machine) • PCB Design– power/ground, signal traces, trace width, test points / extra via, pads / mount holes, big before small • PCB Manufacturing – price-Mme trade-off/ • Place Components – first step (check power/ground) -- work flow Test Circuit Construc2on Breadboard + through hole components + Breakout boards Breakout boards, surcoards + hookup wires Surcoard : surface-mount to through hole Dual in-line (DIP) packaging hap://www.beldynsys.com/cc521.htm Source : hap://en.wikipedia.org/wiki/File:Breadboard_counter.jpg Development Boards – good reference for circuit design and component selec2on SomeMmes, it can be cheaper to pair your design with a development -

Basic DC Motor Circuits

Basic DC Motor Circuits Living with the Lab Gerald Recktenwald Portland State University [email protected] DC Motor Learning Objectives • Explain the role of a snubber diode • Describe how PWM controls DC motor speed • Implement a transistor circuit and Arduino program for PWM control of the DC motor • Use a potentiometer as input to a program that controls fan speed LWTL: DC Motor 2 What is a snubber diode and why should I care? Simplest DC Motor Circuit Connect the motor to a DC power supply Switch open Switch closed +5V +5V I LWTL: DC Motor 4 Current continues after switch is opened Opening the switch does not immediately stop current in the motor windings. +5V – Inductive behavior of the I motor causes current to + continue to flow when the switch is opened suddenly. Charge builds up on what was the negative terminal of the motor. LWTL: DC Motor 5 Reverse current Charge build-up can cause damage +5V Reverse current surge – through the voltage supply I + Arc across the switch and discharge to ground LWTL: DC Motor 6 Motor Model Simple model of a DC motor: ❖ Windings have inductance and resistance ❖ Inductor stores electrical energy in the windings ❖ We need to provide a way to safely dissipate electrical energy when the switch is opened +5V +5V I LWTL: DC Motor 7 Flyback diode or snubber diode Adding a diode in parallel with the motor provides a path for dissipation of stored energy when the switch is opened +5V – The flyback diode allows charge to dissipate + without arcing across the switch, or without flowing back to ground through the +5V voltage supply. -

Understanding Performance Numbers in Integrated Circuit Design Oprecomp Summer School 2019, Perugia Italy 5 September 2019

Understanding performance numbers in Integrated Circuit Design Oprecomp summer school 2019, Perugia Italy 5 September 2019 Frank K. G¨urkaynak [email protected] Integrated Systems Laboratory Introduction Cost Design Flow Area Speed Area/Speed Trade-offs Power Conclusions 2/74 Who Am I? Born in Istanbul, Turkey Studied and worked at: Istanbul Technical University, Istanbul, Turkey EPFL, Lausanne, Switzerland Worcester Polytechnic Institute, Worcester MA, USA Since 2008: Integrated Systems Laboratory, ETH Zurich Director, Microelectronics Design Center Senior Scientist, group of Prof. Luca Benini Interests: Digital Integrated Circuits Cryptographic Hardware Design Design Flows for Digital Design Processor Design Open Source Hardware Integrated Systems Laboratory Introduction Cost Design Flow Area Speed Area/Speed Trade-offs Power Conclusions 3/74 What Will We Discuss Today? Introduction Cost Structure of Integrated Circuits (ICs) Measuring performance of ICs Why is it difficult? EDA tools should give us a number Area How do people report area? Is that fair? Speed How fast does my circuit actually work? Power These days much more important, but also much harder to get right Integrated Systems Laboratory The performance establishes the solution space Finally the cost sets a limit to what is possible Introduction Cost Design Flow Area Speed Area/Speed Trade-offs Power Conclusions 4/74 System Design Requirements System Requirements Functionality Functionality determines what the system will do Integrated Systems Laboratory Finally the cost sets a limit -

Analog Integrated Circuit Design, 2Nd Edition

ffirs.fm Page iv Thursday, October 27, 2011 11:41 AM ffirs.fm Page i Thursday, October 27, 2011 11:41 AM ANALOG INTEGRATED CIRCUIT DESIGN Tony Chan Carusone David A. Johns Kenneth W. Martin John Wiley & Sons, Inc. ffirs.fm Page ii Thursday, October 27, 2011 11:41 AM VP and Publisher Don Fowley Associate Publisher Dan Sayre Editorial Assistant Charlotte Cerf Senior Marketing Manager Christopher Ruel Senior Production Manager Janis Soo Senior Production Editor Joyce Poh This book was set in 9.5/11.5 Times New Roman PSMT by MPS Limited, a Macmillan Company, and printed and bound by RRD Von Hoffman. The cover was printed by RRD Von Hoffman. This book is printed on acid free paper. Founded in 1807, John Wiley & Sons, Inc. has been a valued source of knowledge and understanding for more than 200 years, helping people around the world meet their needs and fulfill their aspirations. Our company is built on a foundation of principles that include responsibility to the communities we serve and where we live and work. In 2008, we launched a Corporate Citizenship Initiative, a global effort to address the environmental, social, economic, and ethical challenges we face in our business. Among the issues we are addressing are carbon impact, paper specifications and procurement, ethical conduct within our business and among our vendors, and community and charitable support. For more information, please visit our website: www.wiley.com/go/citizenship. Copyright © 2012 John Wiley & Sons, Inc. All rights reserved. No part of this publication may be reproduced, stored in a retrieval system or transmitted in any form or by any means, electronic, mechanical, photocopying, recording, scanning or otherwise, except as permitted under Sections 107 or 108 of the 1976 United States Copyright Act, without either the prior written permission of the Publisher, or authorization through payment of the appropriate per-copy fee to the Copyright Clearance Center, Inc. -

Chap01: Computer Abstractions and Technology

CHAPTER 1 Computer Abstractions and Technology 1.1 Introduction 3 1.2 Eight Great Ideas in Computer Architecture 11 1.3 Below Your Program 13 1.4 Under the Covers 16 1.5 Technologies for Building Processors and Memory 24 1.6 Performance 28 1.7 The Power Wall 40 1.8 The Sea Change: The Switch from Uniprocessors to Multiprocessors 43 1.9 Real Stuff: Benchmarking the Intel Core i7 46 1.10 Fallacies and Pitfalls 49 1.11 Concluding Remarks 52 1.12 Historical Perspective and Further Reading 54 1.13 Exercises 54 CMPS290 Class Notes (Chap01) Page 1 / 24 by Kuo-pao Yang 1.1 Introduction 3 Modern computer technology requires professionals of every computing specialty to understand both hardware and software. Classes of Computing Applications and Their Characteristics Personal computers o A computer designed for use by an individual, usually incorporating a graphics display, a keyboard, and a mouse. o Personal computers emphasize delivery of good performance to single users at low cost and usually execute third-party software. o This class of computing drove the evolution of many computing technologies, which is only about 35 years old! Server computers o A computer used for running larger programs for multiple users, often simultaneously, and typically accessed only via a network. o Servers are built from the same basic technology as desktop computers, but provide for greater computing, storage, and input/output capacity. Supercomputers o A class of computers with the highest performance and cost o Supercomputers consist of tens of thousands of processors and many terabytes of memory, and cost tens to hundreds of millions of dollars. -

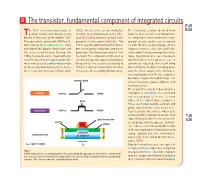

The Transistor, Fundamental Component of Integrated Circuits

D The transistor, fundamental component of integrated circuits he first transistor was made in (SiO2), which serves as an insulator. The transistor, a name derived from Tgermanium by John Bardeen and In 1958, Jack Kilby invented the inte- transfer and resistor, is a fundamen- Walter H. Brattain, in December 1947. grated circuit by manufacturing 5 com- tal component of microelectronic inte- The year after, along with William B. ponents on the same substrate. The grated circuits, and is set to remain Shockley at Bell Laboratories, they 1970s saw the advent of the first micro- so with the necessary changes at the developed the bipolar transistor and processor, produced by Intel and incor- nanoelectronics scale: also well-sui- the associated theory. During the porating 2,250 transistors, and the first ted to amplification, among other func- 1950s, transistors were made with sili- memory. The complexity of integrated tions, it performs one essential basic con (Si), which to this day remains the circuits has grown exponentially (dou- function which is to open or close a most widely-used semiconductor due bling every 2 to 3 years according to current as required, like a switching to the exceptional quality of the inter- “Moore's law”) as transistors continue device (Figure). Its basic working prin- face created by silicon and silicon oxide to become increasingly miniaturized. ciple therefore applies directly to pro- cessing binary code (0, the current is blocked, 1 it goes through) in logic cir- control gate cuits (inverters, gates, adders, and memory cells). The transistor, which is based on the switch source drain transport of electrons in a solid and not in a vacuum, as in the electron gate tubes of the old triodes, comprises three electrodes (anode, cathode and gate), two of which serve as an elec- transistor source drain tron reservoir: the source, which acts as the emitter filament of an electron gate insulator tube, the drain, which acts as the col- source lector plate, with the gate as “control- gate drain ler”. -

A General CAD Concept and Design Framework Architecture for Integrated Microsystems^

Transactions on the Built Environment vol 12, © 1995 WIT Press, www.witpress.com, ISSN 1743-3509 A general CAD concept and design framework architecture for integrated microsystems^ A. Poppe," J.M. Kararn,*) K. Hoffmann," M. Rencz/ B. Courtois,^ M. Glesner/V. Szekely" "Technical University of Budapest, Department of Electron Devices, H-1521 Budapest, Hungary *77M4/77MC, 46 av. F ^bZ/eA F-J&OJ7 GrgMo6/g Ce^x, France *THDarmstadt, Institute of Microelectronic Systems, D-64283 Darmstadt, Germany Abstract Besides foundry facilities, CAD-tools are also required to move microsystems from research prototypes to an industrial market. CAD tools of microelectronics have been developed for more than 20 years, both in the field of circuit design tools and in the area of TCAD tools. Usually a microelectronics engineer is involved only in one side of the design: either he deals with application design or he is par- ticipating in the manufacturing design, but not in both. This is one point that is to be followed in case of microsystem design, if higher level of design productivity is expected. Another point is that certain standards should also be established in case of microsystem design too: based on selected technologies a set of stan- dard components should be pre-designed and collected in a standard component library. This component library should be available from within microsystem de- sign frameworks which might be well established by a proper configuration and extension of existing 1C design frameworks. A very important point is the devel- opment of proper simulation models of microsystem components that are based on e.g. -

Circuit System Design Cards: a System Design Methodology for Circuits Courses Based on Thévenin Equivalents Neil E

Circuit System Design Cards: a system design methodology for circuits courses based on Thévenin equivalents Neil E. Cotter, Member, IEEE, and Cynthia Furse, Fellow, IEEE Abstract—The Circuit System Design cards described here signal being processed in the system design is the Thévenin allow students to design complete circuits with sensors and op- equivalent voltage rather than the circuit output voltage per se. amps by laying down a sequence of cards. The cards teach Furthermore, the Thévenin equivalent may be extended from students several important concepts: system design, Thevénin one card to the next, moving left-to-right, with pre-calculated equivalents, input/output resistance, and op-amp formulas. formulas. Students may design circuits by viewing them as combinations of system building blocks portrayed on one side of the cards. The This paper discusses how the cards are used and the theory other side of each card shows a circuit schematic for the building on which they are based. The next section discusses one card block. Thevénin equivalents are the crucial ingredient in tying in detail, and the following section discusses a two-card the circuits to the building blocks and vice versa. system. The final sections catalog the symbols incorporated on the cards and the entire set of card images. Index Terms—Linear, circuit, system design, cards, Thevénin equivalent II ONE-CARD EXAMPLE I INTRODUCTION One side of each CSD card shows a system view of how the card processes its input signal. Fig. 1(a) shows the system HE deck of 32 Circuit System Design (CSD) cards allows side of the Voltage Reference card that produces an output users to design complete circuits by laying down cards in T voltage, v , from a power supply voltage, V . -

Photovoltaic Couplers for MOSFET Drive for Relays

Photocoupler Application Notes Basic Electrical Characteristics and Application Circuit Design of Photovoltaic Couplers for MOSFET Drive for Relays Outline: Photovoltaic-output photocouplers(photovoltaic couplers), which incorporate a photodiode array as an output device, are commonly used in combination with a discrete MOSFET(s) to form a semiconductor relay. This application note discusses the electrical characteristics and application circuits of photovoltaic-output photocouplers. ©2019 1 Rev. 1.0 2019-04-25 Toshiba Electronic Devices & Storage Corporation Photocoupler Application Notes Table of Contents 1. What is a photovoltaic-output photocoupler? ............................................................ 3 1.1 Structure of a photovoltaic-output photocoupler .................................................... 3 1.2 Principle of operation of a photovoltaic-output photocoupler .................................... 3 1.3 Basic usage of photovoltaic-output photocouplers .................................................. 4 1.4 Advantages of PV+MOSFET combinations ............................................................. 5 1.5 Types of photovoltaic-output photocouplers .......................................................... 7 2. Major electrical characteristics and behavior of photovoltaic-output photocouplers ........ 8 2.1 VOC-IF characteristics .......................................................................................... 9 2.2 VOC-Ta characteristic ........................................................................................ -

COSC 6385 Computer Architecture - Multi-Processors (IV) Simultaneous Multi-Threading and Multi-Core Processors Edgar Gabriel Spring 2011

COSC 6385 Computer Architecture - Multi-Processors (IV) Simultaneous multi-threading and multi-core processors Edgar Gabriel Spring 2011 Edgar Gabriel Moore’s Law • Long-term trend on the number of transistor per integrated circuit • Number of transistors double every ~18 month Source: http://en.wikipedia.org/wki/Images:Moores_law.svg COSC 6385 – Computer Architecture Edgar Gabriel 1 What do we do with that many transistors? • Optimizing the execution of a single instruction stream through – Pipelining • Overlap the execution of multiple instructions • Example: all RISC architectures; Intel x86 underneath the hood – Out-of-order execution: • Allow instructions to overtake each other in accordance with code dependencies (RAW, WAW, WAR) • Example: all commercial processors (Intel, AMD, IBM, SUN) – Branch prediction and speculative execution: • Reduce the number of stall cycles due to unresolved branches • Example: (nearly) all commercial processors COSC 6385 – Computer Architecture Edgar Gabriel What do we do with that many transistors? (II) – Multi-issue processors: • Allow multiple instructions to start execution per clock cycle • Superscalar (Intel x86, AMD, …) vs. VLIW architectures – VLIW/EPIC architectures: • Allow compilers to indicate independent instructions per issue packet • Example: Intel Itanium series – Vector units: • Allow for the efficient expression and execution of vector operations • Example: SSE, SSE2, SSE3, SSE4 instructions COSC 6385 – Computer Architecture Edgar Gabriel 2 Limitations of optimizing a single instruction -

Fundamentals of MOSFET and IGBT Gate Driver Circuits

Application Report SLUA618A–March 2017–Revised October 2018 Fundamentals of MOSFET and IGBT Gate Driver Circuits Laszlo Balogh ABSTRACT The main purpose of this application report is to demonstrate a systematic approach to design high performance gate drive circuits for high speed switching applications. It is an informative collection of topics offering a “one-stop-shopping” to solve the most common design challenges. Therefore, it should be of interest to power electronics engineers at all levels of experience. The most popular circuit solutions and their performance are analyzed, including the effect of parasitic components, transient and extreme operating conditions. The discussion builds from simple to more complex problems starting with an overview of MOSFET technology and switching operation. Design procedure for ground referenced and high side gate drive circuits, AC coupled and transformer isolated solutions are described in great details. A special section deals with the gate drive requirements of the MOSFETs in synchronous rectifier applications. For more information, see the Overview for MOSFET and IGBT Gate Drivers product page. Several, step-by-step numerical design examples complement the application report. This document is also available in Chinese: MOSFET 和 IGBT 栅极驱动器电路的基本原理 Contents 1 Introduction ................................................................................................................... 2 2 MOSFET Technology ......................................................................................................