AMD Processor Recognition Application Note

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Thermal Interface Material Comparison: Thermal Pads Vs

Thermal Interface Material Comparison: Thermal Pads vs. Thermal Grease Publication # 26951 Revision: 3.00 Issue Date: April 2004 © 2004 Advanced Micro Devices, Inc. All rights reserved. The contents of this document are provided in connection with Advanced Micro Devices, Inc. (“AMD”) products. AMD makes no representations or warranties with respect to the accuracy or completeness of the contents of this publication and reserves the right to make changes to specifications and product descriptions at any time without notice. No license, whether express, implied, arising by estoppel, or otherwise, to any intellectual property rights are granted by this publication. Except as set forth in AMD’s Standard Terms and Conditions of Sale, AMD assumes no liability whatsoever, and disclaims any express or implied warranty, relating to its products including, but not limited to, the implied warranty of merchantability, fitness for a particular purpose, or infringement of any intellectual property right. AMD’s products are not designed, intended, authorized or warranted for use as components in systems intended for surgical implant into the body, or in other applications intended to support or sustain life, or in any other application in which the failure of AMD’s product could create a situation where personal injury, death, or severe property or environmental damage may occur. AMD reserves the right to discontinue or make changes to its products at any time without notice. Trademarks AMD, the AMD Arrow logo, AMD Athlon, AMD Duron, AMD Opteron and combinations thereof, are trademarks of Advanced Micro Devices, Inc. Other product names used in this publication are for identification purposes only and may be trademarks of their respective companies. -

Super 7™ Motherboard

SY-5EH5/5EHM V1.0 Super 7Ô Motherboard ************************************************ Pentium® Class CPU supported ETEQ82C663 PCI/AGP Motherboard AT Form Factor ************************************************ User's Guide & Technical Reference NSTL “Year 2000 Test” Certification Letter September 23, 1998 Testing Date: September 23, 1998 Certification Date: September 23, 1998 Certification Number: NCY2000-980923-004 To Whom It May Concern: We are please to inform you that the “SY-5EHM/5EH5” system has passed NSTL Year 2000 certification test program. The Year 2000 test program tests a personal computer for its ability to support the year 2000. The “SY-5EHM/5EH5: system is eligible to carry the NSTL :Year 2000 Certification” seal. The Year 2000 certification test has been done under the following system configuration: Company Name : SOYO COMPUTER INC. System Model Name : SY-5EHM/5EH5 Hardware Revision : N/A CPU Model : Intel Pentium 200/66Mhz On Board Memory/L2 Cache : PC100 SDRAM DIMM 32MBx1 /1MB System BIOS : Award Modular BIOS V4.51PG, An Energy Star Ally Copyright © 1984—98, EH-1A6,07/15/1998-VP3-586B- 8669-2A5LES2AC-00 Best regards, SPORTON INTERNATIONAL INC. Declaration of Conformity According to 47 CFR, Part 2 and 15 of the FCC Rules Declaration No.: D872907 July.10 1998 The following designated product EQUIPMENT: Main Board MODEL NO.: SY-5EH Which is the Class B digital device complies with 47 CFR Parts 2 and 15 of the FCC rules. Operation is subject to the following two conditions : (1) this device may not cause harmful interference, and (2) this device must accept any interference received, including interference that may cause undesired operation. -

2021 User Guide

i Pro Fortran Linux Absoft Pro Fortran User Guide Absoft Fortran Linux Fortran User Guide 5119 Highland Road, PMB 398 Waterford, MI 48327 U.S.A. Tel (248) 220-1190 Fax (248) 220-1194 [email protected] All rights reserved. No part of this publication may be reproduced or used in any form by any means, without the prior written permission of Absoft Corporation. THE INFORMATION CONTAINED IN THIS PUBLICATION IS BELIEVED TO BE ACCURATE AND RELIABLE. HOWEVER, ABSOFT CORPORATION MAKES NO REPRESENTATION OF WARRANTIES WITH RESPECT TO THE PROGRAM MATERIAL DESCRIBED HEREIN AND SPECIFICALLY DISCLAIMS ANY IMPLIED WARRANTIES OF MERCHANTABILITY OR FITNESS FOR ANY PARTICULAR PURPOSE. FURTHER, ABSOFT RESERVES THE RIGHT TO REVISE THE PROGRAM MATERIAL AND MAKE CHANGES THEREIN FROM TIME TO TIME WITHOUT OBLIGATION TO NOTIFY THE PURCHASER OF THE REVISION OR CHANGES. IN NO EVENT SHALL ABSOFT BE LIABLE FOR ANY INCIDENTAL, INDIRECT, SPECIAL OR CONSEQUENTIAL DAMAGES ARISING OUT OF THE PURCHASER'S USE OF THE PROGRAM MATERIAL. U.S. GOVERNMENT RESTRICTED RIGHTS — The software and documentation are provided with RESTRICTED RIGHTS. Use, duplication, or disclosure by the Government is subject to restrictions set forth in subparagraph (c) (1) (ii) of the Rights in Technical Data and Computer Software clause at 252.227-7013. The contractor is Absoft Corporation, 2111 Cass Lake Rd. Ste 102, Keego Harbor, Michigan 48320. ABSOFT CORPORATION AND ITS LICENSOR(S) MAKE NO WARRANTIES, EXPRESS OR IMPLIED, INCLUDING WITHOUT LIMITATION THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE, REGARDING THE SOFTWARE. ABSOFT AND ITS LICENSOR(S) DO NOT WARRANT, GUARANTEE OR MAKE ANY REPRESENTATIONS REGARDING THE USE OR THE RESULTS OF THE USE OF THE SOFTWARE IN TERMS OF ITS CORRECTNESS, ACCURACY, RELIABILITY, CURRENTNESS, OR OTHERWISE. -

A Superscalar Out-Of-Order X86 Soft Processor for FPGA

A Superscalar Out-of-Order x86 Soft Processor for FPGA Henry Wong University of Toronto, Intel [email protected] June 5, 2019 Stanford University EE380 1 Hi! ● CPU architect, Intel Hillsboro ● Ph.D., University of Toronto ● Today: x86 OoO processor for FPGA (Ph.D. work) – Motivation – High-level design and results – Microarchitecture details and some circuits 2 FPGA: Field-Programmable Gate Array ● Is a digital circuit (logic gates and wires) ● Is field-programmable (at power-on, not in the fab) ● Pre-fab everything you’ll ever need – 20x area, 20x delay cost – Circuit building blocks are somewhat bigger than logic gates 6-LUT6-LUT 6-LUT6-LUT 3 6-LUT 6-LUT FPGA: Field-Programmable Gate Array ● Is a digital circuit (logic gates and wires) ● Is field-programmable (at power-on, not in the fab) ● Pre-fab everything you’ll ever need – 20x area, 20x delay cost – Circuit building blocks are somewhat bigger than logic gates 6-LUT 6-LUT 6-LUT 6-LUT 4 6-LUT 6-LUT FPGA Soft Processors ● FPGA systems often have software components – Often running on a soft processor ● Need more performance? – Parallel code and hardware accelerators need effort – Less effort if soft processors got faster 5 FPGA Soft Processors ● FPGA systems often have software components – Often running on a soft processor ● Need more performance? – Parallel code and hardware accelerators need effort – Less effort if soft processors got faster 6 FPGA Soft Processors ● FPGA systems often have software components – Often running on a soft processor ● Need more performance? – Parallel -

AMD-K5TM Processor

AMD-K5TM Processor Data Sheet Publication # 18522 Rev: F Amendment/0 Issue Date: January 1997 This document contains information on a product under development at AMD. The information is intended to help you evaluate this product. AMD reserves the right to change or discontinue work on this proposed product without notice. © 1997 Advanced Micro Devices, Inc. All Rights Reserved. Advanced Micro Devices, Inc. ("AMD") reserves the right to make changes in its products without notice in order to improve design or performance charac- teristics. The information in this publication is believed to be accurate at the time of publication, but AMD makes no representations or warranties with respect to the accuracy or completeness of the contents of this publication or the information contained herein, and reserves the right to make changes at any time, without notice. AMD disclaims responsibility for any consequences resulting from the use of the information included in this publication. This publication neither states nor implies any representations or warranties of any kind, including but not limited to, any implied warranty of merchantability or fitness for a particular purpose. AMD products are not authorized for use as critical components in life support devices or systems without AMD’s written approval. AMD assumes no liability whatsoever for claims associated with the sale or use (including the use of engineering samples) of AMD products except as provided in AMD’s Terms and Conditions of Sale for such product. Trademarks: AMD, the AMD logo, and combinations thereof are trademarks of Advanced Micro Devices, Inc. Am486 is a registered trademark, and AMD-K5 is a trademark of Advanced Micro Devices, Inc. -

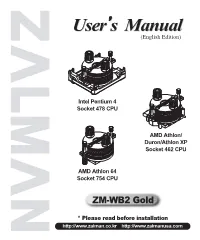

User's Manual User's Manual

User’s Manual (English Edition) Intel Pentium 4 Socket 478 CPU AMD Athlon/ Duron/Athlon XP Socket 462 CPU AMD Athlon 64 Socket 754 CPU ZM-WB2 Gold * Please read before installation http://www.zalman.co.kr http://www.zalmanusa.com 1. Features 1) Gold plated pure copper base maximizes cooling performance and prevents CPU blocks from galvanic corrosion 2) Intel Pentium 4 (Socket 478), AMD Athlon/Duron/Athlon XP (Socket 462),Athlon 64 (Socket 754) compatible design for broad compatibility. 3) Three types of compression fitting are offered for use with water tubes (8X10mm,8X11mm,10X13mm) * Zalman Tech. Co., Ltd. is not responsible for any damage resulting from CPU OVERCLOCKING. 2. Specifications Part No Part name Q’ ty Weight (g) Use 1 CPU block 1 447.0 CPU mountimg 2 Hand screw 2 8.0 Clip mountimg 3 Thermal grease 1 1.8 Apply to cpu core 4 Clip 1 9.6 CPU block mountimg 5 User’s manual 1 6 Clip supports 2 8.2 Socket 478 7 Clip supports A 2 5.0 Socket 462 8 Clip supports B 2 5.0 Socket 462 9 Bolts 4 0.8 Clip supports, A, B-type 10 Paper washer 1 set 7, 8 mountimg 11 Nipple 2 6.2 Socket 754 mountimg 12 Back plate 60.0 Socket 754 mountimg Fitting to 13 Fitting 3 set 8 x 10mm, 8 x 11mm, 10 x 13mm tubes NOTE 1) The maximum weight for the cooler is specified as 450g/450g/300g for socket 478/754/462 respectively. Special care should be taken when moving a computer equipped with a cooler which exceeds the relevant weight limit. -

System Management BIOS (SMBIOS) Reference 6 Specification

1 2 Document Number: DSP0134 3 Date: 2011-01-26 4 Version: 2.7.1 5 System Management BIOS (SMBIOS) Reference 6 Specification 7 Document Type: Specification 8 Document Status: DMTF Standard 9 Document Language: en-US 10 System Management BIOS (SMBIOS) Reference Specification DSP0134 11 Copyright Notice 12 Copyright © 2000, 2002, 2004–2011 Distributed Management Task Force, Inc. (DMTF). All rights 13 reserved. 14 DMTF is a not-for-profit association of industry members dedicated to promoting enterprise and systems 15 management and interoperability. Members and non-members may reproduce DMTF specifications and 16 documents, provided that correct attribution is given. As DMTF specifications may be revised from time to 17 time, the particular version and release date should always be noted. 18 Implementation of certain elements of this standard or proposed standard may be subject to third party 19 patent rights, including provisional patent rights (herein "patent rights"). DMTF makes no representations 20 to users of the standard as to the existence of such rights, and is not responsible to recognize, disclose, 21 or identify any or all such third party patent right, owners or claimants, nor for any incomplete or 22 inaccurate identification or disclosure of such rights, owners or claimants. DMTF shall have no liability to 23 any party, in any manner or circumstance, under any legal theory whatsoever, for failure to recognize, 24 disclose, or identify any such third party patent rights, or for such party’s reliance on the standard or 25 incorporation -

Élan™SC520 Microcontroller Data Sheet PRELIMINARY

PRELIMINARY Élan™SC520 Microcontroller Integrated 32-Bit Microcontroller with PC/AT-Compatible Peripherals, PCI Host Bridge, and Synchronous DRAM Controller DISTINCTIVE CHARACTERISTICS ■ ■ Industry-standard Am5x86® CPU with floating ROM/Flash controller for 8-, 16-, and 32-bit devices point unit (FPU) and 16-Kbyte write-back cache ■ Enhanced PC/AT-compatible peripherals – 100-MHz and 133-MHz operating frequencies provide improved performance – Low-voltage operation (core VCC = 2.5 V) – Enhanced programmable interrupt controller – 5-V tolerant I/O (3.3-V output levels) (PIC) prioritizes 22 interrupt levels (up to 15 external sources) with flexible routing ■ E86™ family of x86 embedded processors – Enhanced DMA controller includes double buffer – Part of a software-compatible family of chaining, extended address and transfer counts, microprocessors and microcontrollers well and flexible channel routing supported by a wide variety of development tools ■ – Two 16550-compatible UARTs operate at baud Integrated PCI host bridge controller leverages rates up to 1.15 Mbit/s with optional DMA interface standard peripherals and software ■ Standard PC/AT-compatible peripherals – 33 MHz, 32-bit PCI bus Revision 2.2-compliant – Programmable interval timer (PIT) – High-throughput 132-Mbyte/s peak transfer – Real-time clock (RTC) with battery backup – Supports up to five external PCI masters capability and 114 bytes of RAM – Integrated write-posting and read-buffering for ■ Additional integrated peripherals high-throughput applications – Three general-purpose -

AMD-K6-2® Processor

Preliminary Information ® Mobile AMD-K6-2® Processor Data Sheet Publication # 21896 Rev: E Amendment/0 Issue Date: May 2000 Preliminary Information © 2000 Advanced Micro Devices, Inc. All rights reserved. The contents of this document are provided in connection with Advanced Micro Devices, Inc. (“AMD”) products. AMD makes no representations or warranties with respect to the accuracy or completeness of the contents of this publication and reserves the right to make changes to specifications and product descriptions at any time without notice. No license, whether express, implied, arising by estoppel or otherwise, to any intellectual property rights is granted by this publication. Except as set forth in AMD’s Standard Terms and Conditions of Sale, AMD assumes no liability whatsoever, and disclaims any express or implied warranty, relating to its products including, but not limited to, the implied warranty of merchantability, fitness for a particular purpose, or infringement of any intellectual property right. AMD’s products are not designed, intended, authorized or warranted for use as components in systems intended for surgical implant into the body, or in other applications intended to support or sustain life, or in any other application in which the failure of AMD’s product could create a situation where personal injury, death, or severe property or environmental damage may occur. AMD reserves the right to discontinue or make changes to its products at any time without notice. Trademarks AMD, the AMD logo, K6, 3DNow!, and combinations thereof, and Super7 are trademarks, and AMD-K6 and RISC86 are registered trademarks of Advanced Micro Devices, Inc. MMX is a trademark of Intel Corporation. -

32-Bit Broch/4.0-8/23 (Page 3)

E86™ FAMILY 32-Bit Microprocessors www.amd.com 3 Leverage the billions of dollars spent annually developing hardware and software for the world's dominant processor architecture—x86 SECTION I • Assured, flexible, and x86 compatible migration path from 16-bit to full 32-bit bus design HIGH PERFORMANCE x86 EMBEDDED PROCESSORS • Industry standard x86 architecture The E86™ family of 32-bit microprocessors and microcontrollers represent the highest level of x86 performance that AMD currently offers for the embedded provides largest knowledge base market. This 32-bit family of devices includes the Am386®, Am486®, AMD-K6™E of designers microprocessors as well as the Élan™ family of integrated microcontrollers. Since all E86 family processors are x86 compatible, a software compatible • Enhanced performance and lower upgrade path for your next generation design is assured. And since the E86 family is based on the world’s dominant processor architecture - x86 - system costs embedded designers are also able to leverage the billions of dollars spent annually developing hardware and software for the PC market. Low cost • High level of integration that development tools, readily available chipsets and peripherals, and pre-written software are all benefits of utilizing the x86 architecture in your designs. reduces time-to-market and increases reliability HIGH PERFORMANCE 32-BIT MICROPROCESSOR PORTFOLIO Many customers require the leading edge performance of PC microproces- • A complete third-party support program sors, while still desiring the level of support that is typically associated with from AMD’s FusionE86sm partners. embedded processors. AMD’s Embedded Processor Division is chartered to provide these industry-proven CPU cores with the long-term product support, development tool infrastructure, and technical support that embedded cus- tomers have come to expect. -

Communication Theory II

Microprocessor (COM 9323) Lecture 2: Review on Intel Family Ahmed Elnakib, PhD Assistant Professor, Mansoura University, Egypt Feb 17th, 2016 1 Text Book/References Textbook: 1. The Intel Microprocessors, Architecture, Programming and Interfacing, 8th edition, Barry B. Brey, Prentice Hall, 2009 2. Assembly Language for x86 processors, 6th edition, K. R. Irvine, Prentice Hall, 2011 References: 1. Computer Architecture: A Quantitative Approach, 5th edition, J. Hennessy, D. Patterson, Elsevier, 2012. 2. The 80x86 Family, Design, Programming and Interfacing, 3rd edition, Prentice Hall, 2002 3. The 80x86 IBM PC and Compatible Computers, Assembly Language, Design, and Interfacing, 4th edition, M.A. Mazidi and J.G. Mazidi, Prentice Hall, 2003 2 Lecture Objectives 1. Provide an overview of the various 80X86 and Pentium family members 2. Define the contents of the memory system in the personal computer 3. Convert between binary, decimal, and hexadecimal numbers 4. Differentiate and represent numeric and alphabetic information as integers, floating-point, BCD, and ASCII data 5. Understand basic computer terminology (bit, byte, data, real memory system, protected mode memory system, Windows, DOS, I/O) 3 Brief History of the Computers o1946 The first generation of Computer ENIAC (Electrical and Numerical Integrator and Calculator) was started to be used based on the vacuum tube technology, University of Pennsylvania o1970s entire CPU was put in a single chip. (1971 the first microprocessor of Intel 4004 (4-bit data bus and 2300 transistors and 45 instructions) 4 Brief History of the Computers (cont’d) oLate 1970s Intel 8080/85 appeared with 8-bit data bus and 16-bit address bus and used from traffic light controllers to homemade computers (8085: 246 instruction set, RISC*) o1981 First PC was introduced by IBM with Intel 8088 (CISC**: over 20,000 instructions) microprocessor oMotorola emerged with 6800. -

AMD-K6 Processor Revision Guide As Errata Or Specification Changes/Clarifications and Are Available to Anyone Who Requests the Information

AMD-K6® Processor Revision Guide Model 7 Publication # 21846 Rev: H Amendment/0 Issue Date: June 1999 © 1999 Advanced Micro Devices, Inc. All rights reserved. The contents of this document are provided in connection with Advanced Micro Devices, Inc. ("AMD") products. AMD makes no representations or warranties with respect to the accuracy or completeness of the contents of this publication and reserves the right to make changes to specifications and product descriptions at any time without notice. No license, whether express, implied, arising by estoppel or otherwise, to any intellectual property rights is granted by this publication. Except as set forth in AMD's Standard Terms and Conditions of Sale, AMD assumes no liability whatsoever, and disclaims any express or implied warranty, relating to its products including, but not limited to, the implied warranty of merchantability, fitness for a particular purpose, or infringement of any intellectual property right. AMD's products are not designed, intended, authorized or warranted for use as components in systems intended for surgical implant into the body, or in other applications intended to support or sustain life, or in any other application in which the failure of AMD's product could create a situation where personal injury, death, or severe property or environmental damage may occur. AMD reserves the right to discontinue or make changes to its products at any time without notice. Trademarks AMD, the AMD logo, K6, and combinations thereof, K86, and Super7 are trademarks, and AMD-K6 is a registered trademark of Advanced Micro Devices, Inc. Microsoft and Windows are registered trademarks of Microsoft Corporation.