The Criminal Justice Microcomputer' Guide and Software Catalogue

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Analysis of Server-Smartphone Application Communication Patterns

View metadata, citation and similar papers at core.ac.uk brought to you by CORE provided by Aaltodoc Publication Archive Aalto University School of Science Degree Programme in Computer Science and Engineering Péter Somogyi Analysis of server-smartphone application communication patterns Master’s Thesis Budapest, June 15, 2014 Supervisors: Professor Jukka Nurminen, Aalto University Professor Tamás Kozsik, Eötvös Loránd University Instructor: Máté Szalay-Bekő, M.Sc. Ph.D. Aalto University School of Science ABSTRACT OF THE Degree programme in Computer Science and MASTER’S THESIS Engineering Author: Péter Somogyi Title: Analysis of server-smartphone application communication patterns Number of pages: 83 Date: June 15, 2014 Language: English Professorship: Data Communication Code: T-110 Software Supervisor: Professor Jukka Nurminen, Aalto University Professor Tamás Kozsik, Eötvös Loránd University Instructor: Máté Szalay-Bekő, M.Sc. Ph.D. Abstract: The spread of smartphone devices, Internet of Things technologies and the popularity of web-services require real-time and always on applications. The aim of this thesis is to identify a suitable communication technology for server and smartphone communication which fulfills the main requirements for transferring real- time data to the handheld devices. For the analysis I selected 3 popular communication technologies that can be used on mobile devices as well as from commonly used browsers. These are client polling, long polling and HTML5 WebSocket. For the assessment I developed an Android application that receives real-time sensor data from a WildFly application server using the aforementioned technologies. Industry specific requirements were selected in order to verify the usability of this communication forms. The first one covers the message size which is relevant because most smartphone users have limited data plan. -

IBM Z Systems Introduction May 2017

IBM z Systems Introduction May 2017 IBM z13s and IBM z13 Frequently Asked Questions Worldwide ZSQ03076-USEN-15 Table of Contents z13s Hardware .......................................................................................................................................................................... 3 z13 Hardware ........................................................................................................................................................................... 11 Performance ............................................................................................................................................................................ 19 z13 Warranty ............................................................................................................................................................................ 23 Hardware Management Console (HMC) ..................................................................................................................... 24 Power requirements (including High Voltage DC Power option) ..................................................................... 28 Overhead Cabling and Power ..........................................................................................................................................30 z13 Water cooling option .................................................................................................................................................... 31 Secure Service Container ................................................................................................................................................. -

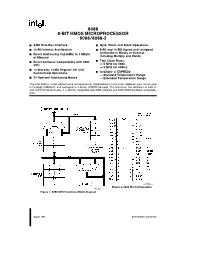

8088 8-Bit Hmos Microprocessor 8088 8088-2

8088 8-BIT HMOS MICROPROCESSOR 8088/8088-2 Y 8-Bit Data Bus Interface Y Byte, Word, and Block Operations Y 16-Bit Internal Architecture Y 8-Bit and 16-Bit Signed and Unsigned Arithmetic in Binary or Decimal, Y Direct Addressing Capability to 1 Mbyte of Memory Including Multiply and Divide Y Two Clock Rates: Y Direct Software Compatibility with 8086 CPU Ð 5 MHz for 8088 Ð 8 MHz for 8088-2 Y 14-Word by 16-Bit Register Set with Symmetrical Operations Y Available in EXPRESS Ð Standard Temperature Range Y 24 Operand Addressing Modes Ð Extended Temperature Range The Intel 8088 is a high performance microprocessor implemented in N-channel, depletion load, silicon gate technology (HMOS-II), and packaged in a 40-pin CERDIP package. The processor has attributes of both 8- and 16-bit microprocessors. It is directly compatible with 8086 software and 8080/8085 hardware and periph- erals. 231456±2 Figure 2. 8088 Pin Configuration 231456±1 Figure 1. 8088 CPU Functional Block Diagram August 1990 Order Number: 231456-006 8088 Table 1. Pin Description The following pin function descriptions are for 8088 systems in either minimum or maximum mode. The ``local bus'' in these descriptions is the direct multiplexed bus interface connection to the 8088 (without regard to additional bus buffers). Symbol Pin No. Type Name and Function AD7±AD0 9±16 I/O ADDRESS DATA BUS: These lines constitute the time multiplexed memory/IO address (T1) and data (T2, T3, Tw, T4) bus. These lines are active HIGH and float to 3-state OFF during interrupt acknowledge and local bus ``hold acknowledge''. -

Intel 8080 Datasheet

infel.. 8080A/8080A-1/8080A-2 8-BIT N-CHANNEL MICROPROCESSOR • TTL Drive Capability • Decimal, Binary, and Double Precision • 2,..,s (-1:1.3,..,s, -2:1.5 ,..,s) Instruction Arithmetic Cycle • Ability to Provide Priority Vectored • Powerful Problem Solving Instruction Interrupts Set • 512 Directly Addressed 110 Ports 6 General Purpose Registers and an Available In EXPRESS • Accumulator • - Standard Temperature Range 16-Blt Program Counter for Directly Available In 4Q-Lead Cerdlp and Plastic • Addressing up to 64K Bytes of Memory • Packages 16-Blt Stack Pointer and Stack (See Packaging Spec. Order #231369) • Manipulation Instructions for Rapid Switching of the Program Environment • The Intel 8080A is a complete 8-bit parallel central processing unit (CPU). It is fabricated on a single LSI chip using Intel's n-channel silicon gate MOS process. This offers the user a high performance solution to control and processing applications. The 8080A contains 6 8-bit general purpose working registers and an accumulator. The 6 general purpose registers may be addressed individually or in pairs providing both single and double precision operators. Arithmetic and logical instructions set or reset 4 testable flags. A fifth flag provides decimal arithmetic opera tion. The 8080A has an external stack feature wherein any portion of memory may be used as a last in/first out stack to store/retrieve the contents of the accumulator, flags, program counter, and all of the 6 general purpose registers. The 16-bit stack pointer controls the addressing of this external stack. This stack gives the 8080A the ability to easily handle multiple level priority interrupts by rapidly storing and restoring processor status. -

Implementation of Embedded Web Server Based on ARM11 and Linux Using Raspberry PI

International Journal of Recent Technology and Engineering (IJRTE) ISSN: 2277-3878, Volume-3 Issue-3, July 2014 Implementation of Embedded Web Server Based on ARM11 and Linux using Raspberry PI Girish Birajdar Abstract— As ARM processor based web servers not uses III. HARDWARE USED computer directly, it helps a lot in reduction of cost. In this We will use different hardware to implement this embedded project our aim is to implement an Embedded Web Server (EWS) based on ARM11 processor and Linux operating system using web server, which are described in this section. Raspberry Pi. it will provide a powerful networking solution with 1. Raspberry Pi : The Raspberry Pi is low cost ARM wide range of application areas over internet. We will run web based palm-size computer. The Raspberry Pi has server on an embedded system having limited resources to serve microprocessor ARM1176JZF-S which is a member of embedded web page to a web browser. ARM11 family and has ARMv6 architecture. It is build Index Terms— Embedded Web Server, Raspberry Pi, ARM, around a BCM2835 broadcom processor. ARM processor Ethernet etc. operates at 700 MHz & it has 512 MB RAM. It consumes 5V electricity at 1A current due to which power I. INTRODUCTION consumption of raspberry pi is less. It has many peripherals such as USB port, 10/100 ethernet, GPIO, HDMI & With evolution of World-Wide Web (WWW), its composite video outputs and SD card slot.SD card slot is application areas are increasing day by day. Web access used to connect the SD card which consist of raspberry linux functionality can be embedded in a low cost device which operating system. -

Computer Organization and Architecture Designing for Performance Ninth Edition

COMPUTER ORGANIZATION AND ARCHITECTURE DESIGNING FOR PERFORMANCE NINTH EDITION William Stallings Boston Columbus Indianapolis New York San Francisco Upper Saddle River Amsterdam Cape Town Dubai London Madrid Milan Munich Paris Montréal Toronto Delhi Mexico City São Paulo Sydney Hong Kong Seoul Singapore Taipei Tokyo Editorial Director: Marcia Horton Designer: Bruce Kenselaar Executive Editor: Tracy Dunkelberger Manager, Visual Research: Karen Sanatar Associate Editor: Carole Snyder Manager, Rights and Permissions: Mike Joyce Director of Marketing: Patrice Jones Text Permission Coordinator: Jen Roach Marketing Manager: Yez Alayan Cover Art: Charles Bowman/Robert Harding Marketing Coordinator: Kathryn Ferranti Lead Media Project Manager: Daniel Sandin Marketing Assistant: Emma Snider Full-Service Project Management: Shiny Rajesh/ Director of Production: Vince O’Brien Integra Software Services Pvt. Ltd. Managing Editor: Jeff Holcomb Composition: Integra Software Services Pvt. Ltd. Production Project Manager: Kayla Smith-Tarbox Printer/Binder: Edward Brothers Production Editor: Pat Brown Cover Printer: Lehigh-Phoenix Color/Hagerstown Manufacturing Buyer: Pat Brown Text Font: Times Ten-Roman Creative Director: Jayne Conte Credits: Figure 2.14: reprinted with permission from The Computer Language Company, Inc. Figure 17.10: Buyya, Rajkumar, High-Performance Cluster Computing: Architectures and Systems, Vol I, 1st edition, ©1999. Reprinted and Electronically reproduced by permission of Pearson Education, Inc. Upper Saddle River, New Jersey, Figure 17.11: Reprinted with permission from Ethernet Alliance. Credits and acknowledgments borrowed from other sources and reproduced, with permission, in this textbook appear on the appropriate page within text. Copyright © 2013, 2010, 2006 by Pearson Education, Inc., publishing as Prentice Hall. All rights reserved. Manufactured in the United States of America. -

45-Year CPU Evolution: One Law and Two Equations

45-year CPU evolution: one law and two equations Daniel Etiemble LRI-CNRS University Paris Sud Orsay, France [email protected] Abstract— Moore’s law and two equations allow to explain the a) IC is the instruction count. main trends of CPU evolution since MOS technologies have been b) CPI is the clock cycles per instruction and IPC = 1/CPI is the used to implement microprocessors. Instruction count per clock cycle. c) Tc is the clock cycle time and F=1/Tc is the clock frequency. Keywords—Moore’s law, execution time, CM0S power dissipation. The Power dissipation of CMOS circuits is the second I. INTRODUCTION equation (2). CMOS power dissipation is decomposed into static and dynamic powers. For dynamic power, Vdd is the power A new era started when MOS technologies were used to supply, F is the clock frequency, ΣCi is the sum of gate and build microprocessors. After pMOS (Intel 4004 in 1971) and interconnection capacitances and α is the average percentage of nMOS (Intel 8080 in 1974), CMOS became quickly the leading switching capacitances: α is the activity factor of the overall technology, used by Intel since 1985 with 80386 CPU. circuit MOS technologies obey an empirical law, stated in 1965 and 2 Pd = Pdstatic + α x ΣCi x Vdd x F (2) known as Moore’s law: the number of transistors integrated on a chip doubles every N months. Fig. 1 presents the evolution for II. CONSEQUENCES OF MOORE LAW DRAM memories, processors (MPU) and three types of read- only memories [1]. The growth rate decreases with years, from A. -

The Early Years of Academic Computing: L a Memoir by Douglas S

03 G A The Early Years of Academic Computing: L A Memoir by Douglas S. Gale E This is from a collection of reflections/memoirs concerning the early years of academic comput- ing, emphasizing the period when Cornell developed its own decentralized computing environ- ments and networking became a national strategic goal. ©2016 Henrietta Gale Initial Release: April 2016 (Increment 01) Second Release: April 2017 (Increments 02-04) Published by The Internet-First University Press Copy editor and proofreader: Dianne Ferriss The entire incremental book is openly available at http://hdl.handle.net/1813/36810 Books and Articles Collection – http://ecommons.library.cornell.edu/handle/1813/63 The Internet-First University Press – http://ecommons.library.cornell.edu/handle/1813/62 C. Memoir by Douglas S. Gale Preface and Introduction Bill Arms and Ken King have chronicled much of the early history of academic computing. Accordingly, I have tried to focus my contribution to The Early Years of Academic Computing on topics less covered by King and Arms. My contribution is organized into four chronological periods, roughly spanning the last 50 years of the 20th century, and each has an organizational theme: career transitions, the microcomputer revolution, the networking revolution, and the changing role of academic computing and networking. The theme of the first period -- career transitions -- will consider where the early practitioners of academic computing came from. Computer Science was first recognized as an academic discipline in 1962, and the early years of academic computing were led by people who had received their academic training in other disciplines. Many, if not most, came from the community of computer users and early adopters. -

Performance of a Computer (Chapter 4) Vishwani D

ELEC 5200-001/6200-001 Computer Architecture and Design Fall 2013 Performance of a Computer (Chapter 4) Vishwani D. Agrawal & Victor P. Nelson epartment of Electrical and Computer Engineering Auburn University, Auburn, AL 36849 ELEC 5200-001/6200-001 Performance Fall 2013 . Lecture 1 What is Performance? Response time: the time between the start and completion of a task. Throughput: the total amount of work done in a given time. Some performance measures: MIPS (million instructions per second). MFLOPS (million floating point operations per second), also GFLOPS, TFLOPS (1012), etc. SPEC (System Performance Evaluation Corporation) benchmarks. LINPACK benchmarks, floating point computing, used for supercomputers. Synthetic benchmarks. ELEC 5200-001/6200-001 Performance Fall 2013 . Lecture 2 Small and Large Numbers Small Large 10-3 milli m 103 kilo k 10-6 micro μ 106 mega M 10-9 nano n 109 giga G 10-12 pico p 1012 tera T 10-15 femto f 1015 peta P 10-18 atto 1018 exa 10-21 zepto 1021 zetta 10-24 yocto 1024 yotta ELEC 5200-001/6200-001 Performance Fall 2013 . Lecture 3 Computer Memory Size Number bits bytes 210 1,024 K Kb KB 220 1,048,576 M Mb MB 230 1,073,741,824 G Gb GB 240 1,099,511,627,776 T Tb TB ELEC 5200-001/6200-001 Performance Fall 2013 . Lecture 4 Units for Measuring Performance Time in seconds (s), microseconds (μs), nanoseconds (ns), or picoseconds (ps). Clock cycle Period of the hardware clock Example: one clock cycle means 1 nanosecond for a 1GHz clock frequency (or 1GHz clock rate) CPU time = (CPU clock cycles)/(clock rate) Cycles per instruction (CPI): average number of clock cycles used to execute a computer instruction. -

DLP Discovery 4100 Development Kit Software User's Guide (Rev. A)

DLP® Discovery™ 4100 Development Platform User's Guide Literature Number: DLPU040A October 2016–Revised November 2018 Contents Revision History ........................................................................................................................... 6 Preface ........................................................................................................................................ 7 1 Overview............................................................................................................................. 9 1.1 The DLP Discovery 4100 Development Platform ...................................................................... 11 1.2 DLP Discovery 4100 Development Platform Photo.................................................................... 13 1.3 Key Components ........................................................................................................... 14 1.3.1 Xilinx Virtex 5 APPSFPGA ....................................................................................... 14 1.3.2 DLPC410 - Digital Controller for DLP Discovery 4100 Chipset ............................................. 14 1.3.3 DLPA200 - DMD Micromirror Driver ............................................................................ 14 1.3.4 DLPR410 - Configuration PROM for DLPC410 Controller................................................... 14 1.3.5 APPSFPGA Flash Configuration PROM ....................................................................... 15 1.3.6 DMD Connectors ................................................................................................ -

Classification of Computers

Chapter-2 Classification of Computers Computers can be classified many different ways -- by size, by function, or by processing capacity. Functionality wise 4 types a) Micro computer b) Mini Computer c) Mainframe Computer d) Super Computer Microcomputers Microcomputers are connected to networks of other computers. The price of a microcomputer varies from each other depending on the capacity and features of the computer. Microcomputers make up the vast majority of computers. Single user can interact with this computer at a time. It is a small and general purpose computer. Mini Computer Mini Computer is a small and general purpose computer. It is more expensive than a micro computer. It has more storage capacity and speed. It designed to simultaneously handle the needs of multiple users. Mainframe Computer Large computers are called Mainframes. Mainframe computers process data at very high rates of speed, measured in the millions of instructions per second. They are very expensive than micro computer and mini computer. Mainframes are designed for multiple users and process vast amounts of data quickly. Examples: - Banks, insurance companies, manufacturers, mail-order companies, and airlines are typical users. Super Computers The largest computers are Super Computers. They are the most powerful, the most expensive, and the fastest. They are capable of processing trillions of instructions per second. It uses governmental agencies, such as:- Chemical analysis in laboratory Space exploration National Defense Agency National Weather Service Bio-Medical research Design of many other machines Limitations of Computer Computer cannot take over all activities simply because they are less flexible than humans. It does not hold intelligence of its own. -

From Social Welfare to Social Control: Federal War in American Cities, 1968-1988

From Social Welfare to Social Control: Federal War in American Cities, 1968-1988 Elizabeth Kai Hinton Submitted in partial fulfillment of requirements for the degree of Doctor of Philosophy in the Graduate School of Arts and Sciences COLUMBIA UNIVERSITY 2013 © 2012 Elizabeth Kai Hinton All rights reserved ABSTRACT From Social Welfare to Social Control: Federal War in American Cities, 1968-1988 Elizabeth Hinton The first historical account of federal crime control policy, “From Social Welfare to Social Control” contextualizes the mass incarceration of marginalized Americans by illuminating the process that gave rise to the modern carceral state in the decades after the Civil Rights Movement. The dissertation examines the development of the national law enforcement program during its initial two decades, from the Omnibus Crime Control and Safe Streets Act of 1968, which established the block grant system and a massive federal investment into penal and juridical agencies, to the Omnibus Anti-Drug Abuse Act of 1988, which set sentencing guidelines that ensured historic incarceration rates. During this critical period, Presidential Administrations, State Departments, and Congress refocused the domestic agenda from social programs to crime and punishment. To challenge our understanding of the liberal welfare state and the rise of modern conservatism, “From Social Welfare to Social Control” emphasizes the bipartisan dimensions of punitive policy and situates crime control as the dominant federal response to the social and demographic transformations brought about by mass protest and the decline of domestic manufacturing. The federal government’s decision to manage the material consequences of rising unemployment, subpar school systems, and poverty in American cities as they manifested through crime reinforced violence within the communities national law enforcement legislation targeted with billions of dollars in grant funds from 1968 onwards.