Systems Architecture

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

1 Oral History Interview with Brian Randell January 7, 2021 Via Zoom

Oral History Interview with Brian Randell January 7, 2021 Via Zoom Conducted by William Aspray Charles Babbage Institute 1 Abstract Brian Randell tells about his upbringing and his work at English Electric, IBM, and Newcastle University. The primary topic of the interview is his work in the history of computing. He discusses his discovery of the Irish computer pioneer Percy Ludgate, the preparation of his edited volume The Origins of Digital Computers, various lectures he has given on the history of computing, his PhD supervision of Martin Campbell-Kelly, the Computer History Museum, his contribution to the second edition of A Computer Perspective, and his involvement in making public the World War 2 Bletchley Park Colossus code- breaking machines, among other topics. This interview is part of a series of interviews on the early history of the history of computing. Keywords: English Electric, IBM, Newcastle University, Bletchley Park, Martin Campbell-Kelly, Computer History Museum, Jim Horning, Gwen Bell, Gordon Bell, Enigma machine, Curta (calculating device), Charles and Ray Eames, I. Bernard Cohen, Charles Babbage, Percy Ludgate. 2 Aspray: This is an interview on the 7th of January 2021 with Brian Randell. The interviewer is William Aspray. We’re doing this interview via Zoom. Brian, could you briefly talk about when and where you were born, a little bit about your growing up and your interests during that time, all the way through your formal education? Randell: Ok. I was born in 1936 in Cardiff, Wales. Went to school, high school, there. In retrospect, one of the things I missed out then was learning or being taught Welsh. -

Technical Details of the Elliott 152 and 153

Appendix 1 Technical Details of the Elliott 152 and 153 Introduction The Elliott 152 computer was part of the Admiralty’s MRS5 (medium range system 5) naval gunnery project, described in Chap. 2. The Elliott 153 computer, also known as the D/F (direction-finding) computer, was built for GCHQ and the Admiralty as described in Chap. 3. The information in this appendix is intended to supplement the overall descriptions of the machines as given in Chaps. 2 and 3. A1.1 The Elliott 152 Work on the MRS5 contract at Borehamwood began in October 1946 and was essen- tially finished in 1950. Novel target-tracking radar was at the heart of the project, the radar being synchronized to the computer’s clock. In his enthusiasm for perfecting the radar technology, John Coales seems to have spent little time on what we would now call an overall systems design. When Harry Carpenter joined the staff of the Computing Division at Borehamwood on 1 January 1949, he recalls that nobody had yet defined the way in which the control program, running on the 152 computer, would interface with guns and radar. Furthermore, nobody yet appeared to be working on the computational algorithms necessary for three-dimensional trajectory predic- tion. As for the guns that the MRS5 system was intended to control, not even the basic ballistics parameters seemed to be known with any accuracy at Borehamwood [1, 2]. A1.1.1 Communication and Data-Rate The physical separation, between radar in the Borehamwood car park and digital computer in the laboratory, necessitated an interconnecting cable of about 150 m in length. -

History of Computer Science from Wikipedia, the Free Encyclopedia

History of computer science From Wikipedia, the free encyclopedia The history of computer science began long before the modern discipline of computer science that emerged in the 20th century, and hinted at in the centuries prior. The progression, from mechanical inventions and mathematical theories towards the modern concepts and machines, formed a major academic field and the basis of a massive worldwide industry.[1] Contents 1 Early history 1.1 Binary logic 1.2 Birth of computer 2 Emergence of a discipline 2.1 Charles Babbage and Ada Lovelace 2.2 Alan Turing and the Turing Machine 2.3 Shannon and information theory 2.4 Wiener and cybernetics 2.5 John von Neumann and the von Neumann architecture 3 See also 4 Notes 5 Sources 6 Further reading 7 External links Early history The earliest known as tool for use in computation was the abacus, developed in period 2700–2300 BCE in Sumer . The Sumerians' abacus consisted of a table of successive columns which delimited the successive orders of magnitude of their sexagesimal number system.[2] Its original style of usage was by lines drawn in sand with pebbles . Abaci of a more modern design are still used as calculation tools today.[3] The Antikythera mechanism is believed to be the earliest known mechanical analog computer.[4] It was designed to calculate astronomical positions. It was discovered in 1901 in the Antikythera wreck off the Greek island of Antikythera, between Kythera and Crete, and has been dated to c. 100 BCE. Technological artifacts of similar complexity did not reappear until the 14th century, when mechanical astronomical clocks appeared in Europe.[5] Mechanical analog computing devices appeared a thousand years later in the medieval Islamic world. -

Timeline of Computer History

Timeline of Computer History By Year By Category Search AI & Robotics (55) Computers (145)(145) Graphics & Games (48) Memory & Storage (61) Networking & The Popular Culture (50) Software & Languages (60) Bell Laboratories scientist 1937 George Stibitz uses relays for a Hewlett-Packard is founded demonstration adder 1939 Hewlett and Packard in their garage workshop “Model K” Adder David Packard and Bill Hewlett found their company in a Alto, California garage. Their first product, the HP 200A A Called the “Model K” Adder because he built it on his Oscillator, rapidly became a popular piece of test equipm “Kitchen” table, this simple demonstration circuit provides for engineers. Walt Disney Pictures ordered eight of the 2 proof of concept for applying Boolean logic to the design of model to test recording equipment and speaker systems computers, resulting in construction of the relay-based Model the 12 specially equipped theatres that showed the movie I Complex Calculator in 1939. That same year in Germany, “Fantasia” in 1940. engineer Konrad Zuse built his Z2 computer, also using telephone company relays. The Complex Number Calculat 1940 Konrad Zuse finishes the Z3 (CNC) is completed Computer 1941 The Zuse Z3 Computer The Z3, an early computer built by German engineer Konrad Zuse working in complete isolation from developments elsewhere, uses 2,300 relays, performs floating point binary arithmetic, and has a 22-bit word length. The Z3 was used for aerodynamic calculations but was destroyed in a bombing raid on Berlin in late 1943. Zuse later supervised a reconstruction of the Z3 in the 1960s, which is currently on Operator at Complex Number Calculator (CNC) display at the Deutsches Museum in Munich. -

TCM Report, Summer

Board of Directors Corporate Donors Contributing Members John William Poduska. Sr. Benefactor-$lO.ooo or more Pathway Design. Inc. Patron-$SOO or more Chairman and CEO AFIPS. Inc." PC Magazine Anonymous. Ray Duncan. Tom Eggers. Belmont Computer. Inc. American Exr.ress Foundation Peat. Marwick. Mitchell & Co. Alan E. Frisbie. Tom and Rosemarie American Te ephone & Telegraph Co." Pell. Rudman. Inc. Hall. Andrew Lavien. Nicholas and Gwen Bell. President Apollo Computer. Inc." Pencept. Inc. Nancy Petti nella. Paul R. Pierce. The Computer Museum Bank of America" Polese-Clancy. Inc. Jonathan Rotenberg. Oliver and Kitty Erich Bloch The Boston Globe" Price Waterhouse Selfridge. J. Michael Storie. Bob National Science Foundation ComputerLand" Project Software & Development. Inc. Whelan. Leo R. Yochim Control Data Corporation" Shawmut Corporation David Donaldson Data General Corporation" Standard Oil Corporation Sponsor-$250 Ropes and Gray Digital Equipment Corporation" Teradyne Hewlett-Packard Warner & Stackpole Isaac Auerbach. G. C . Beldon. Jr .. Sydney Fernbach Philip D. Brooke. Richard J. Clayton. Computer Consultant International Data Group" XRE Corporation International Business Machines. Inc." " Contributed to the Capital Campaign Richard Corben. Howard E. Cox. Jr .. C. Lester Hogan The MITRE Corporation" Lucien and Catherine Dimino. Philip H. Fairchild Camera and Instrument NEC Corporation" Darn. Dan L. Eisner. Bob O. Evans. Corporation Raytheon Company Branko Gerovac. Dr. Roberto Guatelli. Sanders Associates M. Ernest Huber. Lawrence J. Kilgallen. Arthur Humphreys The Travelers Companies Core Members Martin Kirkpatrick. Marian Kowalski. ICL Wang Laboratories. Inc." Raymond Kurzweil. Michael Levitt. Carl Theodore G. Johnson Harlan E. and Lois Anderson Machover. Julius Marcus. Joe W .. Charles and Constance Bachman Matthews. Tron McConnell. -

Alan Turingturing –– Computercomputer Designerdesigner

AlanAlan TuringTuring –– ComputerComputer DesignerDesigner Brian E. Carpenter with input from Robert W. Doran The University of Auckland May 2012 Turing, the theoretician ● Turing is widely regarded as a pure mathematician. After all, he was a B-star Wrangler (in the same year as Maurice Wilkes) ● “It is possible to invent a single machine which can be used to compute any computable sequence. If this machine U is supplied with the tape on the beginning of which is written the string of quintuples separated by semicolons of some computing machine M, then U will compute the same sequence as M.” (1937) ● So how was he able to write Proposals for development in the Mathematics Division of an Automatic Computing Engine (ACE) by the end of 1945? 2 Let’s read that carefully ● “It is possible to inventinvent a single machinemachine which can be used to compute any computable sequence. If this machinemachine U is supplied with the tapetape on the beginning of which is writtenwritten the string of quintuples separated by semicolons of some computing machinemachine M, then U will compute the same sequence as M.” ● The founding statement of computability theory was written in entirely physical terms. 3 What would it take? ● A tape on which you can write, read and erase symbols. ● Poulsen demonstrated magnetic wire recording in 1898. ● A way of storing symbols and performing simple logic. ● Eccles & Jordan patented the multivibrator trigger circuit (flip- flop) in 1919. ● Rossi invented the coincidence circuit (AND gate) in 1930. ● Building U in 1937 would have been only slightly more bizarre than building a differential analyser with Meccano. -

Alan Turing's Automatic Computing Engine

5 Turing and the computer B. Jack Copeland and Diane Proudfoot The Turing machine In his first major publication, ‘On computable numbers, with an application to the Entscheidungsproblem’ (1936), Turing introduced his abstract Turing machines.1 (Turing referred to these simply as ‘computing machines’— the American logician Alonzo Church dubbed them ‘Turing machines’.2) ‘On Computable Numbers’ pioneered the idea essential to the modern computer—the concept of controlling a computing machine’s operations by means of a program of coded instructions stored in the machine’s memory. This work had a profound influence on the development in the 1940s of the electronic stored-program digital computer—an influence often neglected or denied by historians of the computer. A Turing machine is an abstract conceptual model. It consists of a scanner and a limitless memory-tape. The tape is divided into squares, each of which may be blank or may bear a single symbol (‘0’or‘1’, for example, or some other symbol taken from a finite alphabet). The scanner moves back and forth through the memory, examining one square at a time (the ‘scanned square’). It reads the symbols on the tape and writes further symbols. The tape is both the memory and the vehicle for input and output. The tape may also contain a program of instructions. (Although the tape itself is limitless—Turing’s aim was to show that there are tasks that Turing machines cannot perform, even given unlimited working memory and unlimited time—any input inscribed on the tape must consist of a finite number of symbols.) A Turing machine has a small repertoire of basic operations: move left one square, move right one square, print, and change state. -

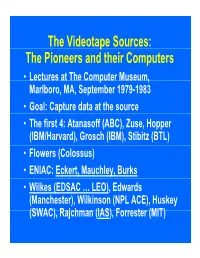

P the Pioneers and Their Computers

The Videotape Sources: The Pioneers and their Computers • Lectures at The Compp,uter Museum, Marlboro, MA, September 1979-1983 • Goal: Capture data at the source • The first 4: Atanasoff (ABC), Zuse, Hopper (IBM/Harvard), Grosch (IBM), Stibitz (BTL) • Flowers (Colossus) • ENIAC: Eckert, Mauchley, Burks • Wilkes (EDSAC … LEO), Edwards (Manchester), Wilkinson (NPL ACE), Huskey (SWAC), Rajchman (IAS), Forrester (MIT) What did it feel like then? • What were th e comput ers? • Why did their inventors build them? • What materials (technology) did they build from? • What were their speed and memory size specs? • How did they work? • How were they used or programmed? • What were they used for? • What did each contribute to future computing? • What were the by-products? and alumni/ae? The “classic” five boxes of a stored ppgrogram dig ital comp uter Memory M Central Input Output Control I O CC Central Arithmetic CA How was programming done before programming languages and O/Ss? • ENIAC was programmed by routing control pulse cables f ormi ng th e “ program count er” • Clippinger and von Neumann made “function codes” for the tables of ENIAC • Kilburn at Manchester ran the first 17 word program • Wilkes, Wheeler, and Gill wrote the first book on programmiidbBbbIiSiing, reprinted by Babbage Institute Series • Parallel versus Serial • Pre-programming languages and operating systems • Big idea: compatibility for program investment – EDSAC was transferred to Leo – The IAS Computers built at Universities Time Line of First Computers Year 1935 1940 1945 1950 1955 ••••• BTL ---------o o o o Zuse ----------------o Atanasoff ------------------o IBM ASCC,SSEC ------------o-----------o >CPC ENIAC ?--------------o EDVAC s------------------o UNIVAC I IAS --?s------------o Colossus -------?---?----o Manchester ?--------o ?>Ferranti EDSAC ?-----------o ?>Leo ACE ?--------------o ?>DEUCE Whirl wi nd SEAC & SWAC ENIAC Project Time Line & Descendants IBM 701, Philco S2000, ERA.. -

Media Technology and Society

MEDIA TECHNOLOGY AND SOCIETY Media Technology and Society offers a comprehensive account of the history of communications technologies, from the telegraph to the Internet. Winston argues that the development of new media, from the telephone to computers, satellite, camcorders and CD-ROM, is the product of a constant play-off between social necessity and suppression: the unwritten ‘law’ by which new technologies are introduced into society. Winston’s fascinating account challenges the concept of a ‘revolution’ in communications technology by highlighting the long histories of such developments. The fax was introduced in 1847. The idea of television was patented in 1884. Digitalisation was demonstrated in 1938. Even the concept of the ‘web’ dates back to 1945. Winston examines why some prototypes are abandoned, and why many ‘inventions’ are created simultaneously by innovators unaware of each other’s existence, and shows how new industries develop around these inventions, providing media products for a mass audience. Challenging the popular myth of a present-day ‘Information Revolution’, Media Technology and Society is essential reading for anyone interested in the social impact of technological change. Brian Winston is Head of the School of Communication, Design and Media at the University of Westminster. He has been Dean of the College of Communications at the Pennsylvania State University, Chair of Cinema Studies at New York University and Founding Research Director of the Glasgow University Media Group. His books include Claiming the Real (1995). As a television professional, he has worked on World in Action and has an Emmy for documentary script-writing. MEDIA TECHNOLOGY AND SOCIETY A HISTORY: FROM THE TELEGRAPH TO THE INTERNET BrianWinston London and New York First published 1998 by Routledge 11 New Fetter Lane, London EC4P 4EE Simultaneously published in the USA and Canada by Routledge 29 West 35th Street, New York, NY 10001 Routledge is an imprint of the Taylor & Francis Group This edition published in the Taylor & Francis e-Library, 2003. -

Alan Turing 1 Alan Turing

Alan Turing 1 Alan Turing Alan Turing Turing at the time of his election to Fellowship of the Royal Society. Born Alan Mathison Turing 23 June 1912 Maida Vale, London, England, United Kingdom Died 7 June 1954 (aged 41) Wilmslow, Cheshire, England, United Kingdom Residence United Kingdom Nationality British Fields Mathematics, Cryptanalysis, Computer science Institutions University of Cambridge Government Code and Cypher School National Physical Laboratory University of Manchester Alma mater King's College, Cambridge Princeton University Doctoral advisor Alonzo Church Doctoral students Robin Gandy Known for Halting problem Turing machine Cryptanalysis of the Enigma Automatic Computing Engine Turing Award Turing test Turing patterns Notable awards Officer of the Order of the British Empire Fellow of the Royal Society Alan Mathison Turing, OBE, FRS ( /ˈtjʊərɪŋ/ TEWR-ing; 23 June 1912 – 7 June 1954), was a British mathematician, logician, cryptanalyst, and computer scientist. He was highly influential in the development of computer science, giving a formalisation of the concepts of "algorithm" and "computation" with the Turing machine, which can be considered a model of a general purpose computer.[1][2][3] Turing is widely considered to be the father of computer science and artificial intelligence.[4] During World War II, Turing worked for the Government Code and Cypher School (GC&CS) at Bletchley Park, Britain's codebreaking centre. For a time he was head of Hut 8, the section responsible for German naval cryptanalysis. He devised a number of techniques for breaking German ciphers, including the method of the bombe, an electromechanical machine that could find settings for the Enigma machine. -

Alan Turing's Other Universal Machine

viewpoints VDOI:10.1145/2209249.2209277 Martin Campbell-Kelly Historical Reflections Alan Turing’s Other Universal Machine Reflections on the Turing ACE computer and its influence. LL COMPUTER SCIENTISTS know about the Univer- sal Turing Machine, the theoretical construct the British genius Alan Turing Adescribed in his famous 1936 paper on the Entscheidungsproblem (the halting problem). The Turing Machine is one of the foundation stones of theoreti- cal computer science. Much less well known is the practical stored program computer he proposed after the war in February 1946. The computer was called the ACE—Automatic Comput- ing Engine—a name intended to evoke the spirit of Charles Babbage, the pio- neer of computing machines in the previous century. Almost all post-war electronic com- puters were, and still are, based on the famous EDVAC Report written by John von Neumann in June 1945 on behalf The Pilot ACE, May 1950. Jim Wilkinson (center right) and Donald Davies (right). of the computer group at the Moore School of Electrical Engineering at the roles. Computers were in the air and of one, and over the next few months University of Pennsylvania. Von Neu- universities at Manchester, Cam- he evolved the design of the ACE. His mann was very familiar with Turing’s bridge, and elsewhere established report was formally presented to the 1936 Entscheidungsproblem paper. In electronic computer projects. Out- NPL’s executive committee in Febru- 1937, Turing was a research assistant side the academic sphere, in Lon- ary 1946. at the Institute for Advanced Study at don, the National Physical Laboratory Although the ACE drew heavily on Princeton University, where von Neu- (NPL—Britain’s equivalent of the Na- the EDVAC Report, it had many novel mann was a professor of mathematics. -

David Link There Must Be an Angel on the Beginnings of the Arithmetics Of

david link There Must Be an Angel On the Beginnings of the Arithmetics of Rays From August 1953 to May 1954 strange love-letters appeared on the notice board of Manchester University’s Computer Department:1 “darling sweetheart you are my avid fellow feeling. my affection curiously clings to your passionate wish. my liking yearns for your heart. you are my wistful sympathy: my tender liking. yours beautifully m.u.c.”2 The acronym “M.U.C.” stood for “Manchester University Computer”, the ear- liest electronic, programmable, and universal calculating machine; the fully functional prototype was completed in June 1948.3 One of the very first software developers, Christopher Strachey (1916–1975), had used the built-in random generator of the Ferranti Mark I, the first industrially produced computer of this kind, to generate texts that are intended to express and arouse emotions. The 1 T. William Olle, personal communication, 21 February 2006: “I do remember a copy of the Strachey love-letter being put on the notice board and that must have been after August 1953 and probably prior to May 1954 (the date of Alan Turing’s death).” 2 Christopher Strachey, The “thinking” machine. Encounter. Literature, Arts, Politics 13 (1954): 25–31, p. 26. 3 Frederic C. Williams and Tom Kilburn, Electronic digital computers. Nature 162 (1948): 487. By “computing” and “calculating” I mean here and in the following in general the processing of data. Var- ious machines are claimed to be the “first” computer, but all others lack one of the properties men- tioned. The “ABC”, developed by John V.