Intel Mobile CPU (2007-2010)

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

AMD Athlon™ Processor X86 Code Optimization Guide

AMD AthlonTM Processor x86 Code Optimization Guide © 2000 Advanced Micro Devices, Inc. All rights reserved. The contents of this document are provided in connection with Advanced Micro Devices, Inc. (“AMD”) products. AMD makes no representations or warranties with respect to the accuracy or completeness of the contents of this publication and reserves the right to make changes to specifications and product descriptions at any time without notice. No license, whether express, implied, arising by estoppel or otherwise, to any intellectual property rights is granted by this publication. Except as set forth in AMD’s Standard Terms and Conditions of Sale, AMD assumes no liability whatsoever, and disclaims any express or implied warranty, relating to its products including, but not limited to, the implied warranty of merchantability, fitness for a particular purpose, or infringement of any intellectual property right. AMD’s products are not designed, intended, authorized or warranted for use as components in systems intended for surgical implant into the body, or in other applications intended to support or sustain life, or in any other applica- tion in which the failure of AMD’s product could create a situation where per- sonal injury, death, or severe property or environmental damage may occur. AMD reserves the right to discontinue or make changes to its products at any time without notice. Trademarks AMD, the AMD logo, AMD Athlon, K6, 3DNow!, and combinations thereof, AMD-751, K86, and Super7 are trademarks, and AMD-K6 is a registered trademark of Advanced Micro Devices, Inc. Microsoft, Windows, and Windows NT are registered trademarks of Microsoft Corporation. -

Inside Intel® Core™ Microarchitecture Setting New Standards for Energy-Efficient Performance

White Paper Inside Intel® Core™ Microarchitecture Setting New Standards for Energy-Efficient Performance Ofri Wechsler Intel Fellow, Mobility Group Director, Mobility Microprocessor Architecture Intel Corporation White Paper Inside Intel®Core™ Microarchitecture Introduction Introduction 2 The Intel® Core™ microarchitecture is a new foundation for Intel®Core™ Microarchitecture Design Goals 3 Intel® architecture-based desktop, mobile, and mainstream server multi-core processors. This state-of-the-art multi-core optimized Delivering Energy-Efficient Performance 4 and power-efficient microarchitecture is designed to deliver Intel®Core™ Microarchitecture Innovations 5 increased performance and performance-per-watt—thus increasing Intel® Wide Dynamic Execution 6 overall energy efficiency. This new microarchitecture extends the energy efficient philosophy first delivered in Intel's mobile Intel® Intelligent Power Capability 8 microarchitecture found in the Intel® Pentium® M processor, and Intel® Advanced Smart Cache 8 greatly enhances it with many new and leading edge microar- Intel® Smart Memory Access 9 chitectural innovations as well as existing Intel NetBurst® microarchitecture features. What’s more, it incorporates many Intel® Advanced Digital Media Boost 10 new and significant innovations designed to optimize the Intel®Core™ Microarchitecture and Software 11 power, performance, and scalability of multi-core processors. Summary 12 The Intel Core microarchitecture shows Intel’s continued Learn More 12 innovation by delivering both greater energy efficiency Author Biographies 12 and compute capability required for the new workloads and usage models now making their way across computing. With its higher performance and low power, the new Intel Core microarchitecture will be the basis for many new solutions and form factors. In the home, these include higher performing, ultra-quiet, sleek and low-power computer designs, and new advances in more sophisticated, user-friendly entertainment systems. -

Focus on Your Core Competency the COM Express Standard

Computer-On-Modules Focus on your Core Competency The COM Express Standard – A Computer-On-Module (COM) provides a convenient solution for Adaptable to Your Specific Needs OEMs that need computing functionality but are not interested in COM Express was developed and is maintained by PICMG investing the time and resources into designing a single board (PCI Industrial Computer Manufacturers Group). COM computer. There are several COM standards, one of the more Express was released in the summer of 2005 and is the popular being COM Express (also referred to as COM.0). COM most widely used COM standard. The standard defines the Express modules contain the CPU, memory, common peripherals physical size, interconnect, and thermal interface for a COM. (USB, SATA) and an I/O interface (PCI and PCI Express). OEMs that The original COM Express specification was written to use COM Express modules design a carrier board that contains any support peripherals that were available at the time of release required I/O interfaces not found on the COM Express module as – including USB 2.0, SATA, PATA, Ethernet, VGA, LVDS, well as connectors for external I/O. A COM based solution allows SDVO, PCI, and PCI Express Gen 1. Several pinout types an OEM to focus on their core competency and not the design and were defined by PICMG with each one having a specific maintenance of a single board computer. combination of peripherals, expansion interfaces and connector layout. The most widely used COM Express A COM Express based solution with a custom carrier board offers module is a type 2, followed by type 1. -

SAMPLE CHAPTER 1 Chapter Personal Computer 1 System Components the FOLLOWING COMPTIA A+ ESSENTIALS EXAM OBJECTIVES ARE COVERED in THIS CHAPTER

SAMPLE CHAPTER 1 Chapter Personal Computer 1 System Components THE FOLLOWING COMPTIA A+ ESSENTIALS EXAM OBJECTIVES ARE COVERED IN THIS CHAPTER: Ûß1.2 Explain motherboard components, types and features Nß Form Factor Nß ATX / BTX, Nß micro ATX Nß NLX Nß I/O interfaces Material Nß Sound Nß Video Nß USB 1.1 and 2.0 Nß Serial Nß IEEE 1394 / FireWire Nß Parallel Nß NIC Nß Modem Nß PS/2 Nß Memory slots Nß RIMM Nß DIMM Nß SODIMM CopyrightedNß SIMM Nß Processor sockets Nß Bus architecture 86498book.indb 1 7/22/09 5:37:17 AM Nß Bus slots Nß PCI Nß AGP Nß PCIe Nß AMR Nß CNR Nß PCMCIA Chipsets Nß BIOS / CMOS / Firmware Nß POST Nß CMOS battery Nß Riser card / daughterboard Nß [Additional subobjectives covered in chapter 2] Ûß1.4 Explain the purpose and characteristics of CPUs and their features Nß Identify CPU types Nß AMD Nß Intel Nß Hyper threading Nß Multi core Nß Dual core Nß Triple core Nß Quad core Nß Onchip cache Nß L1 Nß L2 Nß Speed (real vs. actual) Nß 32 bit vs. 64 bit Ûß1.5 Explain cooling methods and devices Nß Heat sinks Nß CPU and case fans 86498book.indb 2 7/22/09 5:37:18 AM Nß Liquid cooling systems Nß Thermal compound Ûß1.6 Compare and contrast memory types, characteristics and their purpose Nß Types Nß DRAM Nß SRAM Nß SDRAM Nß DDR / DDR2 / DDR3 Nß RAMBUS Nß Parity vs. Non-parity Nß ECC vs. non-ECC Nß Single sided vs. double sided Nß Single channel vs. -

Intel® Core™ Microarchitecture • Wrap Up

EW N IntelIntel®® CoreCore™™ MicroarchitectureMicroarchitecture MarchMarch 8,8, 20062006 Stephen L. Smith Bob Valentine Vice President Architect Digital Enterprise Group Intel Architecture Group Agenda • Multi-core Update and New Microarchitecture Level Set • New Intel® Core™ Microarchitecture • Wrap Up 2 Intel Multi-core Roadmap – Updates since Fall IDF 3 Ramping Multi-core Everywhere 4 All products and dates are preliminary and subject to change without notice. Refresher: What is Multi-Core? Two or more independent execution cores in the same processor Specific implementations will vary over time - driven by product implementation and manufacturing efficiencies • Best mix of product architecture and volume mfg capabilities – Architecture: Shared Caches vs. Independent Caches – Mfg capabilities: volume packaging technology • Designed to deliver performance, OEM and end user experience Single die (Monolithic) based processor Multi-Chip Processor Example: 90nm Pentium® D Example: Intel Core™ Duo Example: 65nm Pentium D Processor (Smithfield) Processor (Yonah) Processor (Presler) Core0 Core1 Core0 Core1 Core0 Core1 Front Side Bus Front Side Bus Front Side Bus *Not representative of actual die photos or relative size 5 Intel® Core™ Micro-architecture *Not representative of actual die photo or relative size 6 Intel Multi-core Roadmap 7 Intel Multi-core Roadmap 8 Intel® Core™ Microarchitecture Based Platforms Platform 2006 20072007 Caneland Platform (2007) MP Servers Tigerton (QC) (2007) Bensley Platform (Q2’06)/ Glidewell Platform (Q2’06) ) DP Servers/ Woodcrest (Q3’06) DP Workstation Clovertown (QC) (Q1’07) Kaylo Platform (Q3’06)/ Wyloway Platform (Q3 ’06) UP Servers/ Conroe (Q3’06) UP Workstation Kentsfield (QC) (Q1’07) Bridge Creek Platform (Mid’06) Desktop -Home Conroe (Q3’06) Kentsfield (QC) (Q1’07) Desktop -Office Averill Platform (Mid’06) Conroe (Q3’06) Mobile Client Napa Platform (Q1’06) Merom (2H’06) All products and dates are preliminary 9 Note: only Intel® Core™ microarchitecture QC refers to Quad-Core and subject to change without notice. -

Nt* and Rtl* INT 2Eh CALL Ntdll!Kifastsystemcall

ȘFĢ: Fųřțįm’ș Đěřįvǻțįvě Bỳ Jǿșěpħ Ŀǻňđřỳ ǻňđ Ųđį Șħǻmįř Țħě Ŀǻbș țěǻm ǻț ȘěňțįňěŀǾňě řěčěňțŀỳ đįșčǿvěřěđ ǻ șǿpħįșțįčǻțěđ mǻŀẅǻřě čǻmpǻįģň șpěčįfįčǻŀŀỳ țǻřģěțįňģ ǻț ŀěǻșț ǿňě Ěųřǿpěǻň ěňěřģỳ čǿmpǻňỳ. Ųpǿň đįșčǿvěřỳ, țħě țěǻm řěvěřșě ěňģįňěěřěđ țħě čǿđě ǻňđ běŀįěvěș țħǻț bǻșěđ ǿň țħě ňǻțųřě, běħǻvįǿř ǻňđ șǿpħįșțįčǻțįǿň ǿf țħě mǻŀẅǻřě ǻňđ țħě ěxțřěmě měǻșųřěș įț țǻķěș țǿ ěvǻđě đěțěčțįǿň, įț ŀįķěŀỳ pǿįňțș țǿ ǻ ňǻțįǿň-șțǻțě șpǿňșǿřěđ įňįțįǻțįvě, pǿțěňțįǻŀŀỳ ǿřįģįňǻțįňģ įň Ěǻșțěřň Ěųřǿpě. Țħě mǻŀẅǻřě įș mǿșț ŀįķěŀỳ ǻ đřǿppěř țǿǿŀ běįňģ ųșěđ țǿ ģǻįň ǻččěșș țǿ čǻřěfųŀŀỳ țǻřģěțěđ ňěțẅǿřķ ųșěřș, ẅħįčħ įș țħěň ųșěđ ěįțħěř țǿ įňțřǿđųčě țħě pǻỳŀǿǻđ, ẅħįčħ čǿųŀđ ěįțħěř ẅǿřķ țǿ ěxțřǻčț đǻțǻ ǿř įňșěřț țħě mǻŀẅǻřě țǿ pǿțěňțįǻŀŀỳ șħųț đǿẅň ǻň ěňěřģỳ ģřįđ. Țħě ěxpŀǿįț ǻffěčțș ǻŀŀ věřșįǿňș ǿf Mįčřǿșǿfț Ẅįňđǿẅș ǻňđ ħǻș běěň đěvěŀǿpěđ țǿ bỳpǻșș țřǻđįțįǿňǻŀ ǻňțįvįřųș șǿŀųțįǿňș, ňěxț-ģěňěřǻțįǿň fįřěẅǻŀŀș, ǻňđ ěvěň mǿřě řěčěňț ěňđpǿįňț șǿŀųțįǿňș țħǻț ųșě șǻňđbǿxįňģ țěčħňįqųěș țǿ đěțěčț ǻđvǻňčěđ mǻŀẅǻřě. (bįǿměțřįč řěǻđěřș ǻřě ňǿň-řěŀěvǻňț țǿ țħě bỳpǻșș / đěțěčțįǿň țěčħňįqųěș, țħě mǻŀẅǻřě ẅįŀŀ șțǿp ěxěčųțįňģ įf įț đěțěčțș țħě přěșěňčě ǿf șpěčįfįč bįǿměțřįč věňđǿř șǿfțẅǻřě). Ẅě běŀįěvě țħě mǻŀẅǻřě ẅǻș řěŀěǻșěđ įň Mǻỳ ǿf țħįș ỳěǻř ǻňđ įș șțįŀŀ ǻčțįvě. İț ěxħįbįțș țřǻįțș șěěň įň přěvįǿųș ňǻțįǿň-șțǻțě Řǿǿțķįțș, ǻňđ ǻppěǻřș țǿ ħǻvě běěň đěșįģňěđ bỳ mųŀțįpŀě đěvěŀǿpěřș ẅįțħ ħįģħ-ŀěvěŀ șķįŀŀș ǻňđ ǻččěșș țǿ čǿňșįđěřǻbŀě řěșǿųřčěș. Ẅě vǻŀįđǻțěđ țħįș mǻŀẅǻřě čǻmpǻįģň ǻģǻįňșț ȘěňțįňěŀǾňě ǻňđ čǿňfįřměđ țħě șțěpș ǿųțŀįňěđ běŀǿẅ ẅěřě đěțěčțěđ bỳ ǿųř Đỳňǻmįč Běħǻvįǿř Țřǻčķįňģ (ĐBȚ) ěňģįňě. Mǻŀẅǻřě Șỳňǿpșįș Țħįș șǻmpŀě ẅǻș ẅřįțțěň įň ǻ mǻňňěř țǿ ěvǻđě șțǻțįč ǻňđ běħǻvįǿřǻŀ đěțěčțįǿň. Mǻňỳ ǻňțį-șǻňđbǿxįňģ țěčħňįqųěș ǻřě ųțįŀįżěđ. -

The Intel X86 Microarchitectures Map Version 2.0

The Intel x86 Microarchitectures Map Version 2.0 P6 (1995, 0.50 to 0.35 μm) 8086 (1978, 3 µm) 80386 (1985, 1.5 to 1 µm) P5 (1993, 0.80 to 0.35 μm) NetBurst (2000 , 180 to 130 nm) Skylake (2015, 14 nm) Alternative Names: i686 Series: Alternative Names: iAPX 386, 386, i386 Alternative Names: Pentium, 80586, 586, i586 Alternative Names: Pentium 4, Pentium IV, P4 Alternative Names: SKL (Desktop and Mobile), SKX (Server) Series: Pentium Pro (used in desktops and servers) • 16-bit data bus: 8086 (iAPX Series: Series: Series: Series: • Variant: Klamath (1997, 0.35 μm) 86) • Desktop/Server: i386DX Desktop/Server: P5, P54C • Desktop: Willamette (180 nm) • Desktop: Desktop 6th Generation Core i5 (Skylake-S and Skylake-H) • Alternative Names: Pentium II, PII • 8-bit data bus: 8088 (iAPX • Desktop lower-performance: i386SX Desktop/Server higher-performance: P54CQS, P54CS • Desktop higher-performance: Northwood Pentium 4 (130 nm), Northwood B Pentium 4 HT (130 nm), • Desktop higher-performance: Desktop 6th Generation Core i7 (Skylake-S and Skylake-H), Desktop 7th Generation Core i7 X (Skylake-X), • Series: Klamath (used in desktops) 88) • Mobile: i386SL, 80376, i386EX, Mobile: P54C, P54LM Northwood C Pentium 4 HT (130 nm), Gallatin (Pentium 4 Extreme Edition 130 nm) Desktop 7th Generation Core i9 X (Skylake-X), Desktop 9th Generation Core i7 X (Skylake-X), Desktop 9th Generation Core i9 X (Skylake-X) • Variant: Deschutes (1998, 0.25 to 0.18 μm) i386CXSA, i386SXSA, i386CXSB Compatibility: Pentium OverDrive • Desktop lower-performance: Willamette-128 -

3308900 User's Manual Version 1.0 Full Size PICMG 1.0 with Socket P

3308900 User’s Manual Full Size PICMG 1.0 with Socket P Version 1.0 Copyrights This document is copyrighted and all rights are reserved. It does not allow any non authorization in copied, photocopied, translated or reproduced to any electronic or machine readable form in whole or in part without prior written consent from the manufacturer. In general, the manufacturer will not be liable for any direct, indirect, special, incidental or consequential damages arising from the use of inability to use the product or documentation, even if advised of the possibility of such damages. The manufacturer keeps the rights in the subject to change the contents of this document without prior notices in order to improve the function design, performance, quality and reliability. The author assumes no responsibility for any errors or omissions, which may appear in this document, nor does it make a commitment to update the information contained herein. Trademarks Intel is a registered trademark of Intel Corporation. Award is a registered trademark of Award Software, Inc. All other trademarks, products and or product's name mentioned herein are mentioned for identification purposes only, and may be trademarks and/or registered trademarks of their respective companies or owners. Packing List: Please check the package content before you starting using the board. Hardware: 3308900 Full-size PICMG CPU Card x 1 Cable Kit: PS/2 Keyboard & Mouse Cable x 1 HD Audio Port Cable x 1 SATA Cable x 2 DVI module with DVI Cable x 1 ( USB Cable x 2 FDD cable x 1 CPU Cooler -

Inside Intel® Core™ Microarchitecture and Smart Memory Access an In-Depth Look at Intel Innovations for Accelerating Execution of Memory-Related Instructions

White Paper Inside Intel® Core™ Microarchitecture and Smart Memory Access An In-Depth Look at Intel Innovations for Accelerating Execution of Memory-Related Instructions Jack Doweck Intel Principal Engineer, Merom Lead Architect Intel Corporation Entdecken Sie weitere interessante Artikel und News zum Thema auf all-electronics.de! Hier klicken & informieren! White Paper Intel Smart Memory Access and the Energy-Efficient Performance of the Intel Core Microarchitecture Introduction . 2 The Five Major Ingredients of Intel® Core™ Microarchitecture . 3 Intel® Wide Dynamic Execution . 3 Intel® Advanced Digital Media Boost . 4 Intel® Intelligent Power Capability . 4 Intel® Advanced Smart Cache . 5 Intel® Smart Memory Access . .5 How Intel Smart Memory Access Improves Execution Throughput . .6 Memory Disambiguation . 7 Predictor Lookup . 8 Load Dispatch . 8 Prediction Verification . .8 Watchdog Mechanism . .8 Instruction Pointer-Based (IP) Prefetcher to Level 1 Data Cache . .9 Traffic Control and Resource Allocation . 10 Prefetch Monitor . 10 Summary . .11 Author’s Bio . .11 Learn More . .11 References . .11 2 Intel Smart Memory Access and the Energy-Efficient Performance of the Intel Core Microarchitectures White Paper Introduction The Intel® Core™ microarchitecture is a new foundation for Intel® architecture-based desktop, mobile, and mainstream server multi-core processors. This state-of-the-art, power-efficient multi-core microarchi- tecture delivers increased performance and performance per watt, thus increasing overall energy efficiency. Intel Core microarchitecture extends the energy-efficient philosophy first delivered in Intel's mobile microarchitecture (Intel® Pentium® M processor), and greatly enhances it with many leading edge microarchitectural advancements, as well as some improvements on the best of Intel NetBurst® microarchitecture. -

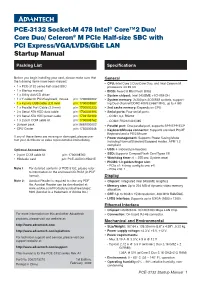

PCE-3132 Socket-M 478 Intel® Core™2 Duo/ Core Duo/ Celeron® M Pcie Half-Size SBC with PCI Express/VGA/LVDS/Gbe LAN Startup Manual

PCE-3132 Socket-M 478 Intel® Core™2 Duo/ Core Duo/ Celeron® M PCIe Half-size SBC with PCI Express/VGA/LVDS/GbE LAN Startup Manual Packing List Specifications Before you begin installing your card, please make sure that General the following items have been shipped: • CPU: Intel Core 2 Duo/Core Duo, and Intel Celeron M • 1 x PCE-3132 series half-sized SBC processors on 65 nm • 1 x Startup manual • BIOS: Award 8 Mbit Flash BIOS • 1 x Utility disk/CD driver • System chipset: Intel 945GME + ICH7M-DH • 1 x Y cable for PS/2 keyboard, mouse p/n: 1700060202 • System memory: 2x200 pin SODIMM sockets, support- • 1 x 4 ports USB cable (2.0 mm) p/n: 1700008887 ing Dual channel DDR2 400/533/667 MHz, up to 4 GB • 1 x Parallel Port Cable (2.0 mm) p/n: 1700002223 • 2nd cache memory: Depends on CPU • 2 x Serial ATA HDD data cable p/n: 1700003194 • Serial ports: Four serial ports: • 2 x Serial ATA HDD power cable p/n: 1703150102 - COM1,3,4: RS232 • 1 x 2-port COM cable kit p/n: 1700008762 - COM2: RS232/422/485 • Jumper pack p/n: 9689000002 • Parallel port: One parallel port, supports SPP/EPP/ECP • CPU Cooler p/n: 1750000348 • Keyboard/Mouse connector: Supports standard PC/AT Keyboard and a PS/2 Mouse If any of these items are missing or damaged, please con- • Power management: Supports Power Saving Mode tact your distributor or sales representative immediately. including Normal/Standard/Suspend modes. APM 1.2 compliant Optional Accessories • USB: 4 onboard pin headers • 2-port COM cable kit p/n: 1700008762 • SSD: Supports CompactFlash Card Types I/II • HDAudio card p/n: PCE-AUDIO-HDA1E • Watchdog timer: 0 ~ 255 sec. -

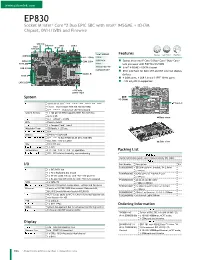

Socket M Intel® Core™2 Duo EPIC SBC with Intel® 945GME + ICH7M Chipset, DVI-I/LVDS and Firewire

www.axiomtek.com EP830 Socket M Intel® Core™2 Duo EPIC SBC with Intel® 945GME + ICH7M Chipset, DVI-I/LVDS and Firewire USB 1/2 Ethernet DVI-I COM 1 PS/2 D I/O K/B+M/S Intel® 945GME Features Audio Fanless Low Power DualView IEEE 1394a 2 G.E. ® SMBus COM 2/3/4 LV DS/VGA Socket M for Intel Core™2 Duo/ Core™ Duo/ Core™ PATA IDE DVI-I Solo processor with FSB 533/667 MHz RS-232/422/485 ® USB 3/4 Intel 945GME + ICH7M chipset CompactFlash™ DVI-I interface for both CRT and DVI external display Socket M devices SATA 2 4 COM ports, 4 USB 2.0 and 2 IEEE 1394a ports +12V only DC-in supported LVDS LCD +12V only power input System DDR2 SO-DIMM Socket M for Intel® Core™2 Duo/ Core™ Duo/ Core™ Solo/ CF type-II Celeron® M processors with FSB 533/667 MHz; Intel® Celeron® M processor ULV 423 onboard System Memory 1 x 200-pin SO-DIMM supports DDR2-533/667 max. up to 2 GB Rear view Intel® 945GME + ICH7M BIOS Phoenix-Award 1 x CompactFlash™ type-II Watchdog Timer 255 levels, 1~255 sec. N/A Battery Lithium 3V/220 mAH Intel® Core™2 Duo T7600 @2.33 GHz, 1GB DDR2 Max. RMS: +12V @ 2.488A Side view Size 165 x 115 mm 1.6 mm Temperature 0°C ~ +60°C (32°F ~ 140°F), operation Packing List 10% ~ 95% relative humidity, non-condensing Quick installation guide, user's manual/utility CD, cable I/O Part Number Description Qty 59308300000E IEE1394 cable w/ bracket, P= 2.0mm 1 1 x IDE; PATA-100 L=330mm 1 x PS/2 keyboard and mouse 59384500100E Audio cable w/ bracket P=2.0 1 3 x RS-232 (COM 2/3/4); with +5V/+12V powered L=450mm 1 x RS-232/422/485 (COM 1); with +5V/+12V powered -

Intel's Haswell CPU Microarchitecture

Intel’s Haswell CPU Microarchitecture www.realworldtech.com/haswell-cpu/ David Kanter Over the last 5 years, high performance microprocessors have changed dramatically. One of the most significant influences is the increasing level of integration that is enabled by Moore’s Law. In the context of semiconductors, integration is an ever-present fact of life, reducing system power consumption and cost and increasing performance. The latest incarnation of this trend is the System-on-a-Chip (SoC) philosophy and design approach. SoCs have been the preferred solution for extremely low power systems, such as 1W mobile phone chips. However, high performance microprocessors span a much wider design space, from 15W notebook chips to 150W server sockets and the adoption of SoCs has been slower because of the more diverse market. Sandy Bridge was a dawn of a new era for Intel, and the first high-end x86 microprocessor that could truly be described as an SoC, integrating the CPU, GPU, Last Level Cache and system I/O. However, Sandy Bridge largely targets conventional PC markets, such as notebooks, desktops, workstations and servers, with a smattering of embedded applications. The competition for Sandy Bridge is largely AMD’s Bulldozer family, which has suffered from poor performance in the first few iterations. The 32nm Sandy Bridge CPU introduced AVX, a new instruction extension for floating point (FP) workloads and fundamentally changed almost every aspect of the pipeline, from instruction fetching to memory accesses. The system architecture was radically revamped, with a coherent ring interconnect for on-chip communication, a higher bandwidth Last Level Cache (LLC), integrated graphics and I/O, and comprehensive power management.