Microprocessor Design Verification

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

System Design for a Computational-RAM Logic-In-Memory Parailel-Processing Machine

System Design for a Computational-RAM Logic-In-Memory ParaIlel-Processing Machine Peter M. Nyasulu, B .Sc., M.Eng. A thesis submitted to the Faculty of Graduate Studies and Research in partial fulfillment of the requirements for the degree of Doctor of Philosophy Ottaw a-Carleton Ins titute for Eleceical and Computer Engineering, Department of Electronics, Faculty of Engineering, Carleton University, Ottawa, Ontario, Canada May, 1999 O Peter M. Nyasulu, 1999 National Library Biôiiothkque nationale du Canada Acquisitions and Acquisitions et Bibliographie Services services bibliographiques 39S Weiiington Street 395. nie WeUingtm OnawaON KlAW Ottawa ON K1A ON4 Canada Canada The author has granted a non- L'auteur a accordé une licence non exclusive licence allowing the exclusive permettant à la National Library of Canada to Bibliothèque nationale du Canada de reproduce, ban, distribute or seU reproduire, prêter, distribuer ou copies of this thesis in microform, vendre des copies de cette thèse sous paper or electronic formats. la forme de microficbe/nlm, de reproduction sur papier ou sur format électronique. The author retains ownership of the L'auteur conserve la propriété du copyright in this thesis. Neither the droit d'auteur qui protège cette thèse. thesis nor substantial extracts fkom it Ni la thèse ni des extraits substantiels may be printed or otherwise de celle-ci ne doivent être imprimés reproduced without the author's ou autrement reproduits sans son permission. autorisation. Abstract Integrating several 1-bit processing elements at the sense amplifiers of a standard RAM improves the performance of massively-paralle1 applications because of the inherent parallelism and high data bandwidth inside the memory chip. -

Introduction to ASIC Design

’14EC770 : ASIC DESIGN’ An Introduction Application - Specific Integrated Circuit Dr.K.Kalyani AP, ECE, TCE. 1 VLSI COMPANIES IN INDIA • Motorola India – IC design center • Texas Instruments – IC design center in Bangalore • VLSI India – ASIC design and FPGA services • VLSI Software – Design of electronic design automation tools • Microchip Technology – Offers VLSI CMOS semiconductor components for embedded systems • Delsoft – Electronic design automation, digital video technology and VLSI design services • Horizon Semiconductors – ASIC, VLSI and IC design training • Bit Mapper – Design, development & training • Calorex Institute of Technology – Courses in VLSI chip design, DSP and Verilog HDL • ControlNet India – VLSI design, network monitoring products and services • E Infochips – ASIC chip design, embedded systems and software development • EDAIndia – Resource on VLSI design centres and tutorials • Cypress Semiconductor – US semiconductor major Cypress has set up a VLSI development center in Bangalore • VDAT 2000 – Info on VLSI design and test workshops 2 VLSI COMPANIES IN INDIA • Sandeepani – VLSI design training courses • Sanyo LSI Technology – Semiconductor design centre of Sanyo Electronics • Semiconductor Complex – Manufacturer of microelectronics equipment like VLSIs & VLSI based systems & sub systems • Sequence Design – Provider of electronic design automation tools • Trident Techlabs – Power systems analysis software and electrical machine design services • VEDA IIT – Offers courses & training in VLSI design & development • Zensonet Technologies – VLSI IC design firm eg3.com – Useful links for the design engineer • Analog Devices India Product Development Center – Designs DSPs in Bangalore • CG-CoreEl Programmable Solutions – Design services in telecommunications, networking and DSP 3 Physical Design, CAD Tools. • SiCore Systems Pvt. Ltd. 161, Greams Road, ... • Silicon Automation Systems (India) Pvt. Ltd. ( SASI) ... • Tata Elxsi Ltd. -

A System-Level Synthetic Circuit Generator for FPGA Architectural Analysis

A System-Level Synthetic Circuit Generator for FPGA Architectural Analysis by Cindy Mark B.A.Sc., Queen’s University, 2006 A THESIS SUBMITTED IN PARTIAL FULFILMENT OF THE REQUIREMENTS FOR THE DEGREE OF Master of Applied Science in The Faculty of Graduate Studies (Electrical and Computer Engineering) The University Of British Columbia (Vancouver) November, 2008 c Cindy Mark 2008 Abstract Architectural research for Field-Programmable Gate Arrays (FPGAs) tends to use an experimental approach. The benchmark circuits are used not only to compare different architectures, but also to ensure that the FPGA is sufficiently flexible to implement the desired variety of circuits. The most common benchmark circuits used for architectural research are circuits from the Microelectronics Center of North Carolina (MCNC). These circuits are small; they occupy less than 3% [5] of the largest available commercial FPGA. Moreover, these circuits are more representative of the glue logic circuits that were targets of early devices. This contrasts with the trend towards implementing Systems on Chip (SoCs) on FPGAs where several functional modules are integrated into a single circuit which is mapped onto one device. In this thesis, we develop a synthetic system-level circuit generator that connects pre- existing circuits in a realistic manner to build large netlists that share the characteristics of real SoC circuits. This generator is based on a survey of contemporary circuit designs from industrial and academic sources. We demonstrate that these system-level circuits scale well and that their post-routing characteristics match the results of large pre-existing benchmarks better than the results of circuits from previous synthetic generators. -

Coverstory by Robert Cravotta, Technical Editor

coverstory By Robert Cravotta, Technical Editor u WELCOME to the 31st annual EDN Microprocessor/Microcontroller Di- rectory. The number of companies and devices the directory lists continues to grow and change. The size of this year’s table of devices has grown more than NEW PROCESSOR OFFERINGS 25% from last year’s. Also, despite the fact that a number of companies have disappeared from the list, the number of companies participating in this year’s CONTINUE TO INCLUDE directory has still grown by 10%. So what? Should this growth and change in the companies and devices the directory lists mean anything to you? TARGETED, INTEGRATED One thing to note is that this year’s directory has experienced more compa- ny and product-line changes than the previous few years. One significant type PERIPHERAL SETS THAT SPAN of change is that more companies are publicly offering software-programma- ble processors. To clarify this fact, not every company that sells processor prod- ALL ARCHITECTURE SIZES. ucts decides to participate in the directory. One reason for not participating is that the companies are selling their processors only to specific customers and are not yet publicly offering those products. Some of the new companies par- ticipating in this year’s directory have recently begun making their processors available to the engineering public. Another type of change occurs when a company acquires another company or another company’s product line. Some of the acquired product lines are no longer available in their current form, such as the MediaQ processors that Nvidia acquired or the Triscend products that Arm acquired. -

Welcome to CSE467! Highlights

Welcome to CSE467! Highlights: Course Staff: Bruce Hemingway and Charles Giefer We'll be reading hand-outs and papers from various sources. Course web:http://www.cs.washington.edu/467/ The course work will be built around an embedded-core processor in an FPGA. My office: CSE 464 Allen Center, 206 543-6274 Tools are Active-HDL from Aldec, Synplify, and Xilinx ISE. Today: Course overview Languages are verilog and C. What is computer engineering? Applications in the FPGA will include some audio. What we will cover in this class What is “design”, and how do we do it? You may do this week’s lab at your own time. Basis for FPGAs The project- audio string model CSE467 1 CSE467 2 What is computer engineering? What we will cover in CSE467 CE is not PC design Basic digital design (much of it review) It includes PC design Combinational logic Truth tables & logic gates CE is not necessarily digital design Logic minimization Analog computers Special functions (muxes, decoders, ROMs, etc.) Real-world (analog) interfaces Sequential logic CE is about designing information-processing systems Flip-flops and registers Computers Clocking Networks and networking HW Synchronization and timing State machines Automation/controllers (smart appliances, etc.) Counters Medical/test equipment (CT scanners, etc.) State minimization and encoding Much, much more Moore vs Mealy CSE467 3 CSE467 4 What we will cover (con’t) CSE467 is about design Advanced topics Design is an art Field-programmable gate arrays (FPGAs) You learn -

Object-Oriented Development for Reconfigurable Architectures

Object-Oriented Development for Reconfigurable Architectures Von der Fakultät für Mathematik und Informatik der Technischen Universität Bergakademie Freiberg genehmigte DISSERTATION zur Erlangung des akademischen Grades Doktor Ingenieur Dr.-Ing., vorgelegt von Dipl.-Inf. (FH) Dominik Fröhlich geboren am 19. Februar 1974 Gutachter: Prof. Dr.-Ing. habil. Bernd Steinbach (Freiberg) Prof. Dr.-Ing. Thomas Beierlein (Mittweida) PD Dr.-Ing. habil. Michael Ryba (Osnabrück) Tag der Verleihung: 20. Juni 2007 To my parents. ABSTRACT Reconfigurable hardware architectures have been available now for several years. Yet the application devel- opment for such architectures is still a challenging and error-prone task, since the methods, languages, and tools being used for development are inappropriate to handle the complexity of the problem. This hampers the widespread utilization, despite of the numerous advantages offered by this type of architecture in terms of computational power, flexibility, and cost. This thesis introduces a novel approach that tackles the complexity challenge by raising the level of ab- straction to system-level and increasing the degree of automation. The approach is centered around the paradigms of object-orientation, platforms, and modeling. An application and all platforms being used for its design, implementation, and deployment are modeled with objects using UML and an action language. The application model is then transformed into an implementation, whereby the transformation is steered by the platform models. In this thesis solutions for the relevant problems behind this approach are discussed. It is shown how UML can be used for complete and precise modeling of applications and platforms. Application development is done at the system-level using a set of well-defined, orthogonal platform models. -

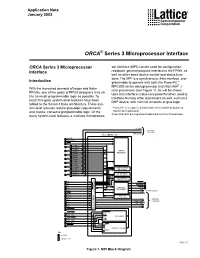

FPGA: ORCA Series 3 Microprocessor Interface

Application Note January 2002 ORCA® Series 3 Microprocessor Interface ORCA Series 3 Microprocessor sor interface (MPI) can be used for configuration, Interface readback, general-purpose interface to the FPGA, as well as other basic device control and status func- tions. The MPI is a synchronous, 8-bit interface, pro- Introduction grammable to operate with both the PowerPC * MPC800 series microprocessor and Intel i960† J With the increased demand of larger and faster core processors (see Figure 1). As will be shown FPGAs, one of the goals of FPGA designers is to uti- later, this interface is also very powerful when used to lize as much programmable logic as possible. To interface to many other processors as well, such as a reach this goal, system-level features have been DSP device, with minimal amounts of glue logic. added to the Series 3 base architecture. These sys- tem-level features reduce glue-logic requirements * PowerPC is a registered trademark of International Business and, hence, conserve programmable logic. Of the Machines Corporation. †Intel and i960 are registered trademarks of Intel Corporation. many system-level features, a multiuse microproces- D[7:0]IN TO FPGA ROUTING D[7:0]OUT ORCA SERIES 3 MPI DONE RD_DATA INIT D7 D7IN D7OUT D6 D6IN D6OUT STATUS REGISTER D5 D5IN D5OUT D4 D4IN D4OUT D3IN D3 D3OUT D2IN D2 D2OUT SCRATCHPAD D1IN D1 REGISTER D1OUT D0IN D0 READBACK D0OUT DATA REGISTER READBACK ADDR REGISTER A4 RESET A3 ONLY RD_CFG A2 PRGM A1 CONTROL REGISTERS GSR A0 TO GSR BLOCK POWERPC CS0 IRQ CS1 PART ID CCLK REGISTERS M3 USER_START TO FPGA ROUTING M2 USER_END M1 WR_CTRL M0 A[3:0] MPI_IRQ DECODE/CONTROL MPI_ACK RDYRCV CLK MPI_CLK ADS i960 LOGIC MPI_STRB ALE MPI_ALE W/R MPI_RW RD/WR MPI_B1 BT TS POWERPC LOGIC CLKOUT KEY: TA DEVICE I/O BUFFER 5-8511(F) Figure 1. -

DESIGN and DEVELOPMENT of a SOFT RECONFIGURABLE POWER ELECTRONIC CONTROL PROCESSOR KEVIN S, ER&DCI, CDAC, Trivandrum, [email protected]

NOVATEUR PUBLICATIONS INTERNATIONAL JOURNAL OF INNOVATIONS IN ENGINEERING RESEARCH AND TECHNOLOGY [IJIERT] ISSN: 2394-3696 VOLUME 5, ISSUE 6, June -2018 DESIGN AND DEVELOPMENT OF A SOFT RECONFIGURABLE POWER ELECTRONIC CONTROL PROCESSOR KEVIN S, ER&DCI, CDAC, Trivandrum, [email protected] AJEESH A, Senior Engineer, Power Electronics Group, CDAC, Trivandrum, [email protected] DIVYA D.S, Project Engineer, ER&DCI, CDAC, Trivandrum, [email protected] ABSTRACT This paper proposes to build a soft, platform independent, reconfigurable power electronic control processor in HDL. Currently power electronic control processors are designed with digital signal processors/microcontrollers with limited re-configurability and input-output capabilities, also DSP/microcontrollers suffer processor obsolescence risk. This can be reduced with the use of a reconfigurable control processor design in HDL and implemented on FPGA. Currently FPGA are used along with DSP for glue logic purpose and input-output expansion. So it is economical to use a single FPGA along with a soft core CPU and control modules as hardware accelerators. Some of the soft cores available are licensed and are targeted to a particular FPGA, so a 32 bit soft, reconfigurable power electronic control processor is developed from scratch. I. INTRODUCTION In this paper development of a soft, reconfigurable power electronic control processor is discussed. The conventionally used soft cores in power electronics like NIOS II are highly efficient but they take 8-9 cycles for memory read or write instructions. So to reduce this memory read and write cycles, the need for a soft reconfigurable processor arises. This newly developed soft core is also a FPGA independent one, so that it can be implemented on any available FPGA. -

Logic Families

Logic Families PDF generated using the open source mwlib toolkit. See http://code.pediapress.com/ for more information. PDF generated at: Mon, 11 Aug 2014 22:42:35 UTC Contents Articles Logic family 1 Resistor–transistor logic 7 Diode–transistor logic 10 Emitter-coupled logic 11 Gunning transceiver logic 16 Transistor–transistor logic 16 PMOS logic 23 NMOS logic 24 CMOS 25 BiCMOS 33 Integrated injection logic 34 7400 series 35 List of 7400 series integrated circuits 41 4000 series 62 List of 4000 series integrated circuits 69 References Article Sources and Contributors 75 Image Sources, Licenses and Contributors 76 Article Licenses License 77 Logic family 1 Logic family In computer engineering, a logic family may refer to one of two related concepts. A logic family of monolithic digital integrated circuit devices is a group of electronic logic gates constructed using one of several different designs, usually with compatible logic levels and power supply characteristics within a family. Many logic families were produced as individual components, each containing one or a few related basic logical functions, which could be used as "building-blocks" to create systems or as so-called "glue" to interconnect more complex integrated circuits. A "logic family" may also refer to a set of techniques used to implement logic within VLSI integrated circuits such as central processors, memories, or other complex functions. Some such logic families use static techniques to minimize design complexity. Other such logic families, such as domino logic, use clocked dynamic techniques to minimize size, power consumption, and delay. Before the widespread use of integrated circuits, various solid-state and vacuum-tube logic systems were used but these were never as standardized and interoperable as the integrated-circuit devices. -

Graphics Controllers & Development Tools GRAPHICS SOLUTIONS PRODUCT OVERVIEW GRAPHICS SOLUTIONS

PRODUCT OVERVIEW GRAPHICS SOLUTIONS Graphics Controllers & Development Tools GRAPHICS SOLUTIONS PRODUCT OVERVIEW GRAPHICS SOLUTIONS Copyright © 2008 Fujitsu Limited Tokyo, Japan and Fujitsu Microelectronics Europe This brochure contains references to various Fujitsu Graphics Controller products GmbH. All Rights Reserved. under their original development code names. Fujitsu does not lay any claim to the unique future use of these code names. The information contained in this document has been carefully checked and is believed to be entirely reliable. However Fujitsu and its subsidiaries assume no Designed and produced in the UK. Printed on environmentally friendly paper. responsibility for inaccuracies. The information contained in this document does not convey any licence under the copyrights, patent rights or trademarks claimed and owned by Fujitsu. Fujitsu Limited and its subsidiaries reserve the right to change products or ARM is a registered trademark of ARM Limited in UK, USA and Taiwan. specifications without notice. ARM is a trademark of ARM Limited in Japan and Korea. ARM Powered logo is a registered trademark of ARM Limited in Japan, UK, USA, and Taiwan. No part of this publication may be copied or reproduced in any form or by any means ARM Powered logo is a trademark of ARM Limited in Korea. or transferred to any third party without the prior consent of Fujitsu. ARM926EJ-S and ETM9 are trademarks of ARM Limited. CONTENTS Introduction to Graphics Controllers 2 Introduction to Business Unit Graphics Solutions 3 MB86290A ‘Cremson’ -

Application Report How to Migrate Custom Logic from an FPGA/CPLD to C2000™ Microcontrollers

www.ti.com Table of Contents Application Report How to Migrate Custom Logic From an FPGA/CPLD to C2000™ Microcontrollers Peter Galicki ABSTRACT The Configurable Logic Block (CLB) reduces total system cost and enhances functionality by absorbing external logic into C2000™ microcontrollers. CLB uses function calls and a GUI-based programming tool called SysConfig to absorb external logic into the microcontroller without having to learn Hardware Description Language like VHDL or Verilog. This Report shows programmers, hardware engineers and system designers how to translate FPGA- or CPLD-based custom logic (that has been originally defined in HDL) to a CLB form that can be programmed into C2000 MCUs. Table of Contents Trademarks.................................................................................................................................................................................2 1 Introduction.............................................................................................................................................................................3 2 CLB Description From the Hardware Perspective...............................................................................................................3 2.1 How Does the CLB Work................................................................................................................................................... 3 2.2 System-Level View of CLB.................................................................................................................................................5 -

Ep 0565914 A1

Europaisches Patentamt European Patent Office © Publication number: 0 565 914 A1 Office europeen des brevets EUROPEAN PATENT APPLICATION © Application number: 93104769.0 int ci 5 G06F 1/32 @ Date of filing: 23.03.93 © Priority: 15.04.92 US 870124 Inventor: Lee, Nathan Junsup 19 Scher Drive © Date of publication of application: New York City, New York 10956(US) 20.10.93 Bulletin 93/42 Inventor: Leontiades, Kyriakos 353 N.W. 22 Street 0 Designated Contracting States: Boca Raton, Florida 33431 (US) DE FR GB Inventor: Novak, Frank Peter 82 Oak Avenue © Applicant: International Business Machines Park Ridge, New Jersey 07656(US) Corporation Inventor: Sharma, Vikram Old Orchard Road 32 Hillview Drive Armonk, N.Y. 10504(US) Pleasantville, New York 10570(US) @ Inventor: Kannan, Krishnamurthi 2715 Evergreen Street © Representative: Monig, Anton, Dipl.-lng. Yorktown Heights, New York 10598(US) IBM Deutschland Informationssysteme Inventor: Jones, Christopher Dane GmbH, 1356 Dorchester Drive Patentwesen und Urheberrecht Georgetown, Kentucky 40324(US) D-70548 Stuttgart (DE) (sf) A system for distributed power management in portable computers. © The present invention provides a system and function of the conditions sensed by the sensing method for managing power in a portable, pen- means. based notebook computer. The system and method provides a means for minimizing power consumption by collecting and interpreting power related data at various processing elements while hiding many of the details from the end-user. The present invention is a system and method for monitoring, collecting and acting upon power-related data in a portable computer to maximize the amount of time the porta- ble computer can be used between battery re-charg- ing with minimal user intervention.