AN1597 Longwave Radio Data Decoding Using an HC11 and an MC3371

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Overview of Sensors for Applications

OVERVIEW OF SENSORS FOR APPLICATIONS Deepak Putrevu Head, MTDD/AMHTDG EM SPECTRUM Visible 0.4-0.7μm Near infrared (NIR) 0.7-1.5μm Optical Infrared Shortwave infrared (SWIR) 1.5-3.0μm Mid-wave infrared (MWIR) 3.0-8.0μm (OIR) Region Longwave IR(LWIR)/Thermal IR(TIR) 8.0-15μm Far infrared (FIR) Beyond15μm Gamma Rays X Rays UV Visible NIR SWIR Thermal IR Microwave P-band: ~0.25 – 1 GHz Microwave Region L-band: 1 -2 GHz S-band: 2-4 GHz •Sensors are 24x365 C-band: 4-8 GHz •Signal data characteristics X-band: 8-12 GHz unique to the microwave region of the EM spectrum Ku-band: 12-18 GHz K-band: 18-26 GHz •Response is primarily governed by geometric Ka-band: 26-40 GHz structures and hence V-band: 40 - 75 GHz complementary to optical W-band: 75-110 GHz imaging mm-wave: 110 – 300GHz Basic Interactions between Electromagnetic Energy and the Earth’s Surface Incident Power reflected, ρP Reflectivity: The fractional part of the radiation, P incident radiation that is reflected by the surface. Power absorbed, αP Absorptivity: the fractional part of the = Power emitted, εP incident radiation that is absorbed by the surface. Power transmitted, τP Emissivity: The ratio of the observed flux emitted by a body or surface to that of a P= Pr + Pt + Pa blackbody under the same condition. 푃 푃 푃 푟 + 푡 + 푎 = 1 푃 푃 푃 Transmissivity: The fractional part of the ρ + τ + α =1 radiation transmitted through the medium. At thermal equilibrium, absorption and emission are the same. -

Digital Audio Broadcasting : Principles and Applications of Digital Radio

Digital Audio Broadcasting Principles and Applications of Digital Radio Second Edition Edited by WOLFGANG HOEG Berlin, Germany and THOMAS LAUTERBACH University of Applied Sciences, Nuernberg, Germany Digital Audio Broadcasting Digital Audio Broadcasting Principles and Applications of Digital Radio Second Edition Edited by WOLFGANG HOEG Berlin, Germany and THOMAS LAUTERBACH University of Applied Sciences, Nuernberg, Germany Copyright ß 2003 John Wiley & Sons Ltd, The Atrium, Southern Gate, Chichester, West Sussex PO19 8SQ, England Telephone (þ44) 1243 779777 Email (for orders and customer service enquiries): [email protected] Visit our Home Page on www.wileyeurope.com or www.wiley.com All Rights Reserved. No part of this publication may be reproduced, stored in a retrieval system or transmitted in any form or by any means, electronic, mechanical, photocopying, recording, scanning or otherwise, except under the terms of the Copyright, Designs and Patents Act 1988 or under the terms of a licence issued by the Copyright Licensing Agency Ltd, 90 Tottenham Court Road, London W1T 4LP, UK, without the permission in writing of the Publisher. Requests to the Publisher should be addressed to the Permissions Department, John Wiley & Sons Ltd, The Atrium, Southern Gate, Chichester, West Sussex PO19 8SQ, England, or emailed to [email protected], or faxed to (þ44) 1243 770571. This publication is designed to provide accurate and authoritative information in regard to the subject matter covered. It is sold on the understanding that the Publisher is not engaged in rendering professional services. If professional advice or other expert assistance is required, the services of a competent professional should be sought. -

History of Radio Broadcasting in Montana

University of Montana ScholarWorks at University of Montana Graduate Student Theses, Dissertations, & Professional Papers Graduate School 1963 History of radio broadcasting in Montana Ron P. Richards The University of Montana Follow this and additional works at: https://scholarworks.umt.edu/etd Let us know how access to this document benefits ou.y Recommended Citation Richards, Ron P., "History of radio broadcasting in Montana" (1963). Graduate Student Theses, Dissertations, & Professional Papers. 5869. https://scholarworks.umt.edu/etd/5869 This Thesis is brought to you for free and open access by the Graduate School at ScholarWorks at University of Montana. It has been accepted for inclusion in Graduate Student Theses, Dissertations, & Professional Papers by an authorized administrator of ScholarWorks at University of Montana. For more information, please contact [email protected]. THE HISTORY OF RADIO BROADCASTING IN MONTANA ty RON P. RICHARDS B. A. in Journalism Montana State University, 1959 Presented in partial fulfillment of the requirements for the degree of Master of Arts in Journalism MONTANA STATE UNIVERSITY 1963 Approved by: Chairman, Board of Examiners Dean, Graduate School Date Reproduced with permission of the copyright owner. Further reproduction prohibited without permission. UMI Number; EP36670 All rights reserved INFORMATION TO ALL USERS The quality of this reproduction is dependent upon the quality of the copy submitted. In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if material had to be removed, a note will indicate the deletion. UMT Oiuartation PVUithing UMI EP36670 Published by ProQuest LLC (2013). -

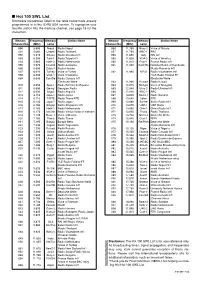

Hot 100 SWL List Shortwave Frequencies Listed in the Table Below Have Already Programmed in to the IC-R5 USA Version

I Hot 100 SWL List Shortwave frequencies listed in the table below have already programmed in to the IC-R5 USA version. To reprogram your favorite station into the memory channel, see page 16 for the instruction. Memory Frequency Memory Station Name Memory Frequency Memory Station Name Channel No. (MHz) name Channel No. (MHz) name 000 5.005 Nepal Radio Nepal 056 11.750 Russ-2 Voice of Russia 001 5.060 Uzbeki Radio Tashkent 057 11.765 BBC-1 BBC 002 5.915 Slovak Radio Slovakia Int’l 058 11.800 Italy RAI Int’l 003 5.950 Taiw-1 Radio Taipei Int’l 059 11.825 VOA-3 Voice of America 004 5.965 Neth-3 Radio Netherlands 060 11.910 Fran-1 France Radio Int’l 005 5.975 Columb Radio Autentica 061 11.940 Cam/Ro National Radio of Cambodia 006 6.000 Cuba-1 Radio Havana /Radio Romania Int’l 007 6.020 Turkey Voice of Turkey 062 11.985 B/F/G Radio Vlaanderen Int’l 008 6.035 VOA-1 Voice of America /YLE Radio Finland FF 009 6.040 Can/Ge Radio Canada Int’l /Deutsche Welle /Deutsche Welle 063 11.990 Kuwait Radio Kuwait 010 6.055 Spai-1 Radio Exterior de Espana 064 12.015 Mongol Voice of Mongolia 011 6.080 Georgi Georgian Radio 065 12.040 Ukra-2 Radio Ukraine Int’l 012 6.090 Anguil Radio Anguilla 066 12.095 BBC-2 BBC 013 6.110 Japa-1 Radio Japan 067 13.625 Swed-1 Radio Sweden 014 6.115 Ti/RTE Radio Tirana/RTE 068 13.640 Irelan RTE 015 6.145 Japa-2 Radio Japan 069 13.660 Switze Swiss Radio Int’l 016 6.150 Singap Radio Singapore Int’l 070 13.675 UAE-1 UAE Radio 017 6.165 Neth-1 Radio Netherlands 071 13.680 Chin-1 China Radio Int’l 018 6.175 Ma/Vie Radio Vilnius/Voice -

Radio Broadcasting

Programs of Study Leading to an Associate Degree or R-TV 15 Broadcast Law and Business Practices 3.0 R-TV 96C Campus Radio Station Lab: 1.0 of Radiologic Technology. This is a licensed profession, CHLD 10H Child Growth 3.0 R-TV 96A Campus Radio Station Lab: Studio 1.0 Hosting and Management Skills and a valid Social Security number is required to obtain and Lifespan Development - Honors Procedures and Equipment Operations R-TV 97A Radio/Entertainment Industry 1.0 state certification and national licensure. or R-TV 96B Campus Radio Station Lab: Disc 1.0 Seminar Required Courses: PSYC 14 Developmental Psychology 3.0 Jockey & News Anchor/Reporter Skills R-TV 97B Radio/Entertainment Industry 1.0 RAD 1A Clinical Experience 1A 5.0 and R-TV 96C Campus Radio Station Lab: Hosting 1.0 Work Experience RAD 1B Clinical Experience 1B 3.0 PSYC 1A Introduction to Psychology 3.0 and Management Skills Plus 6 Units from the following courses (6 Units) RAD 2A Clinical Experience 2A 5.0 or R-TV 97A Radio/Entertainment Industry Seminar 1.0 R-TV 03 Sportscasting and Reporting 1.5 RAD 2B Clinical Experience 2B 3.0 PSYC 1AH Introduction to Psychology - Honors 3.0 R-TV 97B Radio/Entertainment Industry 1.0 R-TV 04 Broadcast News Field Reporting 3.0 RAD 3A Clinical Experience 3A 7.5 and Work Experience R-TV 06 Broadcast Traffic Reporting 1.5 RAD 3B Clinical Experience 3B 3.0 SPCH 1A Public Speaking 4.0 Plus 6 Units from the Following Courses: 6 Units: R-TV 09 Broadcast Sales and Promotion 3.0 RAD 3C Clinical Experience 3C 7.5 or R-TV 05 Radio-TV Newswriting 3.0 -

Digital Radio Broadcasting Network in the Arctic Region

______________________________________________________PROCEEDING OF THE 24TH CONFERENCE OF FRUCT ASSOCIATION Digital Radio Broadcasting Network in the Arctic Region Oleg Varlamov, Vladimir Varlamov, Anna Dolgopyatova Moscow Technical University of Communications and Informatics Moscow, Russia [email protected], [email protected], [email protected] Abstract—Successful economic development of the Arctic 81°), where the geostationary orbit (GEO) is observed very low zone is impossible without creating a continuous information field above the horizon and only a small portion of it is visible, that covers its entire territory and is available not only at where the satellites of the required operator are not always stationary objects, but primarily in moving vehicles - ships, cars, present, providing information fields using satellites located on airplanes, etc. This information field must consist from the GEO is not possible. Approximately from 81 ° to the poles transmission of audio information (broadcasting programs), data (weather maps, ice conditions, etc.), navigation signals, alerts and GEO from the surface of the Earth is not visible even information about emergencies, and must be reserved from theoretically. different sources. As a backup system (and in the coming years, The most promising for the formation of the main the main one) it is advisable to use single-frequency digital information field in the Arctic zone can be considered satellite broadcasting networks of the Digital Radio Mondiale standard in the low frequency range. This is the most economical system for systems in highly elliptical (HEO) or low Earth (LEO) orbits. covering remote areas. For the use of these systems, have all the At the same time, the high cost of such systems, the long period necessary regulatory framework and standard high-efficiency of infrastructure deployment and the limited lifespan, combined radio transmitters. -

A Guide for Radio Operators BROCHURE RADIO TRANSM ANG 3/27/97 8:47 PM Page 2

BROCHURE RADIO TRANSM ANG 3/27/97 8:47 PM Page 17 A Guide for Radio Operators BROCHURE RADIO TRANSM ANG 3/27/97 8:47 PM Page 2 Aussi disponible en français. 32-EN-95539W-01 © Minister of Public Works and Government Services Canada 1996 BROCHURE RADIO TRANSM ANG 3/27/97 8:47 PM Page 3 CUTTING THROUGH... INTERFERENCE FROM RADIO TRANSMITTERS A Guide for Radio Operators This brochure is primarily for amateur and General Radio Service (GRS, commonly known as CB) radio operators. It provides basic information to help you install and maintain your station so you get the best performance and the most enjoyment from it. You will learn how to identify the causes of radio interference in nearby electronic equipment, and how to fix the problem. What type of equipment can be affected by radio interference? Both radio and non-radio devices can be adversely affected by radio signals. Radio devices include AM and FM radios, televisions, cordless telephones and wireless intercoms. Non-radio electronic equipment includes stereo audio systems, wired telephones and regular wired intercoms. All of this equipment can be disturbed by radio signals. What can cause radio interference? Interference usually occurs when radio transmitters and electronic equipment are operated within close range of each other. Interference is caused by: ■ incorrectly installed radio transmitting equipment; ■ an intense radio signal from a nearby transmitter; ■ unwanted signals (called spurious radiation) generated by the transmitting equipment; and ■ not enough shielding or filtering in the electronic equipment to prevent it from picking up unwanted signals. What can you do? 1. -

En 300 720 V2.1.0 (2015-12)

Draft ETSI EN 300 720 V2.1.0 (2015-12) HARMONISED EUROPEAN STANDARD Ultra-High Frequency (UHF) on-board vessels communications systems and equipment; Harmonised Standard covering the essential requirements of article 3.2 of the Directive 2014/53/EU 2 Draft ETSI EN 300 720 V2.1.0 (2015-12) Reference REN/ERM-TG26-136 Keywords Harmonised Standard, maritime, radio, UHF ETSI 650 Route des Lucioles F-06921 Sophia Antipolis Cedex - FRANCE Tel.: +33 4 92 94 42 00 Fax: +33 4 93 65 47 16 Siret N° 348 623 562 00017 - NAF 742 C Association à but non lucratif enregistrée à la Sous-Préfecture de Grasse (06) N° 7803/88 Important notice The present document can be downloaded from: http://www.etsi.org/standards-search The present document may be made available in electronic versions and/or in print. The content of any electronic and/or print versions of the present document shall not be modified without the prior written authorization of ETSI. In case of any existing or perceived difference in contents between such versions and/or in print, the only prevailing document is the print of the Portable Document Format (PDF) version kept on a specific network drive within ETSI Secretariat. Users of the present document should be aware that the document may be subject to revision or change of status. Information on the current status of this and other ETSI documents is available at http://portal.etsi.org/tb/status/status.asp If you find errors in the present document, please send your comment to one of the following services: https://portal.etsi.org/People/CommiteeSupportStaff.aspx Copyright Notification No part may be reproduced or utilized in any form or by any means, electronic or mechanical, including photocopying and microfilm except as authorized by written permission of ETSI. -

High-Frequency Radiowa Ve Probing of the High-Latitude Ionosphere

RAYMOND A. GREENWALD HIGH-FREQUENCY RADIOWAVE PROBING OF THE HIGH-LATITUDE IONOSPHERE During the past several years, a program of high-frequency radiowave studies of the high-latitude ionosphere has been developed in the APL Space Department. Studies are now being conducted on the formation and motion of high-latitude ionospheric electron density irregularities, using a sophisti cated high-frequency radar system installed at Goose Bay, .Labrador. The radar antenna is also being used to receive signals from a beacon transmitter located at Thule, Greenland. This information is providing a better understanding of the spatial and temporal variability of high-latitude propagation channels and their relationship to disturbances in the magnetosphere-ionosphere system . INTRODUCTION turbances prior to their impingement on the magneto At altitudes above 100 kilometers, the atmosphere sphere is quite limited. Therefore, we still have only of the earth gradually changes from a predominantly limited success in forecasting sudden changes in the neutral medium to an increasingly ionized gas or plas high-latitude ionosphere and consequently in high ma. The ionization is caused chiefly by a combination latitude radiowave propagation. of solar extreme ultraviolet radiation and, at high lati In order for space scientists to obtain a better un tudes, particle precipitation from the earth's magne derstanding of the various interactions occurring tosphere. Because of its ionized nature between 100 among the solar wind, the magnetosphere, and the ion and 1000 kilometers, this part of the atmosphere is osphere, active measurement programs are conduct commonly referred to as the ionosphere. In this re ed in all three regions. -

Portable Shortwave Receivers

Portable Shortwave Receivers ● Longwave, AM, FM and Shortwave ELITE SATELLIT ● VHF Air Band ● HD Radio Reception ● RDS Display ● Superior Sensitivity and Selectivity ● Dual Conversion Design ● Huge 5.7 Inch Backlit Display ● Drift-free Digital Phase Lock Loop ● Direct Frequency and Band Entry ● Single Sideband Synchronous Detector ● Selectable Bandwidths ● High Dynamic Range ● Dual Programmable Clocks ● Dual Event Programmable Timers ● Stereo Line Level Input ● Stereo Line Level Output ● Earphone Jack ● Separate Bass and Treble Controls ● Adjustable AGC: Fast or Slow ● Telescopic Antenna AM/FM/SW ● Battery (4xD) or Included AC Adapter ● Scan and Search ● 1700 Total Memories (500 alphanumeric) ● Deluxe Carry Bag The Elite Satellit is simply the finest full-sized portable in the world. The Elite Satellit is an elegant confluence of performance, features and capabilities. The look, feel and finish of this radio is superb. The solid, quality feel is second to none. The digitally synthesized, dual conversion shortwave tuner covers all long wave, mediums wave (AM) and shortwave frequencies. HD Radio improves audio fidelity and adds additional programming without a subscription fee. Adjacent frequency interference can be minimized or eliminated with a choice of three bandwidths [7.0, 4.0, 2.5 kHz]. The sideband selectable Synchronous AM Detector further minimizes adjacent frequency interference and reduces fading distortion of AM signals. IF Passband Tuning is yet another advanced feature that functions in AM and SSB modes to reject interference. AGC is selectable at fast or slow. High dynamic range permits the detection of weak signals in the presence of strong signals. All this coupled with great sensitivity will bring in stations from every part of the globe. -

Hans Knot International Radio Report April 2016 Welcome to Another

Hans Knot International Radio Report April 2016 Welcome to another edition of the International Radio Report. Thanks all for your e mails, memories, photos, questions and more. Part of the report is what was left after the March edition was totally filled and so let’s go with this edition in which first there’s space for a story I wrote last months after again doing some research: ‘Ronan O’Rahilly, Georgie Fame and the Blue Fames. Where it really went wrong!’ On this subject I’ve written before but let’s go back in time and also add some new facts to it: ‘Was Ronan O’Rahilly the manager of Georgie Fame?’ I can tell you there was a problem with an important instrument. When in April 1964 Granada Television came with an edition of the ‘World in action’ series, which was a production from Michael Hodges, they informed the television public about a new form of Piracy, the watery pirates. Two radio ships bringing music and entertainment under the names of Radio Caroline and Radio Atlanta. Radio Caroline was the first 20th century Pirate off the British coast with programs, at that stage, for 12 hours a day. Interviews with the Caroline people were made in the offices of Queen Magazine in the city of London and included – among others – Jocelyn Stevens and the then 23-year old Irish Ronan O’Rahilly. During this documentary it became known, which we would also read in several newspapers in the then following weeks, that Ronan O’Rahilly had started his radiostation Caroline as he couldn’t get his artists played on stations like Radio Luxembourg. -

FM Stereo Format 1

A brief history • 1931 – Alan Blumlein, working for EMI in London patents the stereo recording technique, using a figure-eight miking arrangement. • 1933 – Armstrong demonstrates FM transmission to RCA • 1935 – Armstrong begins 50kW experimental FM station at Alpine, NJ • 1939 – GE inaugurates FM broadcasting in Schenectady, NY – TV demonstrations held at World’s Fair in New York and Golden Gate Interna- tional Exhibition in San Francisco – Roosevelt becomes first U.S. president to give a speech on television – DuMont company begins producing television sets for consumers • 1942 – Digital computer conceived • 1945 – FM broadcast band moved to 88-108MHz • 1947 – First taped US radio network program airs, featuring Bing Crosby – 3M introduces Scotch 100 audio tape – Transistor effect demonstrated at Bell Labs • 1950 – Stereo tape recorder, Magnecord 1250, introduced • 1953 – Wireless microphone demonstrated – AM transmitter remote control authorized by FCC – 405-line color system developed by CBS with ”crispening circuits” to improve apparent picture resolution 1 – FCC reverses its decision to approve the CBS color system, deciding instead to authorize use of the color-compatible system developed by NTSC – Color TV broadcasting begins • 1955 – Computer hard disk introduced • 1957 – Laser developed • 1959 – National Stereophonic Radio Committee formed to decide on an FM stereo system • 1960 – Stereo FM tests conducted over KDKA-FM Pittsburgh • 1961 – Great Rose Bowl Hoax University of Washington vs. Minnesota (17-7) – Chevrolet Impala ‘Super Sport’ Convertible with 409 cubic inch V8 built – FM stereo transmission system approved by FCC – First live televised presidential news conference (John Kennedy) • 1962 – Philips introduces audio cassette tape player – The Beatles release their first UK single Love Me Do/P.S.