Chap02: Instructions

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

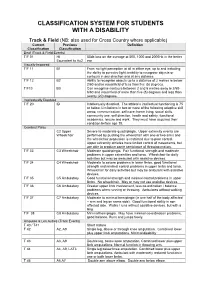

Disability Classification System

CLASSIFICATION SYSTEM FOR STUDENTS WITH A DISABILITY Track & Field (NB: also used for Cross Country where applicable) Current Previous Definition Classification Classification Deaf (Track & Field Events) T/F 01 HI 55db loss on the average at 500, 1000 and 2000Hz in the better Equivalent to Au2 ear Visually Impaired T/F 11 B1 From no light perception at all in either eye, up to and including the ability to perceive light; inability to recognise objects or contours in any direction and at any distance. T/F 12 B2 Ability to recognise objects up to a distance of 2 metres ie below 2/60 and/or visual field of less than five (5) degrees. T/F13 B3 Can recognise contours between 2 and 6 metres away ie 2/60- 6/60 and visual field of more than five (5) degrees and less than twenty (20) degrees. Intellectually Disabled T/F 20 ID Intellectually disabled. The athlete’s intellectual functioning is 75 or below. Limitations in two or more of the following adaptive skill areas; communication, self-care; home living, social skills, community use, self direction, health and safety, functional academics, leisure and work. They must have acquired their condition before age 18. Cerebral Palsy C2 Upper Severe to moderate quadriplegia. Upper extremity events are Wheelchair performed by pushing the wheelchair with one or two arms and the wheelchair propulsion is restricted due to poor control. Upper extremity athletes have limited control of movements, but are able to produce some semblance of throwing motion. T/F 33 C3 Wheelchair Moderate quadriplegia. Fair functional strength and moderate problems in upper extremities and torso. -

Pdp11-40.Pdf

processor handbook digital equipment corporation Copyright© 1972, by Digital Equipment Corporation DEC, PDP, UNIBUS are registered trademarks of Digital Equipment Corporation. ii TABLE OF CONTENTS CHAPTER 1 INTRODUCTION 1·1 1.1 GENERAL ............................................. 1·1 1.2 GENERAL CHARACTERISTICS . 1·2 1.2.1 The UNIBUS ..... 1·2 1.2.2 Central Processor 1·3 1.2.3 Memories ........... 1·5 1.2.4 Floating Point ... 1·5 1.2.5 Memory Management .............................. .. 1·5 1.3 PERIPHERALS/OPTIONS ......................................... 1·5 1.3.1 1/0 Devices .......... .................................. 1·6 1.3.2 Storage Devices ...................................... .. 1·6 1.3.3 Bus Options .............................................. 1·6 1.4 SOFTWARE ..... .... ........................................... ............. 1·6 1.4.1 Paper Tape Software .......................................... 1·7 1.4.2 Disk Operating System Software ........................ 1·7 1.4.3 Higher Level Languages ................................... .. 1·7 1.5 NUMBER SYSTEMS ..................................... 1-7 CHAPTER 2 SYSTEM ARCHITECTURE. 2-1 2.1 SYSTEM DEFINITION .............. 2·1 2.2 UNIBUS ......................................... 2-1 2.2.1 Bidirectional Lines ...... 2-1 2.2.2 Master-Slave Relation .. 2-2 2.2.3 Interlocked Communication 2-2 2.3 CENTRAL PROCESSOR .......... 2-2 2.3.1 General Registers ... 2-3 2.3.2 Processor Status Word ....... 2-4 2.3.3 Stack Limit Register 2-5 2.4 EXTENDED INSTRUCTION SET & FLOATING POINT .. 2-5 2.5 CORE MEMORY . .... 2-6 2.6 AUTOMATIC PRIORITY INTERRUPTS .... 2-7 2.6.1 Using the Interrupts . 2-9 2.6.2 Interrupt Procedure 2-9 2.6.3 Interrupt Servicing ............ .. 2-10 2.7 PROCESSOR TRAPS ............ 2-10 2.7.1 Power Failure .............. -

Framework for In-Field Analyses of Performance and Sub-Technique Selection in Standing Para Cross-Country Skiers

sensors Article Framework for In-Field Analyses of Performance and Sub-Technique Selection in Standing Para Cross-Country Skiers Camilla H. Carlsen 1,*, Julia Kathrin Baumgart 1, Jan Kocbach 1,2, Pål Haugnes 1 , Evy M. B. Paulussen 1,3 and Øyvind Sandbakk 1 1 Centre for Elite Sports Research, Department of Neuromedicine and Movement Science, Faculty of Medicine and Health Sciences, Norwegian University of Science and Technology, 7491 Trondheim, Norway; [email protected] (J.K.B.); [email protected] (J.K.); [email protected] (P.H.); [email protected] (E.M.B.P.); [email protected] (Ø.S.) 2 NORCE Norwegian Research Centre AS, 5008 Bergen, Norway 3 Faculty of Health, Medicine & Life Sciences, Maastricht University, 6200 MD Maastricht, The Netherlands * Correspondence: [email protected]; Tel.: +47-452-40-788 Abstract: Our aims were to evaluate the feasibility of a framework based on micro-sensor technology for in-field analyses of performance and sub-technique selection in Para cross-country (XC) skiing by using it to compare these parameters between elite standing Para (two men; one woman) and able- bodied (AB) (three men; four women) XC skiers during a classical skiing race. The data from a global navigation satellite system and inertial measurement unit were integrated to compare time loss and selected sub-techniques as a function of speed. Compared to male/female AB skiers, male/female Para skiers displayed 19/14% slower average speed with the largest time loss (65 ± 36/35 ± 6 s/lap) Citation: Carlsen, C.H.; Kathrin found in uphill terrain. -

Field Indicators of Hydric Soils

United States Department of Field Indicators of Agriculture Natural Resources Hydric Soils in the Conservation Service United States In cooperation with A Guide for Identifying and Delineating the National Technical Committee for Hydric Soils Hydric Soils, Version 8.2, 2018 Field Indicators of Hydric Soils in the United States A Guide for Identifying and Delineating Hydric Soils Version 8.2, 2018 (Including revisions to versions 8.0 and 8.1) United States Department of Agriculture, Natural Resources Conservation Service, in cooperation with the National Technical Committee for Hydric Soils Edited by L.M. Vasilas, Soil Scientist, NRCS, Washington, DC; G.W. Hurt, Soil Scientist, University of Florida, Gainesville, FL; and J.F. Berkowitz, Soil Scientist, USACE, Vicksburg, MS ii In accordance with Federal civil rights law and U.S. Department of Agriculture (USDA) civil rights regulations and policies, the USDA, its Agencies, offices, and employees, and institutions participating in or administering USDA programs are prohibited from discriminating based on race, color, national origin, religion, sex, gender identity (including gender expression), sexual orientation, disability, age, marital status, family/parental status, income derived from a public assistance program, political beliefs, or reprisal or retaliation for prior civil rights activity, in any program or activity conducted or funded by USDA (not all bases apply to all programs). Remedies and complaint filing deadlines vary by program or incident. Persons with disabilities who require alternative means of communication for program information (e.g., Braille, large print, audiotape, American Sign Language, etc.) should contact the responsible Agency or USDA’s TARGET Center at (202) 720-2600 (voice and TTY) or contact USDA through the Federal Relay Service at (800) 877-8339. -

CS61C : Machine Structures •Remember: “Load from Memory”

inst.eecs.berkeley.edu/~cs61c CS61C : Machine Structures Review Lecture 9 – Introduction to MIPS • In MIPS Assembly Language: Data Transfer & Decisions I • Registers replace C variables • One Instruction (simple operation) per line • Simpler is Better, Smaller is Faster Lecturer PSOE Dan Garcia • New Instructions: www.cs.berkeley.edu/~ddgarcia add, addi, sub Future HVD 1 TB disks! ⇒ The future of digital storage • New Registers: (past the DVD, Blu-Ray and HD DVD) C Variables: $s0 - $s7 may be the Holographic Versatile Disc. Temporary Variables: $t0 - $t7 A massive 1 TB on each (200 DVDs)! 1TB www.zdnet.com.au/news/hardware/0,2000061702,39180148,00.htm Zero: $zero CS61C L09 Introduction to MIPS: Data Transfer & Decisions I (1) Garcia © UCB CS61C L09 Introduction to MIPS: Data Transfer & Decisions I (2) Garcia © UCB Assembly Operands: Memory Anatomy: 5 components of any Computer Registers are in the datapath of the • C variables map onto registers; what processor; if operands are in memory, about large data structures like arrays? Personal Computer we must transfer them to the processor to operate on them, and • 1 of 5 components of a computer: then transfer back to memory when done. memory contains such data structures Computer Processor Memory Devices • But MIPS arithmetic instructions only operate on registers, never directly on Control Input (“brain”) memory. Store (to) Datapath • Data transfer instructions transfer data Registers Output between registers and memory: Load (from) • Memory to register • Register to memory These are “data -

Evaluation of the FEMA P-695 Methodology for Quantification of Building Seismic Performance Factors

NIST GCR 10-917-8 Evaluation of the FEMA P-695 Methodology for Quantification of Building Seismic Performance Factors NEHRP Consultants Joint Venture A partnership of the Applied Technology Council and the Consortium of Universities for Research in Earthquake Engineering Disclaimers This report was prepared for the Engineering Laboratory of the National Institute of Standards and Technology (NIST) under the National Earthquake Hazards Reduction Program (NEHRP) Earthquake Structural and Engineering Research Contract SB134107CQ0019, Task Orders 67344 and 68002. The statements and conclusions contained herein are those of the authors and do not necessarily reflect the views and policies of NIST or the U.S. Government. This report was produced by the NEHRP Consultants Joint Venture, a partnership of the Applied Technology Council (ATC) and the Consortium of Universities for Research in Earthquake Engineering (CUREE). While endeavoring to provide practical and accurate information, the NEHRP Consultants Joint Venture, the authors, and the reviewers assume no liability for, nor express or imply any warranty with regard to, the information contained herein. Users of information contained in this report assume all liability arising from such use. The policy of NIST is to use the International System of Units (metric units) in all of its publications. However, in North America in the construction and building materials industry, certain non-SI units are so widely used instead of SI units that it is more practical and less confusing to include measurement values for customary units only. Cover photo – Illustration of steel concentrically braced frame archetype for performance evaluation. NIST GCR 10-917-8 Evaluation of the FEMA P-695 Methodology for Quantification of Building Seismic Performance Factors Prepared for U.S. -

National Classification? 13

NATIONAL CL ASSIFICATION INFORMATION FOR MULTI CLASS SWIMMERS Version 1.2 2019 PRINCIPAL PARTNER MAJOR PARTNERS CLASSIFICATION PARTNERS Version 1.2 2019 National Swimming Classification Information for Multi Class Swimmers 1 CONTENTS TERMINOLOGY 3 WHAT IS CLASSIFICATION? 4 WHAT IS THE CLASSIFICATION PATHWAY? 4 WHAT ARE THE ELIGIBLE IMPAIRMENTS? 5 CLASSIFICATION SYSTEMS 6 CLASSIFICATION SYSTEM PARTNERS 6 WHAT IS A SPORT CLASS? 7 HOW IS A SPORT CLASS ALLOCATED TO AN ATHLETE? 7 WHAT ARE THE SPORT CLASSES IN MULTI CLASS SWIMMING? 8 SPORT CLASS STATUS 11 CODES OF EXCEPTION 12 HOW DO I CHECK MY NATIONAL CLASSIFICATION? 13 HOW DO I GET A NATIONAL CLASSIFICATION? 13 MORE INFORMATION 14 CONTACT INFORMATION 16 Version 1.2 2019 National Swimming Classification Information for Multi Class Swimmers 2 TERMINOLOGY Assessment Specific clinical procedure conducted during athlete evaluation processes ATG Australian Transplant Games SIA Sport Inclusion Australia BME Benchmark Event CISD The International Committee of Sports for the Deaf Classification Refers to the system of grouping athletes based on impact of impairment Classification Organisations with a responsibility for administering the swimming classification systems in System Partners Australia Deaflympian Representative at Deaflympic Games DPE Daily Performance Environment DSA Deaf Sports Australia Eligibility Criteria Requirements under which athletes are evaluated for a Sport Class Evaluation Process of determining if an athlete meets eligibility criteria for a Sport Class HI Hearing Impairment ICDS International Committee of Sports for the Deaf II Intellectual Impairment Inas International Federation for Sport for Para-athletes with an Intellectual Disability General term that refers to strategic initiatives that address engagement of targeted population Inclusion groups that typically face disadvantage, including people with disability. -

!"#$%&'()*+,-.&/0&,1 23 !"#$45678

!DDDKDCEY ^#D!D ^D#E#DE%K!EY#KY_ :0)% F")(','-/0% </./0%"1l !"#$%&'()*+,-.&/0&,1 ! 23 !"#$45678 !"#! "$%&# "'()$ "*+,$ "%&'())*+,-)),./ 01-2345'67.8! ! 9:1;7<*.8# ! =5 >7?,.8$ ! 4@35'.8;7'.$ '.A %&'())*+,-00:2/ !B!"#$%&'()*$+,-./01$23456!&'"C!DE/D #B!"(78$!9:"/$DDF/ $B!"#$%&'()*$+,-;<=>?$@()*$23456!&'"C!DE/D /BA8BC"D8$()#$+,%!EFG"-%GD#DD !B!"#$%&'(%)'(#*'(+")%,,'-"./01#.%2/03! 45%.-67'5 8.3)/)5)"'*4"'07"2/3)(#! 97/."3":0%;"2#'*<0/".0"3! 45%.-67'5 C!DE/D! 97/.% #B97/.% =./>"(3/)#'*-"'30/".0"3! ?57%. /$DDF/! 97/.% $B!"#$%&'(%)'(#'*83')'@"4"'07('.','-#%.; 4"'07"2/3)(#! 45%.-67'5 8.3)/)5)"'*4"'07"2/3)(#! 97/."3":0%;"2#'*<0/".0"3! 45%.-67'5 C!DE/D! 97/.% /BA"3"%(07 <07'','*B%()7 <0/".0"3! :53)(%,/%. C%)/'.%,=./>"(3/)#! 9%.&"((% :9DD#DD! :53)(%,/% #D!DED$ED# !"! #D!DED/E#E #$ B %&'() *+! ,-&./! 01 23! *1 4. '(5 677-( 89:;<=<: >?15@ A( B&CDA( %6"E8#"9> !"#$ ')-AFGH'C( 81 I&(-C'7&B'?&A(C-7'?-5&(?C1G&A(&(?J-GA1?J-C(I'C)&(AF?J-4'()5-G-AC-$-7?! K&$-?'(5&?G)-A7A)&D'7&IL7&D'?&A(:!"#$ %&#'()(*+"$ ,+-+"$! ;M"M#$=MN; O=MNP 6$G?C'D?""-)*+*HI*(I&J(J%5KL*A,I*M7+M'.A %5KNOKP. I*)JQ,+')*(,A,I*M7+M&'R,O,,. H*5.A 7. +&,M*5+&,(. 3'.8A,M,! S&7T& H*(Q'I*(I&J(JT*II,(*(,O,)+'.A I*)JQ,+')*(,O,)+7. +&,M*5+&,(. 3'.8A,M,! (,MI,T+7R,)JB?*(Q,(S*(U M588,M+M+&'++&,A,I*M7+M H*5.A 7. -

Computer Architectures an Overview

Computer Architectures An Overview PDF generated using the open source mwlib toolkit. See http://code.pediapress.com/ for more information. PDF generated at: Sat, 25 Feb 2012 22:35:32 UTC Contents Articles Microarchitecture 1 x86 7 PowerPC 23 IBM POWER 33 MIPS architecture 39 SPARC 57 ARM architecture 65 DEC Alpha 80 AlphaStation 92 AlphaServer 95 Very long instruction word 103 Instruction-level parallelism 107 Explicitly parallel instruction computing 108 References Article Sources and Contributors 111 Image Sources, Licenses and Contributors 113 Article Licenses License 114 Microarchitecture 1 Microarchitecture In computer engineering, microarchitecture (sometimes abbreviated to µarch or uarch), also called computer organization, is the way a given instruction set architecture (ISA) is implemented on a processor. A given ISA may be implemented with different microarchitectures.[1] Implementations might vary due to different goals of a given design or due to shifts in technology.[2] Computer architecture is the combination of microarchitecture and instruction set design. Relation to instruction set architecture The ISA is roughly the same as the programming model of a processor as seen by an assembly language programmer or compiler writer. The ISA includes the execution model, processor registers, address and data formats among other things. The Intel Core microarchitecture microarchitecture includes the constituent parts of the processor and how these interconnect and interoperate to implement the ISA. The microarchitecture of a machine is usually represented as (more or less detailed) diagrams that describe the interconnections of the various microarchitectural elements of the machine, which may be everything from single gates and registers, to complete arithmetic logic units (ALU)s and even larger elements. -

United States Olympic Committee and U.S. Department of Veterans Affairs

SELECTION STANDARDS United States Olympic Committee and U.S. Department of Veterans Affairs Veteran Monthly Assistance Allowance Program The U.S. Olympic Committee supports Paralympic-eligible military veterans in their efforts to represent the USA at the Paralympic Games and other international sport competitions. Veterans who demonstrate exceptional sport skills and the commitment necessary to pursue elite-level competition are given guidance on securing the training, support, and coaching needed to qualify for Team USA and achieve their Paralympic dreams. Through a partnership between the United States Department of Veterans Affairs and the USOC, the VA National Veterans Sports Programs & Special Events Office provides a monthly assistance allowance for disabled Veterans of the Armed Forces training in a Paralympic sport, as authorized by 38 U.S.C. § 322(d) and section 703 of the Veterans’ Benefits Improvement Act of 2008. Through the program the VA will pay a monthly allowance to a Veteran with a service-connected or non-service-connected disability if the Veteran meets the minimum VA Monthly Assistance Allowance (VMAA) Standard in his/her respective sport and sport class at a recognized competition. Athletes must have established training and competition plans and are responsible for turning in monthly and/or quarterly forms and reports in order to continue receiving the monthly assistance allowance. Additionally, an athlete must be U.S. citizen OR permanent resident to be eligible. Lastly, in order to be eligible for the VMAA athletes must undergo either national or international classification evaluation (and be found Paralympic sport eligible) within six months of being placed on the allowance pay list. -

PA-RISC 1.1 Architecture and Instruction Set Reference Manual

PA-RISC 1.1 Architecture and Instruction Set Reference Manual HP Part Number: 09740-90039 Printed in U.S.A. February 1994 Third Edition Notice The information contained in this document is subject to change without notice. HEWLETT-PACKARD MAKES NO WARRANTY OF ANY KIND WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Hewlett-Packard shall not be liable for errors contained herein or for incidental or consequential damages in connection with furnishing, performance, or use of this material. Hewlett-Packard assumes no responsibility for the use or reliability of its software on equipment that is not furnished by Hewlett-Packard. This document contains proprietary information which is protected by copyright. All rights are reserved. No part of this document may be photocopied, reproduced, or translated to another language without the prior written consent of Hewlett-Packard Company. Copyright © 1986 – 1994 by HEWLETT-PACKARD COMPANY Printing History The printing date will change when a new edition is printed. The manual part number will change when extensive changes are made. First Edition . November 1990 Second Edition. September 1992 Third Edition . February 1994 Contents Contents . iii Preface. ix 1 Overview . 1-1 Introduction. 1-1 System Features . 1-2 PA-RISC 1.1 Enhancements . 1-2 System Organization . 1-4 2 System Organization . 2-1 Introduction. 2-1 Memory and I/O Addressing . 2-2 Byte Ordering (Big Endian/Little Endian) . 2-3 Levels of PA-RISC. 2-5 Data Types . 2-5 Processing Resources. 2-7 3 Addressing and Access Control. -

List Biathlon Middle Distance

BIATHLON MIDDLE DISTANCE START LIST As of 27 JAN 2018 NPC Sport Start IPCNS WC Bib Name Code Class % Time S1 S2 S3 S4 T Points Points Time Women Middle,Visually Impaired 1 REMIZOVA Elena NPA B3 100 09:30:30 111.04 320 Guide: TOKAREV Andrei 2 GALITSYNA Marina NPA B1 88 09:31:00 106.81 223 Guide: PIROGOV Maksim 3 HOSCH Vivian GER B1 88 09:31:30 91.68 280 Guide: SCHILLINGER F 4 RUBANOVSKA Natalia UKR B2 99 09:32:00 70.17 85 Guide: NESTERENKO Lada 5 KLUG Clara GER B1 88 09:32:30 13.64 280 Guide: HARTL Martin 6 SHYSHKOVA Oksana UKR B2 99 09:33:00 0.00 90 Guide: KAZAKOV Vitaliy 7 LYSOVA Mikhalina (WL) NPA B2 99 09:33:30 0.00 500 Guide: IVANOV Alexey Men Middle,Visually Impaired 11 KANAFIN Kairat KAZ B2 99 09:40:30 204.91 Guide: ZHDANOVICH Anton 12 DUBOIS Thomas FRA B1 88 09:41:00 168.61 126 Guide: SAUVAGE Bastien 13 CHOI Bogue KOR B3 100 09:41:30 162.70 65 Guide: KIM Hyunwoo 14 UDALTSOV Vladimir NPA B3 100 09:42:00 150.03 137 Guide: BOGACHEV Ruslan 15 POVAROV Nikita NPA B3 100 09:42:30 149.93 206 Guide: ELISEEV Pavel 16 PONOMAREV Oleg NPA B2 99 09:43:00 137.80 32 Guide: ROMANOV Andrei 17 GARBOWSKI Piotr POL B3 100 09:43:30 135.49 69 Guide: TWARDOWSKI J 18 ARTEMOV Aleksandr NPA B1 88 09:44:00 125.38 209 Guide: CHEREPANOV Ilia 19 MAKHOTKIN Oleksandr UKR B3 100 09:44:30 124.74 16 Guide: NIKULIN Denys 20 HOLUB Yury BLR B3 100 09:45:00 82.45 45 Guide: BUDZILOVICH D 21 POLUKHIN Nikolai NPA B2 99 09:45:30 73.45 345 Guide: BEREZIN Eduard 22 CHALENCON Anthony FRA B1 88 09:46:00 22.36 133 Guide: VALVERDE Simon 23 LUK'YANENKO Vitaliy UKR B3 100 09:46:30