CASPER: Embedding Power Estimation and Hardware

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Openpiton: an Open Source Manycore Research Framework

OpenPiton: An Open Source Manycore Research Framework Jonathan Balkind Michael McKeown Yaosheng Fu Tri Nguyen Yanqi Zhou Alexey Lavrov Mohammad Shahrad Adi Fuchs Samuel Payne ∗ Xiaohua Liang Matthew Matl David Wentzlaff Princeton University fjbalkind,mmckeown,yfu,trin,yanqiz,alavrov,mshahrad,[email protected], [email protected], fxiaohua,mmatl,[email protected] Abstract chipset Industry is building larger, more complex, manycore proces- sors on the back of strong institutional knowledge, but aca- demic projects face difficulties in replicating that scale. To Tile alleviate these difficulties and to develop and share knowl- edge, the community needs open architecture frameworks for simulation, synthesis, and software exploration which Chip support extensibility, scalability, and configurability, along- side an established base of verification tools and supported software. In this paper we present OpenPiton, an open source framework for building scalable architecture research proto- types from 1 core to 500 million cores. OpenPiton is the world’s first open source, general-purpose, multithreaded manycore processor and framework. OpenPiton leverages the industry hardened OpenSPARC T1 core with modifica- Figure 1: OpenPiton Architecture. Multiple manycore chips tions and builds upon it with a scratch-built, scalable uncore are connected together with chipset logic and networks to creating a flexible, modern manycore design. In addition, build large scalable manycore systems. OpenPiton’s cache OpenPiton provides synthesis and backend scripts for ASIC coherence protocol extends off chip. and FPGA to enable other researchers to bring their designs to implementation. OpenPiton provides a complete verifica- tion infrastructure of over 8000 tests, is supported by mature software tools, runs full-stack multiuser Debian Linux, and has been widespread across the industry with manycore pro- is written in industry standard Verilog. -

Day 2, 1640: Leveraging Opensparc

Leveraging OpenSPARC ESA Round Table 2006 on Next Generation Microprocessors for Space Applications G.Furano, L.Messina – TEC-EDD OpenSPARC T1 • The T1 is a new-from-the-ground-up SPARC microprocessor implementation that conforms to the UltraSPARC architecture 2005 specification and executes the full SPARC V9 instruction set. Sun has produced two previous multicore processors: UltraSPARC IV and UltraSPARC IV+, but UltraSPARC T1 is its first microprocessor that is both multicore and multithreaded. • The processor is available with 4, 6 or 8 CPU cores, each core able to handle four threads. Thus the processor is capable of processing up to 32 threads concurrently. • Designed to lower the energy consumption of server computers, the 8-cores CPU uses typically 72 W of power at 1.2 GHz. G.Furano, L.Messina – TEC-EDD 72W … 1.2 GHz … 90nm … • Is a cutting edge design, targeted for high-end servers. • NOT FOR SPACE USE • But, let’s see which are the potential spin-in … G.Furano, L.Messina – TEC-EDD Why OPEN ? On March 21, 2006, Sun made the UltraSPARC T1 processor design available under the GNU General Public License. The published information includes: • Verilog source code of the UltraSPARC T1 design, including verification suite and simulation models • ISA specification (UltraSPARC Architecture 2005) • The Solaris 10 OS simulation images • Diagnostics tests for OpenSPARC T1 • Scripts, open source and Sun internal tools needed to simulate the design and to do synthesis of the design • Scripts and documentation to help with FPGA implementation -

Workshop on Recent Trends in Processor Architecture

Workshop on Recent Trends in Procesor Architecture – OpenSPARC March 17, 2007 Ramesh Iyer Sr. Engineering Manager Shrenik Mehta Senior Director, Frontend Technologies & OpenSPARC Program David Weaver Sr. Staff Engineer, UltraSPARC Architect Jhy-Chun (JC) Wang Sr. Staff Engineer Systems Group Sun Microsystems, Inc. www.opensparc.net Agenda 1.Chip Multi-Threading (CMT) Era 2.Microarchitecture of OpenSPARC T1 3.OpenSPARC T1 Program 4.SPARC Architecture 5.OpenSPARC in Academia 6.OpenSPARC T1 simulators 7.Hypervisor and OS porting 8.Compiler Optimizations and tools 9.Community Participation www.opensparc.net Recent Trends in Processor Architecture -2007 , NIT Trichy, India 2 Making the Right Waves Chip Multi-threading (CoolThreadsTM) Symmetrical Multi-processing (SMP) e c n Reduced Instruction Set a m Computing (RISC) r o f r e P / e c i r P d e v o r p m I 1980 1990 2000 2010 www.opensparc.net Recent Trends in Processor Architecture -2007 , NIT Trichy, India 3 The Processor Growth Single Chip Multiprocessors Multiple cores Integer Unit Data Center >350M xstors <20K gates 1982 1990 1998 2005 RISC SMP RAS SWAP 64 bit CMT Source: Sun Network San Francisco, NC03Q3, Sep. 17, 2003 The Big Bang Is Happening— Four Converging Trends Network Computing Is Moore’s Law Thread Rich A fraction of the die can Web services, JavaTM already build a good applications, database processor core; how am I transactions, ERP . going to use a billion transistors? Worsening Growing Complexity Memory Latency of Processor Design It’s approaching 1000s Forcing a rethinking of of CPU cycles! Friend or foe? processor architecture – modularity, less is more, time-to-market www.opensparc.net Recent Trends in Processor Architecture -2007 , NIT Trichy, India 5 The Big Bang Has Happened— Four Converging Trends Network Computing Is Moore’s Law Thread Rich A fraction of the die can Web services, JavaTM already build a good applications, database processor core; how am I transactions, ERP . -

Dynamic Voltage and Frequency Scaling with Multi-Clock Distribution Systems on SPARC Core" (2009)

Rochester Institute of Technology RIT Scholar Works Theses Thesis/Dissertation Collections 5-1-2009 Dynamic voltage and frequency scaling with multi- clock distribution systems on SPARC core Michael Nasri Michael Follow this and additional works at: http://scholarworks.rit.edu/theses Recommended Citation Michael, Michael Nasri, "Dynamic voltage and frequency scaling with multi-clock distribution systems on SPARC core" (2009). Thesis. Rochester Institute of Technology. Accessed from This Thesis is brought to you for free and open access by the Thesis/Dissertation Collections at RIT Scholar Works. It has been accepted for inclusion in Theses by an authorized administrator of RIT Scholar Works. For more information, please contact [email protected]. Dynamic Voltage and Frequency Scaling with Multi-Clock Distribution Systems on SPARC Core by Michael Nasri Michael A Thesis Submitted in Partial Fulfillment of the Requirements for the Degree of Master of Science in Computer Engineering Supervised by Dr. Dhireesha Kudithipudi Department of Computer Engineering Kate Gleason College of Engineering Rochester Institute of Technology Rochester, NY May 2009 Approved By: Dr. Dhireesha Kudithipudi Assistant Professor, RIT Department of Computer Engineering Primary Advisor Dr. Ken Hsu Professor, RIT Department of Computer Engineering Dr. Muhammad Shaaban Associate Professor, RIT Department of Computer Engineering Thesis Release Permission Form Rochester Institute of Technology Kate Gleason College of Engineering Title: Dynamic Voltage and Frequency Scaling with Multi-Clock Distribution Systems on SPARC Core I, Michael Nasri Michael, hereby grant permission to the Wallace Memorial Library to reproduce my thesis in whole or part. Michael Nasri Michael Date Dedication To my parents for their pride and encouragement To my brother and sisters for their love and support Acknowledgements Thanks to Dr. -

Estudio De Arquitecturas En Soft-Proccesors Y Comparativa De Rendimiento Y Consumo Con Procesadores Comerciales

Universidad Carlos III de Madrid Escuela Politécnica Superior Ingeniería Informática Proyecto Fin de Carrera Madrid, Octubre 2012 Estudio de arquitecturas en soft-proccesors y comparativa de rendimiento y consumo con procesadores comerciales Autor: Víctor Nieto Talaván Tutores: David Expósito Singh Oscar Pérez Alonso Estudio de arquitecturas en soft-proccesors y comparativa de rendimiento y consumo con procesadores comerciales Víctor Nieto Talaván 2 Estudio de arquitecturas en soft-proccesors y comparativa de rendimiento y consumo con procesadores comerciales Agradecimientos Este proyecto se lo quiero agradecer de la mejor manera posible a toda la gente que me ha apoyado a lo largo de mi vida, en especial a toda mi familia. Mi hermano Marcos, mis padres Julio y Mari Carmen, y mi novia Bea forman parte de mi día a día, y sin ellos no habría conseguido seguir adelante. Siempre han estado ahí para todo, para lo bueno y lo malo, y eso es lo mejor que me ha podido pasar. En segundo lugar se lo quiero agradecer a mis amigos, David, Castre, Fombe, Honorio, Marta y Rocío, por ser capaces de aguantarme y animarme todo este tiempo. Tampoco puedo olvidar los buenos momentos que he pasado con mis compañeros de clase, Champi, Cristian, Sohrab, Alberto, Juanto y un largo etc. de personas que han conseguido hacerme sacar una carcajada y una sonrisa. Finalmente, me gustaría agradecer enormemente toda la ayuda que he recibido por parte de mis tutores, David y Oscar, por su gran apoyo en este proyecto, sus conocimientos y su paciencia. No olvidaré los buenos momentos pasados con la gente del laboratorio, por todas las risas que he podido compartir con ellos y por conseguir hacer que finalice este proyecto. -

Opensparc™ Internals

ISBN 978-0-557-01974-8 90000 > 9 780557 019748 OpenSPARC™ Internals OpenSPARC T1/T2 CMT Throughput Computing David L. Weaver, Editor Sun Microsystems, Inc. 4150 Network Circle Santa Clara, CA 95054 U.S.A. 650-960-1300 Copyright 2002-2008 Sun Microsystems, Inc., 4150 Network Circle • Santa Clara, CA 950540 USA. All rights reserved. This product or document is protected by copyright and distributed under licenses restricting its use, copying, distribution, and decompilation. No part of this product or document may be reproduced in any form by any means without prior written authorization of Sun and its licensors, if any. Third-party software, including font technology, is copyrighted and licensed from Sun suppliers. Parts of the product may be derived from Berkeley BSD systems, licensed from the University of California. UNIX is a registered trademark in the U.S. and other countries, exclusively licensed through X/Open Company, Ltd. For Netscape Communicator, the following notice applies: Copyright 1995 Netscape Communications Corporation. All rights reserved. Sun, Sun Microsystems, the Sun logo, Solaris, OpenSolaris, OpenSPARC, Java, MAJC, Sun Fire, UltraSPARC, and VIS are trademarks, registered trademarks, or service marks of Sun Microsystems, Inc. or its subsidiaries in the U.S. and other countries. All SPARC trademarks are used under license and are trademarks or registered trademarks of SPARC International, Inc. in the U.S. and other countries. Products bearing SPARC trademarks are based upon an architecture developed by Sun Microsystems, Inc. The OPEN LOOK and Sun Graphical User Interface was developed by Sun Microsystems, Inc. for its users and licensees. Sun acknowledges the pioneering efforts of Xerox in researching and developing the concept of visual or graphical user interfaces for the computer industry. -

Opensparc Slide-Cast

OpenSPARC Slide-Cast In 12 Chapters Presented by OpenSPARC designers, developers, and programmers ●to guide users as they develop their own OpenSPARC designs and ●to assist professors as they This materialteach the is made next available generation under Creative Commons Attribution-Share 3.0 United States License www.opensparc.net CreativeCreative Commons Commons Attribution-Share Attribution-Share 3.0 3.0 United United States States License License 394 Chapter Twelve OPENSPARC COMMUNITY PARTICIPATION David L. Weaver Principal Engineer, UltraSPARC Architecture Principal Evangelist, OpenSPARC Sun Microsystems www.opensparc.net CreativeCreative Commons Commons Attribution-Share Attribution-Share 3.0 3.0 United United States States License License 395 OpenSPARC in Academia www.opensparc.net Creative Commons Attribution-Share 3.0 United States License 396 64 bits, 64 threads, and free® University Programs for OpenSPARC • Sun supports academic use of OpenSPARC > Collaborations > Centers of Excellence (CoEs) > For university: > access to real, modern industrial microprocessor designs and full verification test suites! > publicity and prestige that aids in obtaining grants > Sharing of course material on OpenSPARC website > Hosting of projects on OpenSPARC website > For additional information, send email to: [email protected] 397 www.opensparc.net Creative Commons Attribution-Share 3.0 United States License 64 bits, 64 threads, and free® University Uses for OpenSPARC: Starting point for lab courses S a working design that -

Report on Major Classes of Hardware Components Page 2 of 31

Project Number: FP7-611404 D3.1 – Report on major classes of hard- ware components Authors M. Kaliorakis, S. Tselonis, N. Foutris, D. Gizopoulos Version 1.7 – 5/8/2014 Lead contractor: University of Athens Contact person: Dimitris Gizopoulos University of Athens Department of Informatics & Telecommunications Panepistimiopolis, Ilissia 15784, Athens (Greece) Tel. +30 210 7275145 Fax. +30 210 7275214 E-mail: [email protected] Work package: WP3 Affected tasks: T3.1 Nature of deliverable1 R P D O Dissemination level2 PU PP RE CO 1 R: Report, P: Prototype, D: Demonstrator, O: Other 2 PU: public, PP: Restricted to other programme participants (including the commission services), RE Restrict- ed to a group specified by the consortium (including the Commission services), CO Confidential, only for members of the consortium (Including the Commission services) D3.1: Report on major classes of hardware components Page 2 of 31 COPYRIGHT © COPYRIGHT CLERECO Consortium consisting of: • Politecnico di Torino (Italy) – Short name: POLITO • National and Kapodistrian University of Athens (Greece) - Short name: UoA • Centre National de la Recherche Scientifique - Laboratoire d'Informatique, de Ro- botique et de Microélectronique de Montpellier (France) - Short name: CNRS • Intel Corporation Iberia S.A. (Spain) - Short name: INTEL • Thales SA (France) - Short name: THALES • Yogitech s.p.a. (Italy) - Short name: YOGITECH • ABB (Norway) - Short name: ABB • Universitat Politècnica de Catalunya: UPC CONFIDENTIALITY NOTE THIS DOCUMENT MAY NOT BE COPIED, REPRODUCED, OR MODIFIED IN WHOLE OR IN PART FOR ANY PURPOSE WITHOUT WRITTEN PERMISSION FROM THE CLERECO CONSORTIUM. IN ADDITION TO SUCH WRITTEN PERMISSION TO COPY, REPRODUCE, OR MODIFY THIS DOCUMENT IN WHOLE OR PART, AN ACKNOWLEDGMENT OF THE AUTHORS OF THE DOCUMENT AND ALL APPLICABLE PORTIONS OF THE COPYRIGHT NOTICE MUST BE CLEARLY REFERENCED ALL RIGHTS RESERVED. -

Nios II/F 1800 Xilinx Microblaze 1324

4.12.2014 Computer System Structures cz:Struktury počítačových systémů Version: 1.0 Lecturer: Richard Šusta ČVUT-FEL in Prague, CR – subject A0B35SPS Microprocessors 2 1 4.12.2014 Definition: Microprocessor A Microprocessor is a Single VLSI Chip that has a CPU and may also have some Other Units (for example, caches, floating point processing arithmetic unit, pipelining, and super-scaling units) Source Microprocessor Family Motorola 68HCxxx Intel 80x86 & i860 Sun SPARC IBM PowerPC Source: Raj Kamal, Embedded Systems: Architecture, Programming and Design 3 Existovalo a dodnes existuje mnoho typů od různých výrobců http://research.microsoft.com/en-us/um/people/gbell/CyberMuseum_contents/Microprocessor_Evolution_Poster.jpg 2 4.12.2014 From 8 bit to 32 bit CISC processors 8 bit µ-processor 8008 8080 8085 Z80 Year 1972 1974 1976 1976 Instructions 66 111 113 158 MIPS 0.06 0.29 0.37 0.58 Minimum system (IO circuits) 20-40 7 3 3 16 and 32 bit 64bit example: Intel 8086/88 80286 80386 80486 Pentium I5-2500K Quad core µ-processor Year 1978/79 1982 1985-91 1989-94 1993-98 2011 Instructions processor 133 ~175 ~195 ~200 ~225 ~500 + numeric cooprocessor MIPS 0.33-0.75 0.9-2.6 2.5-11 16-70 100-300 ~80000 Memory Physical / Virtual 1 MB 16 MB/1 GB 4 GB / 64TB 32 GB / 256 TB Definition: Microcontroller A microcontroller is a single-chip VLSI unit which, though having limited computational capabilities possesses enhanced input- output capabilities and a number of on- chip functional units Source Microcontroller Family Motorola 68HC11xx, HC12xx, HC16xx Intel -

Open Source Hardware

Open Source Hardware Erik Rubow November 20, 2008 1 Introduction The open source software movement has had an enormous impact on today’s techonology. We see this more and more in recent years. It has aided academic research, it has changed the way many tech companies do business, and it has changed our society. More recently (though not for the first time), the idea of open source hardware has been getting a lot of attention. The purpose of this paper is to identify the strengths and weaknesses of open source hardware, get an overview of the current state of open source hardware, and discuss its future. 2 Defining Open Source Hardware There is no clear and widely accepted definition of ”open source hardware”. The Open Source Initiative (OSI) maintains what they call ”The Open Source Defi- nition”, though it was written with software in mind. One reasonable definition is found in the TAPR Open Hardware License[13]: Open Hardware is a thing - a physical artifact, either electrical or mechanical - whose design information is available to, and usable by, the public in a way that allows anyone to make, modify, distribute, and use that thing. [17] gives three requirements for something to ”fully qualify as ’open hard- ware’”: 1. The interface to the hardware must be explicitly made public, so the hardware can be used freely. 2. The design of the hardware must be made public, so that others can implement it and learn from it. 3. The tools used to create the design should be free, so that others can develop and improve the design. -

Opencore and Other Soft Core Processors up Cores T Est Folder

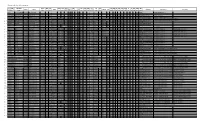

Opencore and other soft core processors _uP_cores_t opencores style / data inst repor com LUTs blk F tool MIPS clks/ KIPS src # src tool fltg Ha max max byte # # pipe start last status author FPGA top file doc reference note worthy comments date LUT? est folder name clone size size ter ment ALUT mults ram max ver /clk inst /LUT code files chain pt vd data inst adrs inst reg len year revis 1664 1664 microprocessorsim? Denis Godinho C 26 2010 2010 C based simulation only X 4stack simulationBernd Paysan forth 32 5 kintex-7-3 James Brakefieldsource errors 6 ## 14.7 0.67 1.0 verilog 80 4stack yes yes Y 2002 2011 bernd-paysan.de/b16.html 6502_verilog_design6502_verilog_desigsim? Hyungok Tak 6502 8 8x verilog yes N N 64K 64K Y 2010 2010 6502 data sheets no files, simulated 6502vhdl 6502vhdl planning Huyvo 6502 8 8x C yes N N 64K 64K Y 2003 2009 6502 data sheets to have a C program generate VHDL A 6809_6309 6809_6309_compatible_corebeta Alejandro Paz Schmidt 6809 8 8x spartan-6-3 James Brakefield2061 6 109 ## 14.7 0.33 3.0 5.8 verilog 5 MC6809_cpu yes N N 64K 64K Y 2012 2013 6809 data sheets includes 6309 op-codes, xilinx & lattice projects A 1 6809_6309 6809_6309_compatible_corebeta Alejandro Paz Schmidt 6809 8 8x kintex-7-3 James Brakefield2207 6 212 ## 14.7 0.33 3.0 10.6 verilog 5 MC6809_cpu yes N N 64K 64K Y 2012 2013 6809 data sheets includes 6309 op-codes, xilinx & lattice projects B 1 68hc05 68hc05 stable Ulrich Riedel 6805 8 8x kintex-7-3 James Brakefield1225 6 300 ## 14.7 0.33 4.0 20.2 vhdl 1 6805 yes N N 64K 64K Y 2007 2009 6805 data -

A Practical Hardware Implementation of Systemic Computation

UNIVERSITY COLLEGE LONDON A Practical Hardware Implementation of Systemic Computation by Christos Sakellariou A thesis submitted in partial fulfilment for the degree of Doctor of Engineering in the Faculty of Engineering Department of Computer Science December 2013 2 Declaration of Authorship I, Christos Sakellariou, declare that this thesis A Practical Hardware Implementation of Systemic Computation and the work presented in it are my own. I confirm that: This work was done wholly or mainly while in candidature for a research degree at University College London. Where any part of this thesis has previously been submitted for a degree or any other qualification at University College London or any other institution, this has been clearly stated. Where I have consulted the published work of others, this is always clearly attributed. Where I have quoted from the work of others, the source is always given. With the exception of such quotations, this thesis is entirely my own work. I have acknowledged all main sources of help. Where the thesis is based on work done by myself jointly with others, I have made clear exactly what was done by others and what I have contributed myself. Signed: Date: 3 Abstract Faculty of Engineering, Department of Computer Science UNIVERSITY COLLEGE LONDON Doctor of Engineering by Christos Sakellariou It is widely accepted that natural computation, such as brain computation, is far superior to typical computational approaches addressing tasks such as learning and parallel processing. As conventional silicon-based technologies are about to reach their physical limits, researchers have drawn inspiration from nature to found new computational paradigms.