AMD Opteron Processor Product Data Sheet

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

MX690E2 Radeon X1250 for Gaming Applications

Industrial Motherboards AMD® RS690E Mini ITX with Integrated MX690E2 Radeon X1250 for Gaming Applications Audio 2 USB KB + Mouse Features 2 USB + LAN DVI + VGA COM1, COM2 • AMD® Socket AM2/AM2+ Supports Athlon 64, Athlon 64 x2, Sempron with 2000 MHz Hyper Transport • AMD® RS690E/SB600 Chipset Amplifi er ATX • Up to 4 GB DDR2 533/667/800 MHz SO-DIMM Sys- LVDS tem Memory PCIe x16 • ATI® Radeon Xpress1250 Graphic Engine RS690E • Dual Display: DVI-D, LVDS, VGA • 1 Gigabit LAN, HD Audio, Amplifi er Socket AM2 • 1 PCI, 1 Mini PCIe, Compact Flash SB600 • 2 SATA, 4 COM, 6 USB, 8-bit GPIO 2 SATA • TPM 1.2 Supported DIO • ATX Power COM3 COM4 • Mini ITX (6.7” x 6.7”) Mini PCIe CF (back) IDE 2 USB Front Panel 2 SO-DIMMs up to 4 GB Specifi cation ATX Power DDR2 SDRAM System Audio CPU Supports AMD® Socket AM2 support Athlon 64, Athlon 64 X AC’97 Codec Realtek® ALC888/ALC886 Audio Codec 2, Sempron with FSB 2000MHz Hyper Transport support with Audio Amplifer TPA3005D2 Stereo 5Watt per channel 200/400/600/800/1000 MHz Chipsets AMD® RS690E + SB600 Ethernet System Memory Two 200-pin SO-DIMM supports up to 4 GB DDR2 SDRAM LAN 1 Realtek® RTL8111B (1000Base-T Fast Ethernet) 400/533/667/800 MHz BIOS SPI Award 8 Mb BIOS Mechanical and Environment Expansion Interface 1 x PCI 1 x CF Power Requirement 42W (Max). ( 3.3V, 3.08A , 5V 0.817A, 5VSB 0.387A, 12V 2.18A) 1 x Mini PCIe Operating Temperature 0~60°C TPM TPM1.2 (Infi neon® TPM chip 9635 TT 1.2 on board) Operating Humidity 5%~90% relative humidity, non-condensing Watchdog Timer Reset: 1 sec.~255 min. -

AMD Socket AM2 with AMD M690T Chipset Reference Schematic D D

5 4 3 2 1 AMD Socket AM2 with AMD M690T Chipset Reference Schematic D D NOTES: Page Index Page Index ------- -------------------------------------------- ------- -------------------------------------------- 1) This schematic supports the AMD Socket AM2 CPU devices. 1 Cover Page 17 SB600 PCIe, PCI, LPC, Straps, & CPU Control 2) These are "Reference Schematics" and as such they have 2 Revision History 18 SB600 ACPI, GPIO, USB, and Audio Interfaces not been verified by an actual board build. 3 Block Diagram 19 SB SATA, IDE, SPI, and HW Management Interfaces 3) This reference schematic supports AMD M960T revision 4 Clock Structure 20 SB600 Power A12 or later. If A12 or later revision is not used, please 5 Power Configuration (1) 21 CRT Connector see your customer support representative for the 6 Power Configuration (2) 22 Broadcom Ethernet Controller necessary application notes for workarounds. 7 Reset & Voltage Sequence 23 Realtek Audio Codec C 4) This reference schematic supports SB600 revision 8 Socket AM2 HT Interface 24 LPC BIOS C A21 or later. If A21 or later revision is not used, please 9 Socket AM2 DDRII Memory Interface 25 USB Power and Connectors see your customer support representative for the 10 Socket AM2 Control & Debug 26 Power Main System, SB600 PCIe, & Other necessary application notes for workarounds. 11 Socket AM2 Power & Ground 27 Standby Power & Powergood 5) Unless otherwise specified, resistors have 5% tolerance. 12 SODIMM DDR2 28 Power for CPU Core 13 M690T HT, PCI, PCIe(R), PCIe Graphics Port 29 Power for DDR2 Memory and Interface 6) Unless otherwise specified, capacitors have 20% tolerance. 14 M690T PLL and Video Interface 30 Power M690T Core, PCIe Interface 15 M690T Power and Side Port Memory Interface 31 Unused Interfaces 16 Clock Generator IMPORTANT NOTICE: B 1. -

Cray XT and Cray XE Y Y System Overview

Crayyy XT and Cray XE System Overview Customer Documentation and Training Overview Topics • System Overview – Cabinets, Chassis, and Blades – Compute and Service Nodes – Components of a Node Opteron Processor SeaStar ASIC • Portals API Design Gemini ASIC • System Networks • Interconnection Topologies 10/18/2010 Cray Private 2 Cray XT System 10/18/2010 Cray Private 3 System Overview Y Z GigE X 10 GigE GigE SMW Fibre Channels RAID Subsystem Compute node Login node Network node Boot /Syslog/Database nodes 10/18/2010 Cray Private I/O and Metadata nodes 4 Cabinet – The cabinet contains three chassis, a blower for cooling, a power distribution unit (PDU), a control system (CRMS), and the compute and service blades (modules) – All components of the system are air cooled A blower in the bottom of the cabinet cools the blades within the cabinet • Other rack-mounted devices within the cabinet have their own internal fans for cooling – The PDU is located behind the blower in the back of the cabinet 10/18/2010 Cray Private 5 Liquid Cooled Cabinets Heat exchanger Heat exchanger (XT5-HE LC only) (LC cabinets only) 48Vdc flexible Cage 2 buses Cage 2 Cage 1 Cage 1 Cage VRMs Cage 0 Cage 0 backplane assembly Cage ID controller Interconnect 01234567 Heat exchanger network cable Cage inlet (LC cabinets only) connection air temp sensor Airflow Heat exchanger (slot 3 rail) conditioner 48Vdc shelf 3 (XT5-HE LC only) 48Vdc shelf 2 L1 controller 48Vdc shelf 1 Blower speed controller (VFD) Blooewer PDU line filter XDP temperature XDP interface & humidity sensor -

Supermicro H8DME-2

Supermicro H8DME-2 Key Features 1. Dual AMD® Opteron™ 2000 Series (Socket F) Support, 1000 MHz HyperTransport Link 2. nVidia MCP55 Pro / NEC uPD720400 Chipset 3. Up to 32GB DDR2 667 SDRAM Up to 32GB DDR2 533 SDRAM Up to 64GB DDR2 400 SDRAM 4. Dual-port Gigabit LAN/Ethernet Controller 5. 6 SATA2 3.0Gb/s HDD Support 6. 2 x8 PCI-e, 2 64-bit 133/100MHz PCI-X, 2 64-bit 100MHz PCI-X 7. ATI ES1000 Graphics 8. SIMLC IPMI 2.0 Support 9. 8 Fan Support with Speed Control Product SKUs Chassis ( Optimized for H8DME-2 ) MBD-H8DME-2- • H8DME-2 (Standard Retail Pack) O • CSE-825TQ-560LPV * • CSE-825TQ-R700LPV * MBD-H8DME-2- • H8DME-2 (Bulk Pack) B 2U Chassis * Please use air-shroud MCP-310-00025- 01 Physical Stats (Air-shrouds sold separately) • CSE-745TQ-800 • Extended ATX Form Factor • CSE-745TQ-R800 • CSE-745TQ-700 • 12" x 13.05" (30.5cm x 33.2cm) • Dimensions CSE-745TQ-R700 Rackmount • CSE-743TQ-R760 Tower / 4U • CSE-743T-R760 Processor/Chipset • CSE-743i-R760 • CSE-743T-650 • Dual 1207-pin Socket F • CSE-743i-650 • Supports up to two AMD Opteron™ 2000 Series (Socket F) processor(s) CPU • • Dual-core Support To ensure system stability, a 420W (minimum) ATX power supply Important [ 4-pin (+12V), 8-pin (+12V) and 24- • 1000MHz HyperTransport Chassis Notes pin are required] System Bus • nVidia MCP55 Pro Chipset • NEC uPD720400 Expansion Slots • 2 x8 PCI-e slots • System Memory 1 SEPC (Supermicro extended Power Connector) slot for 2U active PCI-Express • riser cards with a power extension Sixteen 240-pin DIMM sockets (i.e. -

CPU CARD Industral Motherboard

CPU CARD Industral Motherboard ATX Form Factor with AMD SocketAM2 Processor, Nvidia MCP55Pro Server Grade Platform, Analog CRT output, Six SATA II with RAID Functions, Dual IMBA-3600AM2 LAN, One PCIe x8 and Five PCIe x4 Expansion Slot, CF Card 4 x 240-pin DIMM ATX Power Input Six SATA II AMD Socket AM2 USB 1 Single Board CF NVIDIA MCP55pro server-grade chipset Five PCIe x 4 with One PCI Computer IDE COM Dual GbE 2 VIDEO PCI CARD KB/MS VGA 6 x USB2.0 Audio 3 Xscale PCIe x16 Slot for Solutions COM PCIe x 8 Signals Five PCIe x4 4 Specifications Open Ethernet DDR2800 HMI CPU AMD Socket AM2 Supports Athlont™ 64, Athlon™ 64 x2, AMD™ 64 Opteron™ , AMD Sempron™ processors Features HyperTransport™ Technology 5 200/400/600/800/1000MHz HyperTransport Interface 1. AMD Socket AM2 processor with HyperTransport™ technology supported VITO System Chipsets 2. Built in NVIDIA MCP55Pro (NFP-3600) supports 28 configurable PCI Universal NVIDIA MCP55Pro (NFP-3600) Server Grade Platform express lanes Controller BIOS 3. 6 x SATA II support RAID 0, 1, 0+1, 5, JBOD AMI Flash BIOS 4. One PCIe x16 (x8 single) and five PCIe x4 expansion slots for felxible System Memory PCIe application 4x DDR2 DIMM support 400/533/667/800 MHz up to 8G 5. Dual LAN support fail over/load balancing Ethernet 6 Dual GbE (Marvell 88E1121 PHY) DINO BLADE I/O Interface 1 x RS-232 Packing List 1 x RS-232/422/485 8 x USB 2.0(6 on the edge, 2 on board by pin header) 1 x IMBA-3600AM2 single board computer 6 x SATA II with RAID 0,1, 10, 5, JBOD support 7 1 x IDE 1 x Mini jumper pack LCD 1 x Audio -

AMD's Early Processor Lines, up to the Hammer Family (Families K8

AMD’s early processor lines, up to the Hammer Family (Families K8 - K10.5h) Dezső Sima October 2018 (Ver. 1.1) Sima Dezső, 2018 AMD’s early processor lines, up to the Hammer Family (Families K8 - K10.5h) • 1. Introduction to AMD’s processor families • 2. AMD’s 32-bit x86 families • 3. Migration of 32-bit ISAs and microarchitectures to 64-bit • 4. Overview of AMD’s K8 – K10.5 (Hammer-based) families • 5. The K8 (Hammer) family • 6. The K10 Barcelona family • 7. The K10.5 Shanghai family • 8. The K10.5 Istambul family • 9. The K10.5-based Magny-Course/Lisbon family • 10. References 1. Introduction to AMD’s processor families 1. Introduction to AMD’s processor families (1) 1. Introduction to AMD’s processor families AMD’s early x86 processor history [1] AMD’s own processors Second sourced processors 1. Introduction to AMD’s processor families (2) Evolution of AMD’s early processors [2] 1. Introduction to AMD’s processor families (3) Historical remarks 1) Beyond x86 processors AMD also designed and marketed two embedded processor families; • the 2900 family of bipolar, 4-bit slice microprocessors (1975-?) used in a number of processors, such as particular DEC 11 family models, and • the 29000 family (29K family) of CMOS, 32-bit embedded microcontrollers (1987-95). In late 1995 AMD cancelled their 29K family development and transferred the related design team to the firm’s K5 effort, in order to focus on x86 processors [3]. 2) Initially, AMD designed the Am386/486 processors that were clones of Intel’s processors. -

Six-Core AMD Opteron™ Processor with AMD

AMD最新テクノロジーアップデート -HPCへの取り組み- 日本AMD株式会社 マーケティング&ビジネス開発本部 エンタープライズプロダクトマーケティング部 部長 山野 洋幸 AMD’s HPC Product Portfolio Energy efficient CPU and discrete GPU processors focused on addressing the most demanding HPC workloads Multi-core x86 Processors • Outstanding Performance • Superior Scalability • Enhanced Power Efficiency Professional Graphics • 3D Accelerators For Visualization • See More and Do More with Your Data ATI Stream Computing • GPU Optimized For Computation • Massive Data-parallel Processing • High Performance Per Watt 2 | AMD HPC Product Portfolio Update @ SC’09 | November 30, 2009 For more information be sure to visit AMD at SC’09 booth #1417 AMD’s HPC Product Portfolio Energy efficient CPU and discrete GPU processors focused on addressing the most demanding HPC workloads Multi-core x86 Processors • Outstanding Performance • Superior Scalability • Enhanced Power Efficiency Professional Graphics • 3D Accelerators For Visualization • See More and Do More with Your Data ATI Stream Computing • GPU Optimized For Computation • Massive Data-parallel Processing • High Performance Per Watt 3 | AMD HPC Product Portfolio Update @ SC’09 | November 30, 2009 For more information be sure to visit AMD at SC’09 booth #1417 Planned Server Platform Roadmap 2006 2007 2008 2009 2010 2011 “Maranello” Socket G34 with AMD SR56x0 and SP5100 Magny-Cours New Architecture Six-Core AMD Opteron™ Processor with AMD way Chipset - Socket F(1207) with AMD SR56x0 and SP5100 Shanghai/Istanbul Platform 2/4 Enterprise Enterprise “Socket F (1207)” Socket F(1207) -

Mini-ITX Motherboard, with AMD Socket AM2 for AMD

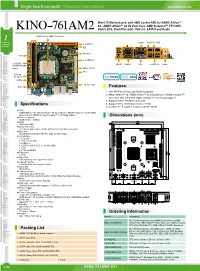

Single board computer / Industrial motherboard www.ieiworld.com Mini-ITX Motherboard, with AMD Socket AM2 for AMD® Athlon™ 64, AMD® Athlon™ 64 X2 Dual-Core, AMD Sempron™ CPU with KINO-761AM2 VGA/ LVDS, Dual PCIe GbE, USB 2.0, SATA II and Audio 1 AMD® Socket AM2 Processor Industrial COM3 Dual PCIe GbE Computing 4 x SATA II Solutions IDE SIS 966 ATX 2 x USB 2.0 2 x DDR2 KB/MS COM1/2 VGA 4 x USB 2.0 Audio 800MHz DIMM 2 socket SIS® 761CX Embedded Computing PCI Solutions Infrared Interface SIS 761CX DDR2 800 COM4 PCIePCI-E 24-bit LVDS DIO Features 1. Mini-ITX Form Factor and RoHS compliant 3 2. AMD® Athlon™ 64, AMD® Athlon™ 64 X2 Dual-Core, AMD® Sempron™ RISC-Based Embedded processor with 2000 MHz HyperTransport™ technology support Solutions 3. Support DDR2 800 MHz up to 4GB Specifications 4. Support VGA, 24-bit dual-channel LVDS 5. 4 x RS-232, 6 x USB 2.0 and 4 x SATA II RAID CPU AMD® Athlon™ 64, AMD® Athlon™ 64 X2 Dual-Core, AMD® Sempron™ Socket AM2 processor with 2000MHz HyperTransport™ technology support System Chipsets Dimensions (mm) SIS® 761CX + SIS966 4 BIOS Industrial Data AMI Flash BIOS Collector/ System Memory Server Solutions 2 x 240-pin dual-channel DDR2 400/533/667/800 MHz up to 4GB Ethernet Dual Broadcom BCM5787M PCI Express GbE chipset I/O Interface 3 x RS-232 1 x RS-232/422/485 6 x USB 2.0 4 x SATA II with RAID 0, 1, 10 and JBOD 5 1 x IDE Video 2 x PS2 for KB/MS Capture Expansion Solutions 1 x PCI Digital I/O 8-bit digital I/O, 4-bit input/ 4-bit output Infrared Interface 1 x Infrared Interface by pin header Super I/O W83697HG Display Interface VGA Intgrated in SiS 761CX 6 24-bit dual-channel LVDS by SiS® 307LV (KINO-761AM2LVDS only) I/O Audio Communication AC'97 codec with Realtek ALC655 Solutions Watchdog Timer Software programmable supports 1 ~255 sec. -

Single Board Computer Full Size

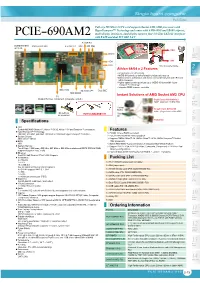

Single board computer Full Size Full-size PICMG 1.3 CPU card supports Socket AM2 AMD processors with HyperTransport™ Technology and comes with AMD 690G and SB600 chipsets, PCIE-690AM2 multi-display interfaces, dual display support, four 3.0 Gbps SATA II interfaces with RAID and dual PCI GbE LAN 4 x SATA II DDR2 800 MHz AMD Socket AM2 6 x USB 2.0 TPM IDE FDD AMD up to 2G DVI-I VGA Socket 1 Infrared Application Server Platform VGA DVI DVI-I DVI-I ConverterCo Cable 2 Athlon 64/64 x 2 Features Single Board Single/Dual Core Processing Computer AMD® 64 technology delivers leading-edge performance Direct connect architecture with direct access memory I/O and CPU core within processor Higher speed, power optimized up to 8GB/S I/O bandwidth Hyper 3 Transport™ technology IBX Series Integrate DDR2 memory controller POS PC AMD 690G HD Audio LPT Dual GbE AMD SB600 Instant Solutions of AMD Socket AM2 CPU TV 4 (Support S-video, component, composite output ) Dual Cores Athlon64 x2 3400+ (Dual Core 1.8 GHz 35W) AFOLUX POS Panel PC Thermal Module Single Core Athlon64 3000+ (Single Core 1.8 GHz 35W) HD audio kit HDTVCABLESET-01 Retention 5 AC-Kit883HD Kit Video Capture Specifications Sempron Card CPU Socket AM2 AMD Opteron™, Athlon™ 64 X2, Athlon™ 64 and Sempron™ processors Features 6 HyperTransport™ Technology 1. PICMG 1.3 and RoHS compliant KAMIO 200 MHz, 400 MHz, 600 MHz, 800 MHz or 1000 MHz HyperTransport™ Interface RISC System Chipset 2. ECC DDR2 unbuffered memory support AMD 690G + SB600 3. -

A740G M2L+ Motherboard

A740G M2L+ Motherboard • Socket AM2/AM2+ • Supports AMD Phenom II Series / Phenom Series / Athlon II / Athlon Processors • Hyper Transport Technology up to 2G • Supports AMD Cool'n'Quiet Technology • Supports BIO-Remote 2 Technology • Supports Charger Booster Technology A740G M2L+ Specifcation CPU SUPPORT AMD Phenom™ II X4 Processor AMD Phenom™ II X3 Processor AMD Phenom™ II X2 Processor AMD Phenom™ X4 Processor AMD Phenom™ X3 Processor AMD Athlon™ II X4 Processor AMD Athlon™ II X3 Processor AMD Athlon™ II X2 Processor AMD Athlon™ X2 Dual-Core Processor AMD Athlon™ 64 X2 Dual-Core Processor AMD Athlon™ 64 FX Processor AMD Athlon™ 64 Processor AMD Sempron™ Processor Maximum CPU TDP (Thermal Design BIOSTARPower) : 95Watt HT Support HT 2G MEMORY Support Dual Channel DDR2 533/667/800/1066 MHz 2 x DDR2 DIMM Memory Slot Max. Supports up to 8GB Memory ※It is recommended to use those Validated DDR2-1066 modules suggested by AMD INTEGRATED VIDEO ATI Radeon™ HD2100 Graphics, On Board Graphic Max. Memory Share Up to 512 MB STORAGE 4 x SATA II Connector 1 x IDE Connector Support SATA RAID: 0,1,10 LAN Realtek RTL8102EL - 10/100 Controller AUDIO CODEC Realtek ALC662 6-Channel HD Audio USB 4 x USB 2.0 Port 2 x USB 2.0 Header EXPANSION SLOT 1 x PCI-E x16 Slot 2 x PCI Slot REAR I/O 1 x PS/2 Mouse 1 x PS/2 Keyboard 4 x USB 2.0 Port 1 x VGA Port 1 x LAN Port 3 x Audio Jacks INTERNAL I/O 2 x USB Header 4 x SATA II Connector (3Gb/s ) 1 x IDE Connector 1 x Floppy Connector 1 x Front Audio Header 1 x Front Panel Header 1 x S/PDIF-Out Header 1 x CPU Fan Connector 1 x System Fan Connector 1 x Printer Port Header DIMENSION Micro ATX Form Factor Dimension: 22.5cm X 18.2cm ( W x L ) OS SUPPORT Supports Windows XP / Vista / 7 ACCESSORIES 2 x SATA Cable 1 x I/O Shield 1 x Fully Setup Driver CD BIOSTAR1 x Quick Guide FEATURES Windows 7 Compatible Supports Solid capacitor BIOS-Flasher A740G M2L+ OVERVIEW *The specification and pictures are subject to change without notice and the package contents may differ by area or your motherboard version! BIOSTAR. -

Six-Core AMD Opteron Processor Istanbul Paul G. Howard, Ph.D

Six-Core AMD Opteron Processor Istanbul Paul G. Howard, Ph.D. Chief Scientist, Microway, Inc. Copyright 2009 by Microway, Inc. In April 2009 AMD™ announced the first 6-core Opteron processor, codenamed Istanbul1; delivery began in June 2009, four months ahead of schedule. Istanbul is based on the AMD 64-bit K10 architecture, and is available for 2-, 4-, and 8-socket systems, with clock speeds ranging from 2.0 to 2.8 GHz. Istanbul is the successor to the quad-core Shanghai processor, launched in 2008. It provides up to 30 percent more performance in the same socket and with the same power draw. Here is a summary of the features of the 6-core Istanbul processor: • Six cores mean more performance, and also more performance per watt because the power and thermal envelopes are the same as for 4-core processors • Consistent architecture, scalable to 2, 4, or 8 processor systems • Energy efficient, incorporates AMD-P power management • Virtualization support using AMD-V • Improved bandwidth, through the use of HyperTransport 3.0 and HT Assist. The current state of AMD Opteron processors Istanbul is based on the AMD K10 64-bit architecture and manufactured on a 45 nm SOI process2. Processors in the K10 line to date are shown in the following table. Code Frequency L3 cache Model number Introduction name Cores Sockets (GHz) (MB) Process range3 date Barcelona 4 4 or 8 1.9-2.5 2 65 nm 8346-8360 September 2007 Barcelona 4 2 1.9-2.5 2 65 nm 2344-2360 September 2007 Budapest 4 1 2.1-2.5 2 65 nm 1352-1356 June 2008 Shanghai 4 4 or 8 2.2-3.1 6 45 nm 8374-8393 November 2008 Shanghai 4 2 2.1-3.1 6 45 nm 2372-2393 November 2008 Suzuka 4 1 2.5-2.9 6 45 nm 1381-1389 June 2009 Istanbul 6 4 or 8 2.1-2.8 6 45 nm 8425-8439 June 2009 Istanbul 6 2 2.0-2.8 6 45 nm 2423-2439 June 2009 Budapest uses the same core as Barcelona, and Suzuka uses the same core as Shanghai. -

Socket E Slot Per

Socket e Slot per CPU Socket e Slot per CPU Socket 1 Socket 2 Socket 3 Socket 4 Socket 5 Socket 6 Socket 7 e Super Socket 7 Socket 8 Slot 1 (SC242) Slot 2 (SC330) Socket 370 (PGA-370) Slot A Socket A (Socket 462) Socket 423 Socket 478 Socket 479 Socket 775 (LGA775) Socket 603 Socket 604 PAC418 PAC611 Socket 754 Socket 939 Socket 940 Socket AM2 (Socket M2) Socket 771 (LGA771) Socket F (Socket 1207) Socket S1 A partire dai processori 486, Intel progettò e introdusse i socket per CPU che, oltre a poter ospitare diversi modelli di processori, ne consentiva anche una rapida e facile sostituzione/aggiornamento. Il nuovo socket viene definito ZIF (Zero Insertion Force ) in quanto l'inserimento della CPU non richiede alcuna forza contrariamente ai socket LIF ( Low Insertion Force ) i quali, oltre a richiedere una piccola pressione per l'inserimento del chip, richiedono anche appositi tool per la sua rimozione. Il modello di socket ZIF installato sulla motherboard è, in genere, indicato sul socket stesso. Tipi diversi di socket accettano famiglie diverse di processori. Se si conosce il tipo di zoccolo montato sulla scheda madre è possibile sapere, grosso modo, che tipo di processori può ospitare. Il condizionale è d'obbligo in quanto per sapere con precisione che tipi di processore può montare una scheda madre non basta sapere solo il socket ma bisogna tenere conto anche di altri fattori come le tensioni, il FSB, le CPU supportate dal BIOS ecc. Nel caso ci si stia apprestando ad aggiornare la CPU è meglio, dunque, attenersi alle informazioni sulla compatibilità fornite dal produttore della scheda madre.