AMD Socket AM2 with AMD M690T Chipset Reference Schematic D D

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Intel Corporation

US RESEARCH | PUBLISHED BY RAYMOND JAMES & ASSOCIATES INTEL CORPORATION (INTC-NASDAQ) JULY 26, 2021 | 8:27 PM EDT Semiconductors COMPANY BRIEF Chris Caso | (212) 856-4893 | [email protected] Melissa Fairbanks | (727) 567-1081 | [email protected] Underperform 4 New Names, Same Problems Suitability M/ACC Intel hosted its "Intel Accelerated" manufacturing roadmap update Monday evening, detailing their process roadmap through 2025. The presentation laid a path through which Intel hopes to MARKET DATA Current Price (Jul-26-21) $54.31 have achieved parity with TSMC (and by extension, AMD) by 2024, and a goal of process leadership Market Cap (mln) $221,802 by 2025. This is no different from the goals laid out by Intel’s new CEO when he came on board Current Net Debt (mln) $10,552 a quarter ago, but the company did provide more details about how they intend to achieve that Enterprise Value (mln) $232,354 Shares Outstanding (mln) 4,084.0 goal. Attaining leadership by 2025 requires Intel to introduce a full process node improvement 30-Day Avg. Daily Value (mln) $1,362.7 each year for the next 4 years – an aggressive assumption given the production missteps from Dividend $1.39 the past several years. What Intel didn’t disclose were the costs of this roadmap, which we Dividend Yield 2.6% 52-Week Range $43.61 - $68.49 expect them to discuss during the November analyst day. And while there is great uncertainty BVPS $14.76 about Intel’s ability to achieve these targets, what’s less uncertain is a requirement for higher Long-Term Debt (mln) $24,632 capital intensity. -

MX690E2 Radeon X1250 for Gaming Applications

Industrial Motherboards AMD® RS690E Mini ITX with Integrated MX690E2 Radeon X1250 for Gaming Applications Audio 2 USB KB + Mouse Features 2 USB + LAN DVI + VGA COM1, COM2 • AMD® Socket AM2/AM2+ Supports Athlon 64, Athlon 64 x2, Sempron with 2000 MHz Hyper Transport • AMD® RS690E/SB600 Chipset Amplifi er ATX • Up to 4 GB DDR2 533/667/800 MHz SO-DIMM Sys- LVDS tem Memory PCIe x16 • ATI® Radeon Xpress1250 Graphic Engine RS690E • Dual Display: DVI-D, LVDS, VGA • 1 Gigabit LAN, HD Audio, Amplifi er Socket AM2 • 1 PCI, 1 Mini PCIe, Compact Flash SB600 • 2 SATA, 4 COM, 6 USB, 8-bit GPIO 2 SATA • TPM 1.2 Supported DIO • ATX Power COM3 COM4 • Mini ITX (6.7” x 6.7”) Mini PCIe CF (back) IDE 2 USB Front Panel 2 SO-DIMMs up to 4 GB Specifi cation ATX Power DDR2 SDRAM System Audio CPU Supports AMD® Socket AM2 support Athlon 64, Athlon 64 X AC’97 Codec Realtek® ALC888/ALC886 Audio Codec 2, Sempron with FSB 2000MHz Hyper Transport support with Audio Amplifer TPA3005D2 Stereo 5Watt per channel 200/400/600/800/1000 MHz Chipsets AMD® RS690E + SB600 Ethernet System Memory Two 200-pin SO-DIMM supports up to 4 GB DDR2 SDRAM LAN 1 Realtek® RTL8111B (1000Base-T Fast Ethernet) 400/533/667/800 MHz BIOS SPI Award 8 Mb BIOS Mechanical and Environment Expansion Interface 1 x PCI 1 x CF Power Requirement 42W (Max). ( 3.3V, 3.08A , 5V 0.817A, 5VSB 0.387A, 12V 2.18A) 1 x Mini PCIe Operating Temperature 0~60°C TPM TPM1.2 (Infi neon® TPM chip 9635 TT 1.2 on board) Operating Humidity 5%~90% relative humidity, non-condensing Watchdog Timer Reset: 1 sec.~255 min. -

Ipox® Portfolio Holding Analysis 02/24/2021

IPOX® PORTFOLIO HOLDING ANALYSIS 02/24/2021 To learn more, visit www.ipox.com; Email: [email protected] MARVELL TECHNOLOGY GROUP LTD (MRVL US) | AQUANTIA CORP (AQ US) Office: +1 (312) 526-3634 COMPANY DESCRIPTION Support +1 (312) 339-4114 ACQUIRER Founded in 1995, Marvell Technology Group is semiconductor company headquartered in Santa Clara, CA. Marvell provides data infrastructure semiconductor solutions for data storage, processing, networking, security and connectivity. TARGET Founded in 2004, Aquantia Corp is a fabless semiconductor company that designs, develops and markets advanced high-speed communications integrated circuits (ICs) for Ethernet connectivity. TARGET IPO HISTORY Aquantia began trading on the NYSE on 11/3/2017 led by Morgan Stanley. The ICs developer sold 6,818,000 shares at $9.00 per share, below its expected price range ($10 to $12). With the 15% greenshoe options fully exercised, Aquantia was valued at ca. $300.09 million. The shares opened at $9.31/share and closed the first day higher at $9.51 (▲5.67%). Aquantia Corp entered the IPOX® Universe on the 7th day of trading. M&A HISTORY Marvell Technology Group announced to buy Aquantia for $452 million on 5/9/2019 at $13.25 per share in cash, which represented a 38.60% premium to Aquantia’s previous close. The acquisition of the Multi-Gig Ethernet company was completed on 9/19/2019. Marvell Technology Group was included in the IPOX® 100 U.S. Portfolio (ETF: FPX) on 3/23/2020 and currently weights approximately 4.90% of the portfolio. *Marvell Technology Group was added to the Nasdaq-100 Index® on December 21, 2020. -

Advanced Micro Devices, Inc. 2485 Augustine Drive Santa Clara, California 95054

ADVANCED MICRO DEVICES, INC. 2485 AUGUSTINE DRIVE SANTA CLARA, CALIFORNIA 95054 NOTICE OF ANNUAL MEETING OF STOCKHOLDERS You are cordially invited to attend our 2020 annual meeting of stockholders (our “Annual Meeting”) to be held on Thursday, May 7, 2020 at 9:00 a.m. Pacific Time. In light of the coronavirus/COVID-19 outbreak and governmental decrees that in-person gatherings be postponed or canceled, and in the best interests of public health and the health and safety of our Board of Directors, employees and stockholders, the Annual Meeting will be held virtually via the Internet at www.virtualshareholdermeeting.com/AMD2020. You will not be able to attend the Annual Meeting in person. We are holding our Annual Meeting to: • Elect the eight director nominees named in this proxy statement; • Ratify the appointment of Ernst & Young LLP as our independent registered public accounting firm for the current fiscal year; • Approve on a non-binding, advisory basis the compensation of our named executive officers, as disclosed in this proxy statement pursuant to the compensation disclosure rules of the U.S. Securities and Exchange Commission (the “SEC”); and • Transact any other business that properly comes before our Annual Meeting or any adjournment or postponement thereof. We are pleased to provide access to our proxy materials over the Internet under the SEC’s “notice and access” rules. As a result, we are mailing to our stockholders (other than those who previously requested printed or emailed materials on an ongoing basis) a Notice of Internet Availability of Proxy Materials (the “Notice”) instead of printed copies of our proxy materials. -

Advanced Micro Devices (AMD)

Strategic Report for Advanced Micro Devices, Inc. Tad Stebbins Andrew Dialynas Rosalie Simkins April 14, 2010 Advanced Micro Devices, Inc. Table of Contents Executive Summary ............................................................................................ 3 Company Overview .............................................................................................4 Company History..................................................................................................4 Business Model..................................................................................................... 7 Market Overview and Trends ...............................................................................8 Competitive Analysis ........................................................................................ 10 Internal Rivalry................................................................................................... 10 Barriers to Entry and Exit .................................................................................. 13 Supplier Power.................................................................................................... 14 Buyer Power........................................................................................................ 15 Substitutes and Complements............................................................................ 16 Financial Analysis ............................................................................................. 18 Overview ............................................................................................................ -

ISTFA 2002 Organizing Committee

ISTFA™ 2002: Conference Proceedings from the 28th Copyright © 2002 ASM International® International Symposium for Testing and Failure Analysis All rights reserved. November 03–November 07, 2002, Phoenix, Arizona, USA www.asminternational.org DOI: 10.31399/asm.cp.istfa2002fm01 ISTFA 2002 Organizing Committee Christian Boit General Chair University of Technology Berlin Berlin, Germany Thomas M. Moore Vice General Chair Omniprobe, Inc. Dallas, TX Richard J. Ross Past General Chair IBM Microelectronics Essex Junction, VT Matt Thayer Symposium Technical Program Chair Advanced Micro Devices Austin, TX Cheryl Hartfield Audio / Visual Chair Texas Instruments Dallas, TX Lee Knauss Publicity Chair Neocera Beltsville, MD Anu Barman Exposition Chair Foveon, Inc. Santa Clara, CA Ingrid DeWolf Panel Discussion & User Group Chair IMECvzw Leuven, Belgium Jerry M. Soden Seminar Chair Sandia National Laboratories Albuquerque, NM iii Downloaded from http://dl.asminternational.org/istfa/proceedings-pdf/ISTFA2002/30774/iii/419327/istfa2002fm01.pdf by guest on 25 September 2021 EDFAS 2002 - 2003 Board of Directors Richard J. Ross Christian Boit EDFAS President Director-At-Large IBM Microelectronics Division University of Technology Berlin Essex Junction, VT Berlin, Germany Edward I. Cole, Jr. Sandra Delgado EDFAS Immediate Past President Director-At-Large Sandia National Laboratories Accurel Systems International Albuquerque, NM Sunny vale, CA Gary F. Shade Jim Erickson EDFAS Vice President Director-At-Large Intel Colorado Springs Design Center Boeing Satellite -

AMD+Investor+Presentation Dec+10

CAUTIONARY STATEMENT This presentation contains forward-looking statements concerning Advanced Micro Devices, Inc. (AMD) such as AMD’s journey, technology investments and plan to drive shareholder returns over the next five years; the proposed transaction with Xilinx, Inc. including expectations, benefits and plans of the proposed transaction; total addressable markets; AMD’s technology roadmaps; the features, functionality, performance, availability, timing and expected benefits of future AMD products; AMD’s data center growth and as the new data center leader; AMD’s product and commercial momentum; and AMD’s long-term financial model, including revenue, non-GAAP gross margin, non-GAAP operating expenses as a percentage of revenue, non-GAAP operating margin and free cash flow margin, which are made pursuant to the Safe Harbor provisions of the Private Securities Litigation Reform Act of 1995. Forward looking statements are commonly identified by words such as "would," "may," "expects," "believes," "plans," "intends," "projects" and other terms with similar meaning. Investors are cautioned that the forward-looking statements in this presentation are based on current beliefs, assumptions and expectations, speak only as of the date of this presentation and involve risks and uncertainties that could cause actual results to differ materially from current expectations. Such statements are subject to certain known and unknown risks and uncertainties, many of which are difficult to predict and generally beyond AMD's control, that could cause actual results and other future events to differ materially from those expressed in, or implied or projected by, the forward-looking information and statements. Investors are urged to review in detail the risks and uncertainties in AMD’s Securities and Exchange Commission filings, including but not limited to AMD’s Quarterly Report on Form 10-Q for the quarter ended September 26, 2020. -

CPU CARD Industral Motherboard

CPU CARD Industral Motherboard ATX Form Factor with AMD SocketAM2 Processor, Nvidia MCP55Pro Server Grade Platform, Analog CRT output, Six SATA II with RAID Functions, Dual IMBA-3600AM2 LAN, One PCIe x8 and Five PCIe x4 Expansion Slot, CF Card 4 x 240-pin DIMM ATX Power Input Six SATA II AMD Socket AM2 USB 1 Single Board CF NVIDIA MCP55pro server-grade chipset Five PCIe x 4 with One PCI Computer IDE COM Dual GbE 2 VIDEO PCI CARD KB/MS VGA 6 x USB2.0 Audio 3 Xscale PCIe x16 Slot for Solutions COM PCIe x 8 Signals Five PCIe x4 4 Specifications Open Ethernet DDR2800 HMI CPU AMD Socket AM2 Supports Athlont™ 64, Athlon™ 64 x2, AMD™ 64 Opteron™ , AMD Sempron™ processors Features HyperTransport™ Technology 5 200/400/600/800/1000MHz HyperTransport Interface 1. AMD Socket AM2 processor with HyperTransport™ technology supported VITO System Chipsets 2. Built in NVIDIA MCP55Pro (NFP-3600) supports 28 configurable PCI Universal NVIDIA MCP55Pro (NFP-3600) Server Grade Platform express lanes Controller BIOS 3. 6 x SATA II support RAID 0, 1, 0+1, 5, JBOD AMI Flash BIOS 4. One PCIe x16 (x8 single) and five PCIe x4 expansion slots for felxible System Memory PCIe application 4x DDR2 DIMM support 400/533/667/800 MHz up to 8G 5. Dual LAN support fail over/load balancing Ethernet 6 Dual GbE (Marvell 88E1121 PHY) DINO BLADE I/O Interface 1 x RS-232 Packing List 1 x RS-232/422/485 8 x USB 2.0(6 on the edge, 2 on board by pin header) 1 x IMBA-3600AM2 single board computer 6 x SATA II with RAID 0,1, 10, 5, JBOD support 7 1 x IDE 1 x Mini jumper pack LCD 1 x Audio -

AMD's Early Processor Lines, up to the Hammer Family (Families K8

AMD’s early processor lines, up to the Hammer Family (Families K8 - K10.5h) Dezső Sima October 2018 (Ver. 1.1) Sima Dezső, 2018 AMD’s early processor lines, up to the Hammer Family (Families K8 - K10.5h) • 1. Introduction to AMD’s processor families • 2. AMD’s 32-bit x86 families • 3. Migration of 32-bit ISAs and microarchitectures to 64-bit • 4. Overview of AMD’s K8 – K10.5 (Hammer-based) families • 5. The K8 (Hammer) family • 6. The K10 Barcelona family • 7. The K10.5 Shanghai family • 8. The K10.5 Istambul family • 9. The K10.5-based Magny-Course/Lisbon family • 10. References 1. Introduction to AMD’s processor families 1. Introduction to AMD’s processor families (1) 1. Introduction to AMD’s processor families AMD’s early x86 processor history [1] AMD’s own processors Second sourced processors 1. Introduction to AMD’s processor families (2) Evolution of AMD’s early processors [2] 1. Introduction to AMD’s processor families (3) Historical remarks 1) Beyond x86 processors AMD also designed and marketed two embedded processor families; • the 2900 family of bipolar, 4-bit slice microprocessors (1975-?) used in a number of processors, such as particular DEC 11 family models, and • the 29000 family (29K family) of CMOS, 32-bit embedded microcontrollers (1987-95). In late 1995 AMD cancelled their 29K family development and transferred the related design team to the firm’s K5 effort, in order to focus on x86 processors [3]. 2) Initially, AMD designed the Am386/486 processors that were clones of Intel’s processors. -

SMBIOS Specification

1 2 Document Identifier: DSP0134 3 Date: 2019-10-31 4 Version: 3.4.0a 5 System Management BIOS (SMBIOS) Reference 6 Specification Information for Work-in-Progress version: IMPORTANT: This document is not a standard. It does not necessarily reflect the views of the DMTF or its members. Because this document is a Work in Progress, this document may still change, perhaps profoundly and without notice. This document is available for public review and comment until superseded. Provide any comments through the DMTF Feedback Portal: http://www.dmtf.org/standards/feedback 7 Supersedes: 3.3.0 8 Document Class: Normative 9 Document Status: Work in Progress 10 Document Language: en-US 11 System Management BIOS (SMBIOS) Reference Specification DSP0134 12 Copyright Notice 13 Copyright © 2000, 2002, 2004–2019 DMTF. All rights reserved. 14 DMTF is a not-for-profit association of industry members dedicated to promoting enterprise and systems 15 management and interoperability. Members and non-members may reproduce DMTF specifications and 16 documents, provided that correct attribution is given. As DMTF specifications may be revised from time to 17 time, the particular version and release date should always be noted. 18 Implementation of certain elements of this standard or proposed standard may be subject to third party 19 patent rights, including provisional patent rights (herein "patent rights"). DMTF makes no representations 20 to users of the standard as to the existence of such rights, and is not responsible to recognize, disclose, 21 or identify any or all such third party patent right, owners or claimants, nor for any incomplete or 22 inaccurate identification or disclosure of such rights, owners or claimants. -

Lista Sockets.Xlsx

Data de Processadores Socket Número de pinos lançamento compatíveis Socket 0 168 1989 486 DX 486 DX 486 DX2 Socket 1 169 ND 486 SX 486 SX2 486 DX 486 DX2 486 SX Socket 2 238 ND 486 SX2 Pentium Overdrive 486 DX 486 DX2 486 DX4 486 SX Socket 3 237 ND 486 SX2 Pentium Overdrive 5x86 Socket 4 273 março de 1993 Pentium-60 e Pentium-66 Pentium-75 até o Pentium- Socket 5 320 março de 1994 120 486 DX 486 DX2 486 DX4 Socket 6 235 nunca lançado 486 SX 486 SX2 Pentium Overdrive 5x86 Socket 463 463 1994 Nx586 Pentium-75 até o Pentium- 200 Pentium MMX K5 Socket 7 321 junho de 1995 K6 6x86 6x86MX MII Slot 1 Pentium II SC242 Pentium III (Cartucho) 242 maio de 1997 Celeron SEPP (Cartucho) K6-2 Socket Super 7 321 maio de 1998 K6-III Celeron (Socket 370) Pentium III FC-PGA Socket 370 370 agosto de 1998 Cyrix III C3 Slot A 242 junho de 1999 Athlon (Cartucho) Socket 462 Athlon (Socket 462) Socket A Athlon XP 453 junho de 2000 Athlon MP Duron Sempron (Socket 462) Socket 423 423 novembro de 2000 Pentium 4 (Socket 423) PGA423 Socket 478 Pentium 4 (Socket 478) mPGA478B Celeron (Socket 478) 478 agosto de 2001 Celeron D (Socket 478) Pentium 4 Extreme Edition (Socket 478) Athlon 64 (Socket 754) Socket 754 754 setembro de 2003 Sempron (Socket 754) Socket 940 940 setembro de 2003 Athlon 64 FX (Socket 940) Athlon 64 (Socket 939) Athlon 64 FX (Socket 939) Socket 939 939 junho de 2004 Athlon 64 X2 (Socket 939) Sempron (Socket 939) LGA775 Pentium 4 (LGA775) Pentium 4 Extreme Edition Socket T (LGA775) Pentium D Pentium Extreme Edition Celeron D (LGA 775) 775 agosto de -

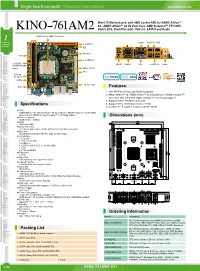

Mini-ITX Motherboard, with AMD Socket AM2 for AMD

Single board computer / Industrial motherboard www.ieiworld.com Mini-ITX Motherboard, with AMD Socket AM2 for AMD® Athlon™ 64, AMD® Athlon™ 64 X2 Dual-Core, AMD Sempron™ CPU with KINO-761AM2 VGA/ LVDS, Dual PCIe GbE, USB 2.0, SATA II and Audio 1 AMD® Socket AM2 Processor Industrial COM3 Dual PCIe GbE Computing 4 x SATA II Solutions IDE SIS 966 ATX 2 x USB 2.0 2 x DDR2 KB/MS COM1/2 VGA 4 x USB 2.0 Audio 800MHz DIMM 2 socket SIS® 761CX Embedded Computing PCI Solutions Infrared Interface SIS 761CX DDR2 800 COM4 PCIePCI-E 24-bit LVDS DIO Features 1. Mini-ITX Form Factor and RoHS compliant 3 2. AMD® Athlon™ 64, AMD® Athlon™ 64 X2 Dual-Core, AMD® Sempron™ RISC-Based Embedded processor with 2000 MHz HyperTransport™ technology support Solutions 3. Support DDR2 800 MHz up to 4GB Specifications 4. Support VGA, 24-bit dual-channel LVDS 5. 4 x RS-232, 6 x USB 2.0 and 4 x SATA II RAID CPU AMD® Athlon™ 64, AMD® Athlon™ 64 X2 Dual-Core, AMD® Sempron™ Socket AM2 processor with 2000MHz HyperTransport™ technology support System Chipsets Dimensions (mm) SIS® 761CX + SIS966 4 BIOS Industrial Data AMI Flash BIOS Collector/ System Memory Server Solutions 2 x 240-pin dual-channel DDR2 400/533/667/800 MHz up to 4GB Ethernet Dual Broadcom BCM5787M PCI Express GbE chipset I/O Interface 3 x RS-232 1 x RS-232/422/485 6 x USB 2.0 4 x SATA II with RAID 0, 1, 10 and JBOD 5 1 x IDE Video 2 x PS2 for KB/MS Capture Expansion Solutions 1 x PCI Digital I/O 8-bit digital I/O, 4-bit input/ 4-bit output Infrared Interface 1 x Infrared Interface by pin header Super I/O W83697HG Display Interface VGA Intgrated in SiS 761CX 6 24-bit dual-channel LVDS by SiS® 307LV (KINO-761AM2LVDS only) I/O Audio Communication AC'97 codec with Realtek ALC655 Solutions Watchdog Timer Software programmable supports 1 ~255 sec.