Multiple PNP Current Sources; IC3 and IC4 Are Matched To

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Notes for Lab 1 (Bipolar (Junction) Transistor Lab)

ECE 327: Electronic Devices and Circuits Laboratory I Notes for Lab 1 (Bipolar (Junction) Transistor Lab) 1. Introduce bipolar junction transistors • “Transistor man” (from The Art of Electronics (2nd edition) by Horowitz and Hill) – Transistors are not “switches” – Base–emitter diode current sets collector–emitter resistance – Transistors are “dynamic resistors” (i.e., “transfer resistor”) – Act like closed switch in “saturation” mode – Act like open switch in “cutoff” mode – Act like current amplifier in “active” mode • Active-mode BJT model – Collector resistance is dynamically set so that collector current is β times base current – β is assumed to be very high (β ≈ 100–200 in this laboratory) – Under most conditions, base current is negligible, so collector and emitter current are equal – β ≈ hfe ≈ hFE – Good designs only depend on β being large – The active-mode model: ∗ Assumptions: · Must have vEC > 0.2 V (otherwise, in saturation) · Must have very low input impedance compared to βRE ∗ Consequences: · iB ≈ 0 · vE = vB ± 0.7 V · iC ≈ iE – Typically, use base and emitter voltages to find emitter current. Finish analysis by setting collector current equal to emitter current. • Symbols – Arrow represents base–emitter diode (i.e., emitter always has arrow) – npn transistor: Base–emitter diode is “not pointing in” – pnp transistor: Emitter–base diode “points in proudly” – See part pin-outs for easy wiring key • “Common” configurations: hold one terminal constant, vary a second, and use the third as output – common-collector ties collector -

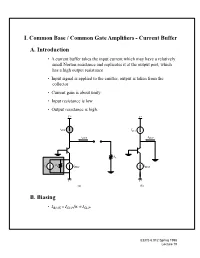

I. Common Base / Common Gate Amplifiers

I. Common Base / Common Gate Amplifiers - Current Buffer A. Introduction • A current buffer takes the input current which may have a relatively small Norton resistance and replicates it at the output port, which has a high output resistance • Input signal is applied to the emitter, output is taken from the collector • Current gain is about unity • Input resistance is low • Output resistance is high. V+ V+ i SUP ISUP iOUT IOUT RL R is S IBIAS IBIAS V− V− (a) (b) B. Biasing = /α ≈ • IBIAS ISUP ISUP EECS 6.012 Spring 1998 Lecture 19 II. Small Signal Two Port Parameters A. Common Base Current Gain Ai • Small-signal circuit; apply test current and measure the short circuit output current ib iout + = β v r gmv oib r − o ve roc it • Analysis -- see Chapter 8, pp. 507-509. • Result: –β ---------------o ≅ Ai = β – 1 1 + o • Intuition: iout = ic = (- ie- ib ) = -it - ib and ib is small EECS 6.012 Spring 1998 Lecture 19 B. Common Base Input Resistance Ri • Apply test current, with load resistor RL present at the output + v r gmv r − o roc RL + vt i − t • See pages 509-510 and note that the transconductance generator dominates which yields 1 Ri = ------ gm µ • A typical transconductance is around 4 mS, with IC = 100 A • Typical input resistance is 250 Ω -- very small, as desired for a current amplifier • Ri can be designed arbitrarily small, at the price of current (power dissipation) EECS 6.012 Spring 1998 Lecture 19 C. Common-Base Output Resistance Ro • Apply test current with source resistance of input current source in place • Note roc as is in parallel with rest of circuit g v m ro + vt it r − oc − v r RS + • Analysis is on pp. -

Precision Current Sources and Sinks Using Voltage References

Application Report SNOAA46–June 2020 Precision Current Sources and Sinks Using Voltage References Marcoo Zamora ABSTRACT Current sources and sinks are common circuits for many applications such as LED drivers and sensor biasing. Popular current references like the LM134 and REF200 are designed to make this choice easier by requiring minimal external components to cover a broad range of applications. However, sometimes the requirements of the project may demand a little more than what these devices can provide or set constraints that make them inconvenient to implement. For these cases, with a voltage reference like the TL431 and a few external components, one can create a simple current bias with high performance that is flexible to fit meet the application requirements. Current sources and sinks have been covered extensively in other Texas Instruments application notes such as SBOA046 and SLYC147, but this application note will cover other common current sources that haven't been previously discussed. Contents 1 Precision Voltage References.............................................................................................. 1 2 Current Sink with Voltage References .................................................................................... 2 3 Current Source with Voltage References................................................................................. 4 4 References ................................................................................................................... 6 List of Figures 1 Current -

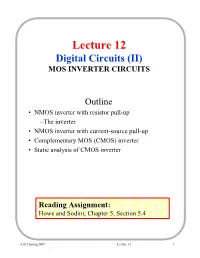

Lecture 12 Digital Circuits (II) MOS INVERTER CIRCUITS

Lecture 12 Digital Circuits (II) MOS INVERTER CIRCUITS Outline • NMOS inverter with resistor pull-up –The inverter • NMOS inverter with current-source pull-up • Complementary MOS (CMOS) inverter • Static analysis of CMOS inverter Reading Assignment: Howe and Sodini; Chapter 5, Section 5.4 6.012 Spring 2007 Lecture 12 1 1. NMOS inverter with resistor pull-up: Dynamics •CL pull-down limited by current through transistor – [shall study this issue in detail with CMOS] •CL pull-up limited by resistor (tPLH ≈ RCL) • Pull-up slowest VDD VDD R R VOUT: VOUT: HI LO LO HI V : VIN: IN C LO HI CL HI LO L pull-down pull-up 6.012 Spring 2007 Lecture 12 2 1. NMOS inverter with resistor pull-up: Inverter design issues Noise margins ↑⇒|Av| ↑⇒ •R ↑⇒|RCL| ↑⇒ slow switching •gm ↑⇒|W| ↑⇒ big transistor – (slow switching at input) Trade-off between speed and noise margin. During pull-up we need: • High current for fast switching • But also high incremental resistance for high noise margin. ⇒ use current source as pull-up 6.012 Spring 2007 Lecture 12 3 2. NMOS inverter with current-source pull-up I—V characteristics of current source: iSUP + 1 ISUP r i oc vSUP SUP _ vSUP Equivalent circuit models : iSUP + ISUP r r vSUP oc oc _ large-signal model small-signal model • High current throughout voltage range vSUP > 0 •iSUP = 0 for vSUP ≤ 0 •iSUP = ISUP + vSUP/ roc for vSUP > 0 • High small-signal resistance roc. 6.012 Spring 2007 Lecture 12 4 NMOS inverter with current-source pull-up Static Characteristics VDD iSUP VOUT VIN CL Inverter characteristics : iD = V 4 3 VIN VGS I + DD SUP roc 2 1 = vOUT vDS VDD (a) VOUT 1 2 3 4 VIN (b) High roc ⇒ high noise margins 6.012 Spring 2007 Lecture 12 5 PMOS as current-source pull-up I—V characteristics of PMOS: + S + VSG _ VSD G B − _ + IDp 5 V + D − V + G − V − D − ID(VSG,VSD) (a) = VSG 3.5 V 300 V = V + V = V − 1 V 250 (triode SD SG Tp SG region) V = 3 V 200 SG − IDp (µA) (saturation region) 150 = VSG 25 100 = 0, 0.5, VSG 1 V (cutoff region) V = 2 V 50 SG = VSG 1.5 V 12345 VSD (V) (b) Note: enhancement-mode PMOS has VTp <0. -

A Temperature and Process Insensitive Cmos Only Reference

A TEMPERATURE AND PROCESS INSENSITIVE CMOS ONLY REFERENCE CURRENT GENERATOR A Thesis Presented to The Graduate Faculty of The University of Akron In Partial Fulfillment of the Requirements for the Degree Master of Science Shivasai Bethi December, 2014 A TEMPERATURE AND PROCESS INSENSITIVE CMOS ONLY REFERENCE CURRENT GENERATOR Shivasai Bethi Thesis Approved: Accepted: ________________________ ________________________ Advisor Department Chair Dr. Kye-shin Lee Dr. Abbas Omar ________________________ ________________________ Committee Member Dean of the College Dr. Joan E. Carletta Dr. George K. Haritos ________________________ ________________________ Committee Member Interim Dean of the Graduate School Dr. Robert Veillette Dr. Rex D. Ramsier ________________________ Date ii ABSTRACT This thesis presents the design of a temperature and process insensitive CMOS only reference current generator. The proposed reference current generator consists of a conventional CMOS Widlar current source, in which the passive resistor is replaced with a transistor resistor. The gate voltage of the transistor resistor is provided by a gate bias generator that makes the output current insensitive to temperature variation. Furthermore, to achieve a process insensitive reference current, three separate gate bias generator circuits for nominal, strong and weak corners were designed. These gate bias generators are manually selected by the control switches to minimize the current variation under different process corners. As an extension of the manual mode selector, the design of an automatic mode selector that automatically selects the optimum gate bias generators to minimize the current variation under different process corners is realized. The proposed reference current generator can be used for high temperature sensor interface applications that include amplifiers, oscillators, filters and data converters. -

Chapter 10 Differential Amplifiers

Chapter 10 Differential Amplifiers 10.1 General Considerations 10.2 Bipolar Differential Pair 10.3 MOS Differential Pair 10.4 Cascode Differential Amplifiers 10.5 Common-Mode Rejection 10.6 Differential Pair with Active Load 1 Audio Amplifier Example An audio amplifier is constructed as above that takes a rectified AC voltage as its supply and amplifies an audio signal from a microphone. CH 10 Differential Amplifiers 2 “Humming” Noise in Audio Amplifier Example However, VCC contains a ripple from rectification that leaks to the output and is perceived as a “humming” noise by the user. CH 10 Differential Amplifiers 3 Supply Ripple Rejection vX Avvin vr vY vr vX vY Avvin Since both node X and Y contain the same ripple, their difference will be free of ripple. CH 10 Differential Amplifiers 4 Ripple-Free Differential Output Since the signal is taken as a difference between two nodes, an amplifier that senses differential signals is needed. CH 10 Differential Amplifiers 5 Common Inputs to Differential Amplifier vX Avvin vr vY Avvin vr vX vY 0 Signals cannot be applied in phase to the inputs of a differential amplifier, since the outputs will also be in phase, producing zero differential output. CH 10 Differential Amplifiers 6 Differential Inputs to Differential Amplifier vX Avvin vr vY Avvin vr vX vY 2Avvin When the inputs are applied differentially, the outputs are 180° out of phase; enhancing each other when sensed differentially. CH 10 Differential Amplifiers 7 Differential Signals A pair of differential signals can be generated, among other ways, by a transformer. -

Transistor Current Source

PY 452 Advanced Physics Laboratory Hans Hallen Electronics Labs One electronics project should be completed. If you do not know what an op-amp is, do either lab 2 or lab 3. A written report is due, and should include a discussion of the circuit with inserted equations and plots as appropriate to substantiate the words and show that the measurements were taken. The report should not consist of the numbered items below and short answers, but should be one coherent discussion that addresses most of the issues brought out in the numbered items below. This is not an electronics course. Familiarity with electronics concepts such as input and output impedance, noise sources and where they matter, etc. are important in the lab AND SHOULD APPEAR IN THE REPORT. The objective of this exercise is to gain familiarity with these concepts. Electronics Lab #1 Transistor Current Source Task: Build and test a transistor current source, , +V with your choice of current (but don't exceed the transistor, power supply, or R ratings). R1 Rload You may wish to try more than one current. (1) Explain your choice of R1, R2, and Rsense. VCE (a) In particular, use the 0.6 V drop of VBE - rule for current flow to calculate I in R2 VBE Rsense terms of Rsense, and the Ic/Ib rule to estimate Ib hence the values of R1&R2. (2) Try your source over a wide range of Rload values, plot Iload vs. Rload and interpret. You may find it instructive to look at VBE and VCE with a floating (neither side grounded) multimeter. -

Current Source & Source Transformation Notes

EE301 – CURRENT SOURCES / SOURCE CONVERSION Learning Objectives a. Analyze a circuit consisting of a current source, voltage source and resistors b. Convert a current source and a resister into an equivalent circuit consisting of a voltage source and a resistor c. Evaluate a circuit that contains several current sources in parallel Ideal sources An ideal source is an active element that provides a specified voltage or current that is completely independent of other circuit elements. DC Voltage DC Current Source Source Constant Current Sources The voltage across the current source (Vs) is dependent on how other components are connected to it. Additionally, the current source voltage polarity does not have to follow the current source’s arrow! 1 Example: Determine VS in the circuit shown below. Solution: 2 Example: Determine VS in the circuit shown above, but with R2 replaced by a 6 k resistor. Solution: 1 8/31/2016 EE301 – CURRENT SOURCES / SOURCE CONVERSION 3 Example: Determine I1 and I2 in the circuit shown below. Solution: 4 Example: Determine I1 and VS in the circuit shown below. Solution: Practical voltage sources A real or practical source supplies its rated voltage when its terminals are not connected to a load (open- circuited) but its voltage drops off as the current it supplies increases. We can model a practical voltage source using an ideal source Vs in series with an internal resistance Rs. Practical current source A practical current source supplies its rated current when its terminals are short-circuited but its current drops off as the load resistance increases. We can model a practical current source using an ideal current source in parallel with an internal resistance Rs. -

A Low Voltage Very High Impedance Current Mirror Circuit and Its Application

ISSN(Online): 2319-8753 ISSN (Print): 2347-6710 International Journal of Innovative Research in Science, Engineering and Technology (A High Impact Factor, Monthly, Peer Reviewed Journal) Visit: www.ijirset.com Vol. 8, Issue 2, February 2019 A Low Voltage Very High Impedance Current Mirror Circuit and Its Application Priya M.K.1, V.K.Vanitha Rugmoni2 M.Tech Scholar, Dept. of ECE, VJCET, Kerala, India1 Asst. Professor, Dept. of ECE, VJCET, Kerala, India2 ABSTRACT: Current mirror circuit has served as the basicbuilding block in analog circuit design since the introduction of integrated circuits. In this paper, “A Very high impedance current mirror, operating in reduced power supply which does not use any additional biasing circuit and its application” is proposed. The design uses a high swing super Wilson current mirror which has negative feedback. A feedback action is used to force the input and output currents to be equal. The output current is expected to be mirrored with a transfer error less than 1% when the input current is increased from 5μA to 40μ A. As an application, the current mirror circuit has been used in the design of a high gain, improved output swing differential amplifier. A telescopic differential amplifier is chosen for designing since it is used in low power application. A comparative study of different current mirror circuits and amplifier is also made. The output swing of the circuit is improved than what is expected. KEYWORDS: Current mirror, Wilson current mirror, Output Impedance, CMRR,Telescopic Differential Amplifier I. INTRODUCTION In the early 1980s many experts predicted the demise of analog circuits. -

Experiment 2: Discrete BJT Op-Amps (Part I)

EE 140 ANALOG INTEGRATED CIRCUITS SPRING 2011 C. Nguyen Experiment 2: Discrete BJT Op-Amps (Part I) This is a three-week laboratory. You are required to write only one lab report for all parts of this experiment. 1.0. INTRODUCTION In this lab, we will introduce and study the properties of a few circuit blocks commonly used to build operational amplifiers. Because we are limited to using discrete components, we will not be able to construct a complete op-amp. This will be done in the op-amp design project later in the semester. In this lab, however, we will ask you to analyze and design circuits commonly used to make integrated circuit operational amplifiers, and you will use these circuits to build a differential amplifier with both resistive and current mirror biasing. Although built with discrete devices, this op-amp uses a classical topology common to most commercial op- amps including the well-known 741. The operation of these circuits will depend on the use of matched transistors. The CA3083 is a matched NPN transistor array built on a single integrated substrate. To ensure that the transistors are properly isolated, you must connect pin 5 of the array to the most negative point of the circuit (-6 volts). Data sheets for the CA3083, and discrete npn and pnp transistors needed in this lab are attached. In this lab more than any other so far, neatness counts. Unless you build your circuits neatly, they will not operate. Trim your resistor leads if necessary. Make sure that you record all the measurements that you make as you proceed, and include these measurements in your lab report. -

B.Tech. Biomedical Engineering

RAMA UNIVERSITY UTTAR PRADESH Faculty of Engineering & Technology SYLLABUS & EVALUATION SCHEME [Effective from the Session 2014-15] B.Tech. Biomedical Engineering 2nd, 3rd&4th Year RAMA UNIVERSITY UTTAR PRADESH, KANPUR A meeting of the Board of Studies of the department of B.Tech Biomedical Engineering of Faculty of Engineering and Technology Rama University Uttar Pradesh, Kanpur was held on 5th July 2014 at 11 AM. The following members were present: 1. …………………………………. Convener 2. …………………………………. Member 3. …………………………………. Member 4. ……………………………… External Member 5. ……………………………… External Member The quorum of the meeting was complete. Agenda of the meeting: 1. Assessment Criteria 2. Question Paper Format 3. Syllabus The meeting resolved unanimously that attached Assessment Criteria, Question Paper Format and Syllabus are justified and approved. Convener Signature: ……………………… Name : ……………………….. Date: Internal Members Signature: 1…………………………………. 2……………………………………… Name: Date: External Members Signature: 1……………………………………… 2………………………………………… Name: Date: Rama University Uttar Pradesh, Kanpur Course Detail and Evaluation Scheme (Effective from the Session 2014-15) B. Tech. Biomedical Engineering Year-2 SEMESTER-III EVALUATION Subject Period S.N. Subject Name SCHEME Total Credit Code L T P CE MTE ETE Theory Subjects 1 BAS-301 Mathematics III 3 1 0 20 20 60 100 4 2 BEC-305 Fundamentals of Electronics Devices 3 1 0 20 20 60 100 4 3 BEC-302 Digital Electronics 3 1 0 20 20 60 100 4 4 BEC-306 Electromagnetic Field Theory 3 1 0 20 20 60 100 4 5 BEC-307 Fundamentals of Network Analysis & Synthesis 3 1 0 20 20 60 100 4 Practicals / Project 6 BEC-351 Electronics Engineering Lab I 0 0 2 30 20 50 100 1 7 BEC-352 Digital Electronics Lab-I 0 0 3 30 20 50 100 1 8 BEC-355 PCB & Electronics Workshop 0 0 2 30 20 50 100 1 9 Total 15 5 7 190 160 450 800 23 L-Lecture, T-Tutorial, P- Practical, CE- Continuous Evaluation, MTE-Mid Term Examination, ETE-End Term Examination Evaluation Scheme: Course without practical components For Continuous Evaluation (CE) is such as: 20 Marks 1. -

Current Mirrors

Current mirrors Current mirrors are important blocks in electronics. They are widely used in several applications and chips, the operational amplifier being one of them. Current mirrors consist of two branches that are parallel to each other and create two approximately equal currents. This is why these circuits are called current mirrors. These currents are used to load other stages in circuits and they are designed in such a way so that current is constant and independent of loading. Current mirrors come in different varieties: Simple current mirror (BJT and MOSFET) Base current corrected simple current mirror Widlar current source Wilson current mirror (BJT and MOSFET) Cascoded current mirror (BJT and MOSFET) For best performance, transistors should be matched, temperature should be the same for all devices and collector-base/drain-gate voltages should also be matched. This will provide equal currents on both sides of the current mirror. All of the circuits have a compliance voltage which is the minimum output voltage required to maintain correct circuit operation: the BJT should be in the active/linear region and the MOSFET should be in the active/saturation region. 1 www.ice77.net Simple current mirror Two implementations exist for the simple current mirror: BJT and MOSFET. BJT The BJT implementation of the simple current mirror is used as a block in the operational amplifier. VCC Vo 3.600V 1.472mA R1 VCC Vo IREF Io I 2k 3.600V 650.0mV V1 V2 Q1 3.6Vdc 0.65Vdc 1.425mA Q2 1.425mA 1.425mA 1.472mA 0V 23.47uA 0V I 23.47uA 655.3mV