USE of FIELD PROGRAMMABLE GATE ARRAY TECHNOLOGY in FUTURE: SPACE AVIONICS Rosc~Ec

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Monolithic Integration of a Novel Microfluidic Device with Silicon Light Emitting Diode-Antifuse and Photodetector

ESSDERC 2002 Monolithic Integration of a Novel Microfluidic Device with Silicon Light Emitting Diode-Antifuse and Photodetector P. LeMinh, J. Holleman, J.W.Berenschot,N.R.Tas,A.vandenBerg MESA+ Research Institute, University of Twente, the Netherlands E-mail [email protected] Abstract developing an CMOS compatible etching recipe using Tetra Methyl Ammonium Hydroxide (TMAH). Light emitting diode antifuse has been integrated into In the next sections of the paper, fabrication process, a microfluidic device that is realized with extended some critical technological design parameters, electrical standard CMOS technological steps. The device and optical properties, few results on first applications comprises of a microchannel sandwiched between a will be described respectively. photodiode detector and a nanometer-scale diode antifuse light emitter. Within this contribution, the 2. Device realization device fabrication process, working principle and properties will be discussed. Change in the interference The realization of the device (figure 1) is a 10-mask fringe of the antifuse spectra has been measured due to process. The starting material is a 3-in silicon n-type the filling of the channel. Preliminary applications are wafer with standard doping. First of all, junction electroosmotic flow speed measurement, detection of photodiode areas were fabricated by implantation of absorptivity of liquids in the channel… boron. So as not to make any step height difference at the junction between n-type and p-type region, thick resist 1. Introduction was used as masking layer for the implantation. This is important to the evenness of the channel. The shape of Silicon is well-known as an electronic and mechanical the channel was then produced by shaping a layer of material but hardly ever used as an active optoelectronic 500nm thick LPCVD polysilicon deposited on top of the element, due to its inefficient radiative recombination first silicon rich nitride (SiRN) layer. -

GS40 0.11-Μm CMOS Standard Cell/Gate Array

GS40 0.11-µm CMOS Standard Cell/Gate Array Version 1.0 January 29, 2001 Copyright Texas Instruments Incorporated, 2001 The information and/or drawings set forth in this document and all rights in and to inventions disclosed herein and patents which might be granted thereon disclosing or employing the materials, methods, techniques, or apparatus described herein are the exclusive property of Texas Instruments. No disclosure of information or drawings shall be made to any other person or organization without the prior consent of Texas Instruments. IMPORTANT NOTICE Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability. TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI’s standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this war- ranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements. Certain applications using semiconductor products may involve potential risks of death, personal injury, or severe property or environmental damage (“Critical Applications”). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WAR- RANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. -

Metadefender Core V4.12.2

MetaDefender Core v4.12.2 © 2018 OPSWAT, Inc. All rights reserved. OPSWAT®, MetadefenderTM and the OPSWAT logo are trademarks of OPSWAT, Inc. All other trademarks, trade names, service marks, service names, and images mentioned and/or used herein belong to their respective owners. Table of Contents About This Guide 13 Key Features of Metadefender Core 14 1. Quick Start with Metadefender Core 15 1.1. Installation 15 Operating system invariant initial steps 15 Basic setup 16 1.1.1. Configuration wizard 16 1.2. License Activation 21 1.3. Scan Files with Metadefender Core 21 2. Installing or Upgrading Metadefender Core 22 2.1. Recommended System Requirements 22 System Requirements For Server 22 Browser Requirements for the Metadefender Core Management Console 24 2.2. Installing Metadefender 25 Installation 25 Installation notes 25 2.2.1. Installing Metadefender Core using command line 26 2.2.2. Installing Metadefender Core using the Install Wizard 27 2.3. Upgrading MetaDefender Core 27 Upgrading from MetaDefender Core 3.x 27 Upgrading from MetaDefender Core 4.x 28 2.4. Metadefender Core Licensing 28 2.4.1. Activating Metadefender Licenses 28 2.4.2. Checking Your Metadefender Core License 35 2.5. Performance and Load Estimation 36 What to know before reading the results: Some factors that affect performance 36 How test results are calculated 37 Test Reports 37 Performance Report - Multi-Scanning On Linux 37 Performance Report - Multi-Scanning On Windows 41 2.6. Special installation options 46 Use RAMDISK for the tempdirectory 46 3. Configuring Metadefender Core 50 3.1. Management Console 50 3.2. -

PPBI for OTP Fpgas Final Report

ESA UNCLASSIFIED – For Official Use estec European Space Research and Technology Centre Keplerlaan 1 2201 AZ Noordwijk The Netherlands Tel. (31) 71 5656565 Fax (31) 71 5656040 www.esa.int PPBI for OTP FPGAs Final Report Prepared by: Ken Hernan Reference: ESCC WG 01/13 Issue: 1 Revision: 9 Date of Issue: 23rd May 2014 Status: Final Document Type: WG Report ESA UNCLASSIFIED – For Official Use ESA UNCLASSIFIED – For Official Use Table of contents: 1 INTRODUCTION ...................................................................................................................................................... 5 1.1 SCOPE OF THE DOCUMENT ..................................................................................................................................... 5 1.2 APPLICABLE AND REFERENCE DOCUMENTS ........................................................................................................... 5 1.2.1 Reference Documents (RDs) .......................................................................................................................... 5 1.3 ACRONYMS AND ABBREVIATIONS .......................................................................................................................... 6 2 EXECUTIVE SUMMARY ........................................................................................................................................ 9 3 WOKRING GROUP ACTIVITIES ........................................................................................................................ 15 4 BACKGROUND -

Semiconductor Devices

H01L CPC COOPERATIVE PATENT CLASSIFICATION H ELECTRICITY (NOTE omitted) H01 BASIC ELECTRIC ELEMENTS (NOTES omitted) H01L SEMICONDUCTOR DEVICES; ELECTRIC SOLID STATE DEVICES NOT OTHERWISE PROVIDED FOR (use of semiconductor devices for measuring G01; resistors in general H01C; magnets, inductors, transformers H01F; capacitors in general H01G; electrolytic devices H01G 9/00; batteries, accumulators H01M; waveguides, resonators, or lines of the waveguide type H01P; line connectors, current collectors H01R; stimulated-emission devices H01S; electromechanical resonators H03H; loudspeakers, microphones, gramophone pick-ups or like acoustic electromechanical transducers H04R; electric light sources in general H05B; printed circuits, hybrid circuits, casings or constructional details of electrical apparatus, manufacture of assemblages of electrical components H05K; use of semiconductor devices in circuits having a particular application, see the subclass for the application) NOTES 1. This subclass covers: • electric solid state devices which are not covered by any other subclass and details thereof, and includes: semiconductor devices adapted for rectifying, amplifying, oscillating or switching; semiconductor devices sensitive to radiation; electric solid state devices using thermoelectric, superconductive, piezo-electric, electrostrictive, magnetostrictive, galvano- magnetic or bulk negative resistance effects and integrated circuit devices; • photoresistors, magnetic field dependent resistors, field effect resistors, capacitors with potential-jump -

Introduction to ASIC Design

’14EC770 : ASIC DESIGN’ An Introduction Application - Specific Integrated Circuit Dr.K.Kalyani AP, ECE, TCE. 1 VLSI COMPANIES IN INDIA • Motorola India – IC design center • Texas Instruments – IC design center in Bangalore • VLSI India – ASIC design and FPGA services • VLSI Software – Design of electronic design automation tools • Microchip Technology – Offers VLSI CMOS semiconductor components for embedded systems • Delsoft – Electronic design automation, digital video technology and VLSI design services • Horizon Semiconductors – ASIC, VLSI and IC design training • Bit Mapper – Design, development & training • Calorex Institute of Technology – Courses in VLSI chip design, DSP and Verilog HDL • ControlNet India – VLSI design, network monitoring products and services • E Infochips – ASIC chip design, embedded systems and software development • EDAIndia – Resource on VLSI design centres and tutorials • Cypress Semiconductor – US semiconductor major Cypress has set up a VLSI development center in Bangalore • VDAT 2000 – Info on VLSI design and test workshops 2 VLSI COMPANIES IN INDIA • Sandeepani – VLSI design training courses • Sanyo LSI Technology – Semiconductor design centre of Sanyo Electronics • Semiconductor Complex – Manufacturer of microelectronics equipment like VLSIs & VLSI based systems & sub systems • Sequence Design – Provider of electronic design automation tools • Trident Techlabs – Power systems analysis software and electrical machine design services • VEDA IIT – Offers courses & training in VLSI design & development • Zensonet Technologies – VLSI IC design firm eg3.com – Useful links for the design engineer • Analog Devices India Product Development Center – Designs DSPs in Bangalore • CG-CoreEl Programmable Solutions – Design services in telecommunications, networking and DSP 3 Physical Design, CAD Tools. • SiCore Systems Pvt. Ltd. 161, Greams Road, ... • Silicon Automation Systems (India) Pvt. Ltd. ( SASI) ... • Tata Elxsi Ltd. -

Recent Advancement in the Memristor Memory Development Ravikumar K

International Journal of Innovative Technology and Exploring Engineering (IJITEE) ISSN: 2278-3075, Volume-9 Issue-7, May 2020 Recent Advancement in the Memristor Memory Development Ravikumar K. I, Sukumar R voltages as referred to in [19]) and d) manufacturing methods Abstract: Meritor is a newly-created tool and because of its compliant with CMOS relative to other NVM systems. nanometer scale and different electrical properties it has received Relative to other MRM (Resistive random access memory) much interest from advanced electronics designers since it was there are specific advantages. The RRAM is combined with discovered. The memory capacity of a memrist is one of the most significant features. In this paper, about 50 papers on designing the SRAM cell in past works such as [20–23], but each of memristor, optimization rules for reducing power, area for configuration either contributes to substantial deterioration of storing the data into memristor and implemented the full adders the fundamental SRAM reading process or absorbs a huge using memristor using the Pspice simulator. The paper ultimately amount of energy for the storage / restoration of data to / from addresses the complex study lapses and obstacles in constructing RRAM as described further in depth in section 4. In our paper the memorial that will enable scholars and thinkers lead to more analysis. we give a new NV-SRAM 8T1R that is similar to a standard Keywords: memristor, optimization. SRAM 6 T device with reading power, delay and noise tolerance. In turn, since only one RRAM cell is required for I. INTRODUCTION the off-time storage of SRAM data, energy used for processing RRAM data is reduced by more than 60% relative The resistive memory of the Crossbar has recently gained to the lowest energy density of previous RRAM NV-SRAM tremendous publicity owing to its amazing high density and designs. -

Linuxvilag-66.Pdf 8791KB 11 2012-05-28 10:27:18

Magazin Hírek Java telefon másképp Huszonegyedik századi autótolvajok Samsung okostelefon Linuxszal Magyarországon még nem jellemzõ, Kínában már kapható de tõlünk nyugatabbra már nem tol- a Samsung SCH-i819 mo- vajkulccsal vagy feszítõvassal, hanem biltelefonja, amely Prizm laptoppal járnak az autótolvajok. 2.5-ös Linuxot futtat. Ot- Mindezt azt teszi lehetõvé, hogy tani nyaralás esetén nyu- a gyújtás, a riasztó és az ajtózárak is godtan vásárolhatunk távirányíthatóak, így egy megfelelõen belõle, hiszen a CDMA felszerelt laptoppal is irányíthatóak 800 MHz-e mellett az ezek a rendszerek. európai 900/1800 MHz-et http://www.leftlanenews.com/2006/ is támogatja. A kommunikációt egy 05/03/gone-in-20-minutes-using- Qualcomm MSM6300-as áramkör bo- laptops-to-steal-cars/ nyolítja, míg az alkalmazások egy 416 MHz-es Intel PXA270-es processzoron A Lucent Technologies és a SUN Elephants Dream futnak. A készülék Class 10-es GPRS elkészítette a Jasper S20-at, ami adatátvitelre képes, illetve tartalmaz alapvetõen más koncepcióval GPS (globális helymeghatározó) vevõt © Kiskapu Kft. Minden jog fenntartva használja a Java-t, mint a mostani is. Az eszköz 64 megabájt SDRAM-ot és telefonok. Joggal kérdezheti a kedves 128 megabájt nem felejtõ flash memóri- Olvasó, hogy megéri-e, van-e hely át kapott, de micro-SD memóriakártyá- a jelenlegi Symbian, Windows Mobile val ezt tovább bõvíthetjük. A kijelzõje és Linux trió mellett. A jelenlegi 2.4 hüvelykes, felbontása pedig „csak” telefonoknál kétféleképpen futhat 240x320 képpont 65 ezer színnel. egy program: natív vagy Java mód- Május 19-én elérhetõvé tette az Orange Természetesen a trendeknek megfele- ban. A Java mód ott szükségessé Open Movie Project elsõ rövidfilmjét lõen nem maradt ki a 2 megapixeles tesz pár olyan szintet, amely Creative Commons jogállással. -

ECE 274 - Digital Logic Lecture 22 Full-Custom Integrated Circuit

ECE 274 - Digital Logic Lecture 22 Full-Custom Integrated Circuit Full-Custom Integrated Circuit Chip created specifically to implement the transistors of the desired chip Lecture 22 – Implementation Layout – detailed description how each transistor and wires should be Manufactured IC Technologies layed on a chips surface Typically use CAD tools to convert our circuit design to a custom layout Fabricating an IC is often referred to a silicon spin 1 2 Semicustom (Application Specific) Integrated Full-Custom Integrated Circuit Circuits - ASICs Full-Custom Integrated Circuit Gate Arrays Pros Utilize a chip whose transistors are pre-designed to forms rows (arrays) of logic gates on the chip Maximum performance Sometimes referred to as sea-of-gates Cons Pros High NRE (Non-Recurring Engineering) cost Much cheaper than full-custom IC Cost of setting of the fabrication of an IC Fabrications time is typically several weeks Often exceeds $1 million Cons May take months before first IC is available Less optimized compared to full-custom IC - Slower performance, bigger size, and more power consumption 3 4 Semicustom (Application Specific) Integrated Semicustom (Application Specific) Integrated Circuits - ASICs Circuits - ASICs Standard Cells Cell Array Utilize library of pre-layed-out gates and smaller pieces of logic (cells) Standard cells are replaced on the IC with only the wiring left to be that a designer must instantiate and connect with wires completed Pros Sometimes referred to as sea of cells Can be better optimized -

Reliability of the Amorphous Silicon Antifuse

Reliability of the Amorphous Silicon Antifuse • • • • • • QuickLogic® White Paper Abstract Development processes at QuickLogic control the reliability of the QuickLogic ViaLink® antifuse. ViaLink reliability is built into the silicon at every step, beginning with design rules and device characterization. But unlike other fab processes, the reliability work continues with the layout rules, test methodology, place and route software, ViaLink programming sequence, programming algorithm, qualification plans, and quality assurance process. All these factors come together to create the reliable QuickLogic ViaLink. Introduction Semiconductor reliability has been studied and characterized [1]. The initial failure rate, also called infant mortality, is high due to defects. The midterm life of a semiconductor component has a low failure rate. Most of the defects have already failed, and the wear out failure for mechanisms has not started. At the end of the semiconductor component life, many elements of the semiconductor begin to wear out. Physical changes to the metals, semiconductor, and dielectrics cause the component to no longer meet the original specification. These failures are predictable and increase with time. This high-low-high failure rate is known as the bathtub curve and is shown in Figure 1. Figure 1: Bathtub curve for semiconductor failure rate. Semiconductor manufacturers have reduced the infant mortality by decreasing the number of defects and screening for the remaining defects. Defects have been reduced with improved and automated wafer handling, improved equipment and improved processes. Automatic inspections have been added during wafer fabrication for the purpose of detecting wafers with defects. Wafers that cannot be reworked are scrapped. After fabrication, wafers are tested for correct electrical parameters. -

Lewis University Dr. James Girard Summer Undergraduate Research Program 2021 Faculty Mentor - Project Application

Lewis University Dr. James Girard Summer Undergraduate Research Program 2021 Faculty Mentor - Project Application Exploring the Use of High-level Parallel Abstractions and Parallel Computing for Functional and Gate-Level Simulation Acceleration Dr. Lucien Ngalamou Department of Engineering, Computing and Mathematical Sciences Abstract System-on-Chip (SoC) complexity growth has multiplied non-stop, and time-to- market pressure has driven demand for innovation in simulation performance. Logic simulation is the primary method to verify the correctness of such systems. Logic simulation is used heavily to verify the functional correctness of a design for a broad range of abstraction levels. In mainstream industry verification methodologies, typical setups coordinate the validation e↵ort of a complex digital system by distributing logic simulation tasks among vast server farms for months at a time. Yet, the performance of logic simulation is not sufficient to satisfy the demand, leading to incomplete validation processes, escaped functional bugs, and continuous pressure on the EDA1 industry to develop faster simulation solutions. In this research, we will explore a solution that uses high-level parallel abstractions and parallel computing to boost the performance of logic simulation. 1Electronic Design Automation 1 1 Project Description 1.1 Introduction and Background SoC complexity is increasing rapidly, driven by demands in the mobile market, and in- creasingly by the fast-growth of assisted- and autonomous-driving applications. SoC teams utilize many verification technologies to address their complexity and time-to-market chal- lenges; however, logic simulation continues to be the foundation for all verification flows, and continues to account for more than 90% [10] of all verification workloads. -

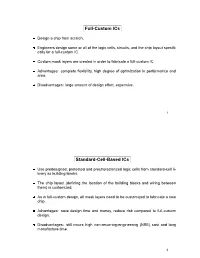

Full-Custom Ics Standard-Cell-Based

Full-Custom ICs Design a chip from scratch. Engineers design some or all of the logic cells, circuits, and the chip layout specifi- cally for a full-custom IC. Custom mask layers are created in order to fabricate a full-custom IC. Advantages: complete flexibility, high degree of optimization in performance and area. Disadvantages: large amount of design effort, expensive. 1 Standard-Cell-Based ICs Use predesigned, pretested and precharacterized logic cells from standard-cell li- brary as building blocks. The chip layout (defining the location of the building blocks and wiring between them) is customized. As in full-custom design, all mask layers need to be customized to fabricate a new chip. Advantages: save design time and money, reduce risk compared to full-custom design. Disadvantages: still incurs high non-recurring-engineering (NRE) cost and long manufacture time. 2 D A B C A B B D C D A A B B Cell A Cell B Cell C Cell D Feedthrough Cell Standard-cell-based IC design. 3 Gate-Array Parts of the chip are pre-fabricated, and other parts are custom fabricated for a particular customer’s circuit. Idential base cells are pre-fabricated in the form of a 2-D array on a gate-array (this partially finished chip is called gate-array template). The wires between the transistors inside the cells and between the cells are custom fabricated for each customer. Custom masks are made for the wiring only. Advantages: cost saving (fabrication cost of a large number of identical template wafers is amortized over different customers), shorter manufacture lead time.