Mobile 3Rd Generation Intel® Core™ Processor Family, Mobile Intel® Pentium® Processor Family, and Mobile Intel® Celeron® Processor Family

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Release Notes for X11R6.8.2 the X.Orgfoundation the Xfree86 Project, Inc

Release Notes for X11R6.8.2 The X.OrgFoundation The XFree86 Project, Inc. 9February 2005 Abstract These release notes contains information about features and their status in the X.Org Foundation X11R6.8.2 release. It is based on the XFree86 4.4RC2 RELNOTES docu- ment published by The XFree86™ Project, Inc. Thereare significant updates and dif- ferences in the X.Orgrelease as noted below. 1. Introduction to the X11R6.8.2 Release The release numbering is based on the original MIT X numbering system. X11refers to the ver- sion of the network protocol that the X Window system is based on: Version 11was first released in 1988 and has been stable for 15 years, with only upwardcompatible additions to the coreX protocol, a recordofstability envied in computing. Formal releases of X started with X version 9 from MIT;the first commercial X products werebased on X version 10. The MIT X Consortium and its successors, the X Consortium, the Open Group X Project Team, and the X.OrgGroup released versions X11R3 through X11R6.6, beforethe founding of the X.OrgFoundation. Therewill be futuremaintenance releases in the X11R6.8.x series. However,efforts arewell underway to split the X distribution into its modular components to allow for easier maintenance and independent updates. We expect a transitional period while both X11R6.8 releases arebeing fielded and the modular release completed and deployed while both will be available as different consumers of X technology have different constraints on deployment. Wehave not yet decided how the modular X releases will be numbered. We encourage you to submit bug fixes and enhancements to bugzilla.freedesktop.orgusing the xorgproduct, and discussions on this server take place on <[email protected]>. -

Download/Face- Modules/Documents/Face-Modules-Hw-Specifications.Pdf

I PC H “ CompuLab Ltd. Revision 1.2 December 2013 Legal Notice © 2013 CompuLab Ltd. All Rights Reserved. No part of this document may be photocopied, reproduced, stored in a retrieval system, or transmitted, in any form or by any means whether, electronic, mechanical, or otherwise without the prior written permission of CompuLab Ltd. No warranty of accuracy is given concerning the contents of the information contained in this publication. To the extent permitted by law no liability (including liability to any person by reason of negligence) will be accepted by CompuLab Ltd., its subsidiaries or employees for any direct or indirect loss or damage caused by omissions from or inaccuracies in this document. CompuLab Ltd. reserves the right to change details in this publication without notice. Product and company names herein may be the trademarks of their respective owners. CompuLab Ltd. 17 HaYetsira St., Yokneam Elite 20692, P.O.B 687 ISRAEL Tel: +972-4-8290100 http://www.compulab.co.il http://fit-pc.com/web/ Fax: +972-4-8325251 CompuLab Ltd. Intense PC Hardware Specification Page 2 of 74 Revision History Revision Engineer Revision Changes 1.0 Maxim Birger Initial public release 1.1 Maxim Birger Memory Interface updated Super-IO Controller peripheral section added RS232 serial com port info added 1.2 Maxim Birger HDMI Block Diagram updated DP Block Diagram updated CompuLab Ltd. Intense PC Hardware Specification Page 3 of 74 Table of Contents Legal Notice .................................................................................................................................................. -

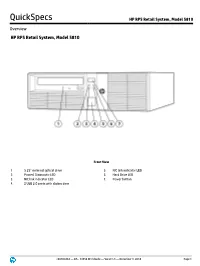

HP RP5810 Retail System, Model 5810

QuickSpecs HP RP5 Retail System, Model 5810 Overview HP RP5 Retail System, Model 5810 Front View 1. 5.25” external optical drive 5. NIC link indicator LED 2. Power/ Diagnostic LED 6. Hard Drive LED 3. NIC link indicator LED 7. Power button 4. 2 USB 2.0 ports with sliding door c04304464 — DA - 14956 Worldwide — Version 8 — December 8, 2014 Page 1 QuickSpecs HP RP5 Retail System, Model 5810 Overview Rear View 1. 24 Volt USB + PWR port 10. PS/2 keyboard port 2. Two (2) Full-Height Slots* 11. VGA port 3. RS232 serial COM3 12. 3 USB 2.0 ports 4. RJ-45 LAN jack 13. 2 USB 3.0 ports 5. RS232 serial (power configurable) COM1 port 14. RS232 serial (power configurable) COM2 port 6. PS/2 mouse port 15. DisplayPort 7. 240W EPA – Active PFC power supply (no line 16. RJ12 cash drawer port switching required) 8. Line in audio jack 17. One (1) PCIe x16 Slot (wired as x16)** – shown is optional three (3) port 12 Volt USB +Power Card 9. Line out audio jack 18. One (1) PCIe x16 Slot (wired as x4)** – shown is optional three (3) port 12 Volt USB + Power Card * Can be configured either as two (2) PCI x1 or two (2) PCIe x1 Full-Height slots. Shown is optional 2 Port RS232 serial (power configurable) Card, COM4 port (left) and COM3 port (right port). **A variety of cards are available to populate slots, dependant on riser choice and connectors utilized. For full details, please contact your HP sales representative for configuration choices. -

GPU Developments 2018

GPU Developments 2018 2018 GPU Developments 2018 © Copyright Jon Peddie Research 2019. All rights reserved. Reproduction in whole or in part is prohibited without written permission from Jon Peddie Research. This report is the property of Jon Peddie Research (JPR) and made available to a restricted number of clients only upon these terms and conditions. Agreement not to copy or disclose. This report and all future reports or other materials provided by JPR pursuant to this subscription (collectively, “Reports”) are protected by: (i) federal copyright, pursuant to the Copyright Act of 1976; and (ii) the nondisclosure provisions set forth immediately following. License, exclusive use, and agreement not to disclose. Reports are the trade secret property exclusively of JPR and are made available to a restricted number of clients, for their exclusive use and only upon the following terms and conditions. JPR grants site-wide license to read and utilize the information in the Reports, exclusively to the initial subscriber to the Reports, its subsidiaries, divisions, and employees (collectively, “Subscriber”). The Reports shall, at all times, be treated by Subscriber as proprietary and confidential documents, for internal use only. Subscriber agrees that it will not reproduce for or share any of the material in the Reports (“Material”) with any entity or individual other than Subscriber (“Shared Third Party”) (collectively, “Share” or “Sharing”), without the advance written permission of JPR. Subscriber shall be liable for any breach of this agreement and shall be subject to cancellation of its subscription to Reports. Without limiting this liability, Subscriber shall be liable for any damages suffered by JPR as a result of any Sharing of any Material, without advance written permission of JPR. -

STATE of NEW JERSEY Department of Labor and Workforce Development Division of Wage and Hour Compliance - Public Contracts Section PO Box 389 Trenton, NJ 08625-0389

STATE OF NEW JERSEY Department of Labor and Workforce Development Division of Wage and Hour Compliance - Public Contracts Section PO Box 389 Trenton, NJ 08625-0389 PREVAILING WAGE RATE DETERMINATION The New Jersey Prevailing Wage Act (N.J.S.A. 34:11-56.25 et seq.) requires that the Department of Labor and Workforce Development establish and enforce a prevailing wage level for workers engaged in public works in order to safeguard their efficiency and general well being and to protect them as well as their employers from the effects of serious and unfair competition. Prevailing wage rates are wage and fringe benefit rates based on the collective bargaining agreements established for a particular craft or trade in the locality in which the public work is performed. In New Jersey, these rates vary by county and by the type of work performed. Applicable prevailing wage rates are those wages and fringe benefits in effect on the date the contract is awarded. All pre-determined rate increases listed at the time the contract is awarded must also be paid, beginning on the dates specified. Rates that have expired will remain in effect until new rates are posted. Prevailing Wage Rate The prevailing wage rate for each craft will list the effective date of the rate and the following information: W = Wage Rate per Hour B = Fringe Benefit Rate per Hour* T = Total Rate per Hour * Fringe benefits are an integral part of the prevailing wage rate. Employers not providing such benefits must pay the fringe benefit amount directly to the employee each payday. -

The Birth, Evolution and Future of Microprocessor

The Birth, Evolution and Future of Microprocessor Swetha Kogatam Computer Science Department San Jose State University San Jose, CA 95192 408-924-1000 [email protected] ABSTRACT timed sequence through the bus system to output devices such as The world's first microprocessor, the 4004, was co-developed by CRT Screens, networks, or printers. In some cases, the terms Busicom, a Japanese manufacturer of calculators, and Intel, a U.S. 'CPU' and 'microprocessor' are used interchangeably to denote the manufacturer of semiconductors. The basic architecture of 4004 same device. was developed in August 1969; a concrete plan for the 4004 The different ways in which microprocessors are categorized are: system was finalized in December 1969; and the first microprocessor was successfully developed in March 1971. a) CISC (Complex Instruction Set Computers) Microprocessors, which became the "technology to open up a new b) RISC (Reduced Instruction Set Computers) era," brought two outstanding impacts, "power of intelligence" and "power of computing". First, microprocessors opened up a new a) VLIW(Very Long Instruction Word Computers) "era of programming" through replacing with software, the b) Super scalar processors hardwired logic based on IC's of the former "era of logic". At the same time, microprocessors allowed young engineers access to "power of computing" for the creative development of personal 2. BIRTH OF THE MICROPROCESSOR computers and computer games, which in turn led to growth in the In 1970, Intel introduced the first dynamic RAM, which increased software industry, and paved the way to the development of high- IC memory by a factor of four. -

Heater Element Specifications Bulletin Number 592

Technical Data Heater Element Specifications Bulletin Number 592 Topic Page Description 2 Heater Element Selection Procedure 2 Index to Heater Element Selection Tables 5 Heater Element Selection Tables 6 Additional Resources These documents contain additional information concerning related products from Rockwell Automation. Resource Description Industrial Automation Wiring and Grounding Guidelines, publication 1770-4.1 Provides general guidelines for installing a Rockwell Automation industrial system. Product Certifications website, http://www.ab.com Provides declarations of conformity, certificates, and other certification details. You can view or download publications at http://www.rockwellautomation.com/literature/. To order paper copies of technical documentation, contact your local Allen-Bradley distributor or Rockwell Automation sales representative. For Application on Bulletin 100/500/609/1200 Line Starters Heater Element Specifications Eutectic Alloy Overload Relay Heater Elements Type J — CLASS 10 Type P — CLASS 20 (Bul. 600 ONLY) Type W — CLASS 20 Type WL — CLASS 30 Note: Heater Element Type W/WL does not currently meet the material Type W Heater Elements restrictions related to EU ROHS Description The following is for motors rated for Continuous Duty: For motors with marked service factor of not less than 1.15, or Overload Relay Class Designation motors with a marked temperature rise not over +40 °C United States Industry Standards (NEMA ICS 2 Part 4) designate an (+104 °F), apply application rules 1 through 3. Apply application overload relay by a class number indicating the maximum time in rules 2 and 3 when the temperature difference does not exceed seconds at which it will trip when carrying a current equal to 600 +10 °C (+18 °F). -

Matrox MGA-1064SG Developer Specification

Matrox Graphics Inc. Matrox MGA-1064SG Developer Specification Document Number 10524-MS-0100 February 10, 1997 Trademark Acknowledgements MGA,™ MGA-1064SG,™ MGA-1164SG,™ MGA-2064W,™ MGA-2164W,™ MGA-VC064SFB,™ MGA-VC164SFB,™ MGA Marvel,™ MGA Millennium,™ MGA Mystique,™ MGA Rainbow Run- ner,™ MGA DynaView,™ PixelTOUCH,™ MGA Control Panel,™ and Instant ModeSWITCH,™ are trademarks of Matrox Graphics Inc. Matrox® is a registered trademark of Matrox Electronic Systems Ltd. VGA,® is a registered trademark of International Business Machines Corporation; Micro Channel™ is a trademark of International Business Machines Corporation. Intel® is a registered trademark, and 386,™ 486,™ Pentium,™ and 80387™ are trademarks of Intel Corporation. Windows™ is a trademark of Microsoft Corporation; Microsoft,® and MS-DOS® are registered trade- marks of Microsoft Corporation. AutoCAD® is a registered trademark of Autodesk Inc. Unix™ is a trademark of AT&T Bell Laboratories. X-Windows™ is a trademark of the Massachusetts Institute of Technology. AMD™ is a trademark of Advanced Micro Devices. Atmel® is a registered trademark of Atmel Corpora- tion. Catalyst™ is a trademark of Catalyst Semiconductor Inc. SGS™ is a trademark of SGS-Thompson. Toshiba™ is a trademark of Toshiba Corporation. Texas Instruments™ is a trademark of Texas Instru- ments. National™ is a trademark of National Semiconductor Corporation. Microchip™ is a trademark of Microchip Technology Inc. All other nationally and internationally recognized trademarks and tradenames are hereby acknowledged. This document contains confidential proprietary information that may not be disclosed without written permission from Matrox Graphics Inc. © Copyright Matrox Graphics Inc., 1997. All rights reserved. Disclaimer: Matrox Graphics Inc. reserves the right to make changes to specifications at any time and without notice. -

Experience a Lower Total Cost of Ownership

EXPERIENCE A LOWER TOTAL COST OF OWNERSHIP Timken® Spherical Roller Bearings are engineered to give you more of what you need. Lower Operating Temperatures Rollers are guided by cage pockets—not a center guide ring—eliminating a friction point and resulting in 4–10% less rotational torque and 5ºC lower operating temperatures.* Less rotational torque leads to improved efficiency, lower energy consumption and more savings. Lower temperatures reduce the oil oxidation rate by 50% to extend lubricant life. Tougher Protection Hardened steel cages deliver greater fatigue strength, increased wear resistance and tougher protection against shock and acceleration. Optimized Uptime Unique slots in the cage face improve oil flow and purge more contaminants from the bearing to help extend equipment uptime. Minimized Wear Improved profiles reduce internal stresses and optimize load distribution to minimize wear. Improved Lube Film Enhanced surface finishes avoid metal-to-metal contact to reduce friction and result in improved lube film. Higher Loads Longer rollers result in 4–8% higher load ratings or 14–29% longer predicted bearing life. Higher load ratings enable you to carry heavier loads. Brass Cages Available in all sizes; ready when you need extra strength and durability in the most unrelenting conditions, including extreme shock and vibration, high acceleration forces, and minimal lubrication. Increase your operational efficiencies and extend maintenance intervals. Starting now. Visit Timken.com/spherical to find out more. *All results are from head-to-head -

Matrox MGA-2164W Developer's Specification

Matrox Graphics Inc. Matrox MGA-2164W Developer’s Specification Document Number 10568-XX-0100 August 18, 1997 Trademark Acknowledgements MGA,™ MGA-1064SG,™ MGA-1164SG,™ MGA-2064W,™ MGA-2164W,™ MGA-VC064SFB,™ MGA-VC164SFB,™ MGA Marvel,™ MGA Millennium,™ MGA Mystique,™ MGA Rainbow Run- ner,™ MGA DynaView,™ PixelTOUCH,™ MGA Control Panel,™ and Instant ModeSWITCH,™ are trademarks of Matrox Graphics Inc. Matrox® is a registered trademark of Matrox Electronic Systems Ltd. VGA,® is a registered trademark of International Business Machines Corporation; Micro Channel™ is a trademark of International Business Machines Corporation. Intel® is a registered trademark, and 386,™ 486,™ Pentium,™ and 80387™ are trademarks of Intel Corporation. Windows™ is a trademark of Microsoft Corporation; Microsoft,® and MS-DOS® are registered trade- marks of Microsoft Corporation. AutoCAD® is a registered trademark of Autodesk Inc. Unix™ is a trademark of AT&T Bell Laboratories. X-Windows™ is a trademark of the Massachusetts Institute of Technology. AMD™ is a trademark of Advanced Micro Devices. Atmel® is a registered trademark of Atmel Corpora- tion. Catalyst™ is a trademark of Catalyst Semiconductor Inc. SGS™ is a trademark of SGS-Thompson. Toshiba™ is a trademark of Toshiba Corporation. Texas Instruments™ is a trademark of Texas Instru- ments. National™ is a trademark of National Semiconductor Corporation. Microchip™ is a trademark of Microchip Technology Inc. All other nationally and internationally recognized trademarks and tradenames are hereby acknowledged. This document contains confidential proprietary information that may not be disclosed without written permission from Matrox Graphics Inc. © Copyright Matrox Graphics Inc., 1997. All rights reserved. Disclaimer: Matrox Graphics Inc. reserves the right to make changes to specifications at any time and without notice. -

Eagle July Wine Editable

august 2021 WINE BY THE GLASS WHITES REDS Flirty & Sparky Gls/Btl Alluring & Spicy Gls/Btl MIONETTO Prosecco (Italy) 7/28 CARICATURE Zinfandel ‘18 (Lodi, CA) *S-G 8/32 VIETTI Moscato d’Asti ‘20 (IT) Half btl 10/20 AMAVI by Pepper Bridge Syrah ‘18 (WA) 14/56 LARCHARGO Reserva Tempranillo ‘12 (SP) 9/36 Sumptously Fruity ALTOS ‘Las Hormigas’ Malbec ‘19 (ARG) 8/32 Ste. CHAPELLE Soft Huckleberry (ID) 5/20 Pinot Noir & Light-bodied Red Dr. LOOSEN Qba Riesling ‘20 (GER) 6/24 MEIOMI ‘19 (CA) 10/40 Refreshing & Satisfying PATTON VALLEY Estate ‘18 (OR) 10/40 LAVENDETTE Rose ‘20 (FR) 8/32 GULP/HABLO TINTO Red ‘19 (SP) *S-G 7/28 McMANIS Pinot Grigio ‘20 (CA) 6/24 As the name implies, this blend is delish and easy-drinking! ELK COVE Pinot Gris ‘20 (OR) 9/36 Handsome Blends Perky & Crisp PASSIONATE ‘Tinto’ Malbec blend ‘19 (AR) 9/36 MARIETTA ‘Lot 72’ Zin blend (CA) 6/24 TELAYA Viognier ‘20 (Yakima, WA) 9/36 SPLIT RAIL GSM ‘17 Rhone style (ID) By draft! 9 Gls LANZOS Sauvignon Blanc blend ‘19 (SP) *S-G 8/32 NAUTILUS Sauvignon Blanc ‘20 (NZ) *S-G 8/32 Merlot CROW CANYON ‘18 (CA) 5/20 Chardonnay DECOY by Duckhorn ‘19 (Sonoma) 12/48 LOST ANGEL ‘18 (CA) 6/24 Cabernet Sauvignon & Cab Blends LA CREMA ‘18 (Sonoma Coast, CA) 9/36 SALMON CREEK ‘17 (CA) 5/20 ROMBAUER ‘20 (Carneros, CA) 17/68 LOUIS MARTINI ‘18 (Sonoma) 9/36 SLEIGHT OF HAND ‘Spellbinder’ ‘18 (WA) 10/40 BODEGAS LANZOS Blanco 8/Gls J. -

Case I,I,Emptyset,P7.Nb

Definitions: In[56]:= $Assumptions = w12 ≥ 0 && w13 ≥ 0 && w16 ≥ 0 && w24 ≥ 0 && w25 ≥ 0 && w36 ≥ 0 && w45 ≥ 0 && u > 0 && v > 0 && w21 ≥ 0 && w31 ≥ 0 && w61 ≥ 0 && w42 ≥ 0 && w52 ≥ 0 && w63 ≥ 0 && w54 ≥ 0 && K34 > 0 && K56 > 0 && K31 > 0 && K51 > 0 w = {{0, w12, w13, 0, 0, w16}, {w21, 0, 0, w24, w25, 0}, {w31, 0, 0, u, 0, w36}, {0, w42, u / K34, 0, w45, 0}, {0, w52, 0, w54, 0, v}, {w61, 0, w63, 0, v / K56, 0}} Out[56]= w12 ≥ 0 && w13 ≥ 0 && w16 ≥ 0 && w24 ≥ 0 && w25 ≥ 0 && w36 ≥ 0 && w45 ≥ 0 && u > 0 && v > 0 && w21 ≥ 0 && w31 ≥ 0 && w61 ≥ 0 && w42 ≥ 0 && w52 ≥ 0 && w63 ≥ 0 && w54 ≥ 0 && K34 > 0 && K56 > 0 && K31 > 0 && K51 > 0 Out[57]= {0, w12, w13, 0, 0, w16}, {w21, 0, 0, w24, w25, 0}, {w31, 0, 0, u, 0, w36}, u v 0, w42, , 0, w45, 0, {0, w52, 0, w54, 0, v}, w61, 0, w63, 0, , 0 K34 K56 In[58]:= MatrixForm[w] Out[58]//MatrixForm= 0 w12 w13 0 0 w16 w21 0 0 w24 w25 0 w31 0 0 u 0 w36 0 w42 u 0 w45 0 K34 0 w52 0 w54 0 v w61 0 w63 0 v 0 K56 Sum of rows In[59]:= d = Table[Total[w[[i, All]]], {i, 6}] d34 = Collect[Expand[d[[3]] * d[[4]] - w[[3, 4]] * w[[4, 3]]], u] d56 = Collect[Expand[d[[5]] * d[[6]] - w[[5, 6]] * w[[6, 5]]], v] u v Out[59]= w12 + w13 + w16, w21 + w24 + w25, u + w31 + w36, + w42 + w45, v + w52 + w54, + w61 + w63 K34 K56 w31 w36 Out[60]= w31 w42 + w36 w42 + w31 w45 + w36 w45 + u + + w42 + w45 K34 K34 w52 w54 Out[61]= w52 w61 + w54 w61 + w52 w63 + w54 w63 + v + + w61 + w63 K56 K56 Effective reaction rates after elimination of metabolites 5 and 6 (useful for easy differentiation w.r.to u), and the final effective reaction rate