Xcell Journal Issue 46, Summer 2003

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Intel® Quick Sync Video Technology Guide

WP80 Superguide 3: THE CLOUD VIDEO SUPERGUIDE JANUARY/FEBRUARY 2015 SPONSORED CONTENT Intel® Quick Sync Video Technology and Intel® Xeon® Processor Based Servers— Flexible Transcode Performance and Quality Video transcoding involves converting provides enterprise-quality HEVC and and boost image quality. Some key one compressed video format to audio codecs, Intel® VTune™ Amplifier improvements include the following: another. In the past this process has XE performance analysis tools and Video • Additional JPEG/MJPEG decode in been a compute-intensive task which Quality Caliper stream quality analyzer. the multi-format codec engine. This demanded a large amount of precious Additionally, product family members, support is on top of existing energy- CPU resources. Intel® Quick Synch Video Intel® Video Pro Analyzer and Intel® efficient, high-performance AVC (QSV) can enable hardware-accelerated Stress Bitstreams and Encoder bundles encode/decode that sustains multiple transcoding to deliver better performance enable production–scale validation and 4K and Ultra HD video streams. than transcoding on the CPU without debug of encode, transcode, and decode • A dedicated new video quality engine sacrificing quality. and playback applications. to provide extensive video processing First introduced in 2011, Intel Quick Intel Media Server Studio SDK at low power consumption Sync technology is available in the Intel® implements many codec and tools • Programmable and media-optimized Xeon® Processor E3-1200 v3 with Intel components initially in software, and EU (execution units)/samplers for HD Graphics P4600/4700 and Iris™ Pro later as hybrid (software and hardware) high quality P5200. (From here on, we’ll simply refer to or entirely in hardware. -

Download/Face- Modules/Documents/Face-Modules-Hw-Specifications.Pdf

I PC H “ CompuLab Ltd. Revision 1.2 December 2013 Legal Notice © 2013 CompuLab Ltd. All Rights Reserved. No part of this document may be photocopied, reproduced, stored in a retrieval system, or transmitted, in any form or by any means whether, electronic, mechanical, or otherwise without the prior written permission of CompuLab Ltd. No warranty of accuracy is given concerning the contents of the information contained in this publication. To the extent permitted by law no liability (including liability to any person by reason of negligence) will be accepted by CompuLab Ltd., its subsidiaries or employees for any direct or indirect loss or damage caused by omissions from or inaccuracies in this document. CompuLab Ltd. reserves the right to change details in this publication without notice. Product and company names herein may be the trademarks of their respective owners. CompuLab Ltd. 17 HaYetsira St., Yokneam Elite 20692, P.O.B 687 ISRAEL Tel: +972-4-8290100 http://www.compulab.co.il http://fit-pc.com/web/ Fax: +972-4-8325251 CompuLab Ltd. Intense PC Hardware Specification Page 2 of 74 Revision History Revision Engineer Revision Changes 1.0 Maxim Birger Initial public release 1.1 Maxim Birger Memory Interface updated Super-IO Controller peripheral section added RS232 serial com port info added 1.2 Maxim Birger HDMI Block Diagram updated DP Block Diagram updated CompuLab Ltd. Intense PC Hardware Specification Page 3 of 74 Table of Contents Legal Notice .................................................................................................................................................. -

HP RP5810 Retail System, Model 5810

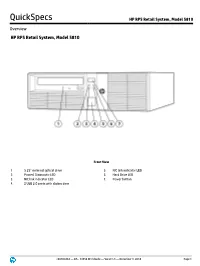

QuickSpecs HP RP5 Retail System, Model 5810 Overview HP RP5 Retail System, Model 5810 Front View 1. 5.25” external optical drive 5. NIC link indicator LED 2. Power/ Diagnostic LED 6. Hard Drive LED 3. NIC link indicator LED 7. Power button 4. 2 USB 2.0 ports with sliding door c04304464 — DA - 14956 Worldwide — Version 8 — December 8, 2014 Page 1 QuickSpecs HP RP5 Retail System, Model 5810 Overview Rear View 1. 24 Volt USB + PWR port 10. PS/2 keyboard port 2. Two (2) Full-Height Slots* 11. VGA port 3. RS232 serial COM3 12. 3 USB 2.0 ports 4. RJ-45 LAN jack 13. 2 USB 3.0 ports 5. RS232 serial (power configurable) COM1 port 14. RS232 serial (power configurable) COM2 port 6. PS/2 mouse port 15. DisplayPort 7. 240W EPA – Active PFC power supply (no line 16. RJ12 cash drawer port switching required) 8. Line in audio jack 17. One (1) PCIe x16 Slot (wired as x16)** – shown is optional three (3) port 12 Volt USB +Power Card 9. Line out audio jack 18. One (1) PCIe x16 Slot (wired as x4)** – shown is optional three (3) port 12 Volt USB + Power Card * Can be configured either as two (2) PCI x1 or two (2) PCIe x1 Full-Height slots. Shown is optional 2 Port RS232 serial (power configurable) Card, COM4 port (left) and COM3 port (right port). **A variety of cards are available to populate slots, dependant on riser choice and connectors utilized. For full details, please contact your HP sales representative for configuration choices. -

GPU Developments 2018

GPU Developments 2018 2018 GPU Developments 2018 © Copyright Jon Peddie Research 2019. All rights reserved. Reproduction in whole or in part is prohibited without written permission from Jon Peddie Research. This report is the property of Jon Peddie Research (JPR) and made available to a restricted number of clients only upon these terms and conditions. Agreement not to copy or disclose. This report and all future reports or other materials provided by JPR pursuant to this subscription (collectively, “Reports”) are protected by: (i) federal copyright, pursuant to the Copyright Act of 1976; and (ii) the nondisclosure provisions set forth immediately following. License, exclusive use, and agreement not to disclose. Reports are the trade secret property exclusively of JPR and are made available to a restricted number of clients, for their exclusive use and only upon the following terms and conditions. JPR grants site-wide license to read and utilize the information in the Reports, exclusively to the initial subscriber to the Reports, its subsidiaries, divisions, and employees (collectively, “Subscriber”). The Reports shall, at all times, be treated by Subscriber as proprietary and confidential documents, for internal use only. Subscriber agrees that it will not reproduce for or share any of the material in the Reports (“Material”) with any entity or individual other than Subscriber (“Shared Third Party”) (collectively, “Share” or “Sharing”), without the advance written permission of JPR. Subscriber shall be liable for any breach of this agreement and shall be subject to cancellation of its subscription to Reports. Without limiting this liability, Subscriber shall be liable for any damages suffered by JPR as a result of any Sharing of any Material, without advance written permission of JPR. -

CTL RFP Proposal

State of Maine Department of Education in coordination with the National Association of State Procurement Officials PROPOSAL COVER PAGE RFP # 201210412 MULTI-STATE LEARNING TECHNOLOGY INITIATIVE Bidder’s Organization Name: CTL Chief Executive - Name/Title: Erik Stromquist / COO Tel: 800.642.3087 x 212 Fax: 503.641.5586 E-mail: [email protected] Headquarters Street Address: 3460 NW Industrial St. Headquarters City/State/Zip: Portland, OR 97210 (provide information requested below if different from above) Lead Point of Contact for Proposal - Name/Title: Michael Mahanay / GM, Sales & Marketing Tel: 800.642.3087 x 205 Fax: 503.641.5586 E-mail: [email protected] Street Address: 3460 NW Industrial St. City/State/Zip: Portland, OR 97219 Proposed Cost: $294/yr. The proposed cost listed above is for reference purposes only, not evaluation purposes. In the event that the cost noted above does not match the Bidder’s detailed cost proposal documents, then the information on the cost proposal documents will take precedence. This proposal and the pricing structure contained herein will remain firm for a period of 180 days from the date and time of the bid opening. No personnel on the multi-state Sourcing Team or any other involved state agency participated, either directly or indirectly, in any activities relating to the preparation of the Bidder’s proposal. No attempt has been made or will be made by the Bidder to induce any other person or firm to submit or not to submit a proposal. The undersigned is authorized to enter into contractual obligations on behalf of the above-named organization. -

2Nd Generation Intel Core Processor Family with Intel 6 Series Chipset Development Kit User Guide

2nd Generation Intel® Core™ Processor Family with Intel® 6 Series Chipset Development Kit User Guide March 2011 Document Number: 325208 About This Document INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. UNLESS OTHERWISE AGREED IN WRITING BY INTEL, THE INTEL PRODUCTS ARE NOT DESIGNED NOR INTENDED FOR ANY APPLICATION IN WHICH THE FAILURE OF THE INTEL PRODUCT COULD CREATE A SITUATION WHERE PERSONAL INJURY OR DEATH MAY OCCUR. Intel may make changes to specifications and product descriptions at any time, without notice. Intel Corporation may have patents or pending patent applications, trademarks, copyrights, or other intellectual property rights that relate to the presented subject matter. The furnishing of documents and other materials and information does not provide any license, express or implied, by estoppel or otherwise, to any such patents, trademarks, copyrights, or other intellectual property rights. Designers must not rely on the absence or characteristics of any features or instructions marked “reserved” or “undefined.” Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. Intel processor numbers are not a measure of performance. -

Keepixo’S Genova Live:Speed Is the Latest Addition to Genova Virtualizable Software Family of Products

High Density Video Transcoding Keepixo’s Genova Live:Speed is the latest addition to Genova Virtualizable Software family of products. It runs on the Kontron SYMKLOUD platform and leverages Intel’s Quick Sync Video (QSV) technology to dramatically increase transcoding density; minimize power consumption while meeting professional service grade levels. Media Processing Acceleration Genova Live:Speed The explosive growth of Internet video traffic has put Keepixo worked with Kontron to leverage the Kontron pressure on video transcoding infrastructures to SYMKLOUD Converged Infrastructure platform and optimize bandwidth, power consumption and cost of developed a comprehensive package that optimizes the operations. High density transcoding solutions such as performance of QSV and allows smooth deployment of Intel’s Quick Sync Video technology have emerged to highly dense transcoding infrastructures comprising of address these challenges. They introduce various levels hundreds of services. of HW acceleration to off-load computationally intensive tasks. Initially targeted at consumer Keepixo selected the Kontron SymKloud MS2910 applications, high density transcoding has become a platform to implement its high density transcoding viable option for professional transcoding solution. The MS2910 platform comes in a 2U (21” infrastructures when included in suitable packages that depth) chassis, dual hot-swappable 10GbE switches, address the requirements of professional applications. and can accommodate up to 9 modular compute servers, each hosting 2 independent CPUs for a total of Intel Quick Sync Video (QSV) is available on a range of up to 18 CPUs per chassis. The SymKloud compute Intel i7 and Xeon E3 processors fitted with on-chip nodes can be of different mix-and-match processor graphics. -

Mass-Producing Your Certified Cluster Solutions

Mass-Producing Your Certified Cluster Solutions White Paper The Intel® Cluster Ready program is designed to help you make the most of your engineering Intel® Cluster Ready resources. The program enables you to sell several different types of clusters from each solution High-Performance you design, by varying the hardware while maintaining the same software stack. You can gain a Computing broader range of cluster products to sell without engineering each one “from scratch.” As long as the software stack remains the same and works on each one of the hardware configurations, you can be confident that your clusters will interoperate with registered Intel Cluster Ready applications. Your customers can purchase your clusters with that same confidence, knowing they’ll be able to get their applications up and running quickly on your systems. Intel® Cluster Ready: Mass-Producing Your Certified Cluster Solutions Table of Contents Overview of Production-Related Activities � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � 3 Creating and certifying recipes � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � 3 Maintaining recipes � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � 3 Mass-producing recipes � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � -

SIMD Extensions

SIMD Extensions PDF generated using the open source mwlib toolkit. See http://code.pediapress.com/ for more information. PDF generated at: Sat, 12 May 2012 17:14:46 UTC Contents Articles SIMD 1 MMX (instruction set) 6 3DNow! 8 Streaming SIMD Extensions 12 SSE2 16 SSE3 18 SSSE3 20 SSE4 22 SSE5 26 Advanced Vector Extensions 28 CVT16 instruction set 31 XOP instruction set 31 References Article Sources and Contributors 33 Image Sources, Licenses and Contributors 34 Article Licenses License 35 SIMD 1 SIMD Single instruction Multiple instruction Single data SISD MISD Multiple data SIMD MIMD Single instruction, multiple data (SIMD), is a class of parallel computers in Flynn's taxonomy. It describes computers with multiple processing elements that perform the same operation on multiple data simultaneously. Thus, such machines exploit data level parallelism. History The first use of SIMD instructions was in vector supercomputers of the early 1970s such as the CDC Star-100 and the Texas Instruments ASC, which could operate on a vector of data with a single instruction. Vector processing was especially popularized by Cray in the 1970s and 1980s. Vector-processing architectures are now considered separate from SIMD machines, based on the fact that vector machines processed the vectors one word at a time through pipelined processors (though still based on a single instruction), whereas modern SIMD machines process all elements of the vector simultaneously.[1] The first era of modern SIMD machines was characterized by massively parallel processing-style supercomputers such as the Thinking Machines CM-1 and CM-2. These machines had many limited-functionality processors that would work in parallel. -

The New Intel® Xeon® Processor Scalable Family

Akhilesh Kumar Intel Corporation, 2017 Authors: Don Soltis, Irma Esmer, Adi Yoaz, Sailesh Kottapalli Notices and Disclaimers This document contains information on products, services and/or processes in development. All information provided here is subject to change without notice. Contact your Intel representative to obtain the latest forecast, schedule, specifications and roadmaps. Intel technologies’ features and benefits depend on system configuration and may require enabled hardware, software or service activation. Learn more at intel.com, or from the OEM or retailer. No computer system can be absolutely secure. Software and workloads used in performance tests may have been optimized for performance only on Intel microprocessors. Performance tests, such as SYSmark and MobileMark, are measured using specific computer systems, components, software, operations and functions. Any change to any of those factors may cause the results to vary. You should consult other information and performance tests to assist you in fully evaluating your contemplated purchases, including the performance of that product when combined with other products. For more complete information visit http://www.intel.com/performance. Optimization Notice: Intel's compilers may or may not optimize to the same degree for non-Intel microprocessors for optimizations that are not unique to Intel microprocessors. These optimizations include SSE2, SSE3, and SSSE3 instruction sets and other optimizations. Intel does not guarantee the availability, functionality, or effectiveness of any optimization on microprocessors not manufactured by Intel. Microprocessor-dependent optimizations in this product are intended for use with Intel microprocessors. Certain optimizations not specific to Intel microarchitecture are reserved for Intel microprocessors. Please refer to the applicable product User and Reference Guides for more information regarding the specific instruction sets covered by this notice. -

Liečba Firmy Krízovým Manažérom

SEPTEMBER- OKTÓBER 2016 Ročník VIII. Magazín o ekonomike, biznise a spoločnosti Cena: 2,20 € LIEČBA FIRMY KRÍZOVÝM MANAŽÉROM Neľahká cesta z červených do čiernych čísel Trendy a výzvy európskej logistiky Firemný blog: robte ho poriadne alebo vôbec Stalo sa, opravíte s naším poistením majetku. Poistenie majetku MÔJ DOMOV Postavte sa s odvahou všetkým nepred- vídaným situáciám, ktoré ohrozujú váš domov. Najoceňovanejšie poistenie majetku Môj domov ich za vás vyrieši rýchlo a fér. allianzsp.sk Infolinka 0800 122 222 VZDELÁVANIE Podchyťme všetky talenty, Magazín o ekonomike, biznise a spoločnosti lebo Európa ich potrebuje V deťoch sa ukrýva veľký potenciál, príliš často však zostáva nevyužitý. Registrované ako periodická tlač Ministerstvom kultúry Slovenskej To je niečo, čo si Európska únia jednoducho nemôže dovoliť: plytvanie republiky pod registračným číslom EV 3451/09, ISSN 1337-9798 ľudskými zdrojmi, ktoré robí ľudí nešťastnými a je takisto kolektívnym Vydanie september – október 2015 zlyhaním. Vydáva: Nemám pritom na mysli len nadanie na štúdium. Je načase uznať ši- Goodwill Publishing, s. r. o. rokú škálu talentu a zručností. Známe sú práce amerického výskumní- IČO: 44 635 770 LB)PXBSEB(BSEOFSB LUPSâJEFOUJmLPWBMWFĔBESVIPWJOUFMJHFODJFPE interpersonálnej po muzikálnu, od priestorovej po jazykovú, logickú Adresa redakcie: alebo intrapersonálnu. Azda všetci súhlasia s tým, že až príliš často sa GOODWILL, Nevädzová 5, 821 01 Bratislava talent hodnotí na základe pevných kritérií, ktoré neodrážajú jeho boha- UFMGBYtHPPEXJMM!HPPEXJMMFVTL tosť ani zložitosť. Musíme sa otvoriť koncepcii talentu a vidieť ďalej, za Ing. Juraj Filin študijné výsledky. Žiaľ, školy majú stále sklon sústrediť sa na úzku ideu šéfredaktor a konateľ spôsobilosti – na akademickú prácu. mMJO!HPPEXJMMFVTLtSFEBLDJB!HPPEXJMMFVTL Potrebujeme talenty pre vyššie vzdelávanie, ale aj pre oblasti odbor- tel.: 0907 78 91 64 ného vzdelávania a prípravy. -

The Economic Impact of Moore's Law: Evidence from When It Faltered

The Economic Impact of Moore’s Law: Evidence from when it faltered Neil Thompson Sloan School of Management, MIT1 Abstract “Computing performance doubles every couple of years” is the popular re- phrasing of Moore’s Law, which describes the 500,000-fold increase in the number of transistors on modern computer chips. But what impact has this 50- year expansion of the technological frontier of computing had on the productivity of firms? This paper focuses on the surprise change in chip design in the mid-2000s, when Moore’s Law faltered. No longer could it provide ever-faster processors, but instead it provided multicore ones with stagnant speeds. Using the asymmetric impacts from the changeover to multicore, this paper shows that firms that were ill-suited to this change because of their software usage were much less advantaged by later improvements from Moore’s Law. Each standard deviation in this mismatch between firm software and multicore chips cost them 0.5-0.7pp in yearly total factor productivity growth. These losses are permanent, and without adaptation would reflect a lower long-term growth rate for these firms. These findings may help explain larger observed declines in the productivity growth of users of information technology. 1 I would like to thank my PhD advisors David Mowery, Lee Fleming, Brian Wright and Bronwyn Hall for excellent support and advice over the years. Thanks also to Philip Stark for his statistical guidance. This work would not have been possible without the help of computer scientists Horst Simon (Lawrence Berkeley National Lab) and Jim Demmel, Kurt Keutzer, and Dave Patterson in the Berkeley Parallel Computing Lab, I gratefully acknowledge their overall guidance, their help with the Berkeley Software Parallelism Survey and their hospitality in letting me be part of their lab.