LECTURE 18 Switches and Switch Stress: the Concept of Safe Operating Area for a Device

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Power Electronics

Diodes and Transistors Semiconductors • Semiconductor devices are made of alternating layers of positively doped material (P) and negatively doped material (N). • Diodes are PN or NP, BJTs are PNP or NPN, IGBTs are PNPN. Other devices are more complex Diodes • A diode is a device which allows flow in one direction but not the other. • When conducting, the diodes create a voltage drop, kind of acting like a resistor • There are three main types of power diodes – Power Diode – Fast recovery diode – Schottky Diodes Power Diodes • Max properties: 1500V, 400A, 1kHz • Forward voltage drop of 0.7 V when on Diode circuit voltage measurements: (a) Forward biased. (b) Reverse biased. Fast Recovery Diodes • Max properties: similar to regular power diodes but recover time as low as 50ns • The following is a graph of a diode’s recovery time. trr is shorter for fast recovery diodes Schottky Diodes • Max properties: 400V, 400A • Very fast recovery time • Lower voltage drop when conducting than regular diodes • Ideal for high current low voltage applications Current vs Voltage Characteristics • All diodes have two main weaknesses – Leakage current when the diode is off. This is power loss – Voltage drop when the diode is conducting. This is directly converted to heat, i.e. power loss • Other problems to watch for: – Notice the reverse current in the recovery time graph. This can be limited through certain circuits. Ways Around Maximum Properties • To overcome maximum voltage, we can use the diodes in series. Here is a voltage sharing circuit • To overcome maximum current, we can use the diodes in parallel. -

Thermal Assessment and In-Situ Monitoring of Insulated

Thermal Assessment and In-Situ Monitoring of Insulated Gate Bipolar Transistors in Power Electronic Modules Preprint Erick Gutierrez,1 Kevin Lin,1 Patrick McCluskey,1 and Douglas DeVoto2 1 University of Maryland 2 National Renewable Energy Laboratory Presented at ASME 2019 International Technical Conference and Exhibition on Packaging and Integration of Electronic and Photonic Microsystems (IPACK2019) Anaheim, California October 7–9, 2019 NREL is a national laboratory of the U.S. Department of Energy Conference Paper Office of Energy Efficiency & Renewable Energy NREL/CP-5400-73583 Operated by the Alliance for Sustainable Energy, LLC February 2020 This report is available at no cost from the National Renewable Energy Laboratory (NREL) at www.nrel.gov/publications. Contract No. DE-AC36-08GO28308 Thermal Assessment and In-Situ Monitoring of Insulated Gate Bipolar Transistors in Power Electronic Modules Preprint Erick Gutierrez,1 Kevin Lin,1 Patrick McCluskey,1 and Douglas DeVoto2 1 University of Maryland 2 National Renewable Energy Laboratory Suggested Citation Gutierrez, Erick, Kevin Lin, Patrick McCluskey, and Douglas DeVoto. 2020. Thermal Assessment and In-Situ Monitoring of Insulated Gate Bipolar Transistors in Power Electronic Modules: Preprint. Golden, CO: National Renewable Energy Laboratory. NREL/CP-5400-73583 https://www.nrel.gov/docs/fy20osti/73583.pdf. NREL is a national laboratory of the U.S. Department of Energy Conference Paper Office of Energy Efficiency & Renewable Energy NREL/CP-5400-73583 Operated by the Alliance for Sustainable Energy, LLC February 2020 This report is available at no cost from the National Renewable Energy National Renewable Energy Laboratory Laboratory (NREL) at www.nrel.gov/publications. -

Data Sheet Freemaq PCSK-Multi PCSK

POWER ELECTRONICS 45 FREEMAQ PCSK FREEMAQ MULTI PCSK UTILITY SCALE BATTERY INVERTER POWER CONVERSION SYSTEM FRU FIELD REPLACEABLE UNITS MODULAR DESIGN UP TO 3 INDEPENDENT BESS INPUTS ICOOL 3 PROVEN HARDWARE AND ROBUST OUTDOOR DESIGN FEATURED WITH THE 4 QUADRANT LATEST CONTROL The Freemaq PCSK is a modular solution from 1700 kW 3 LEVEL TOPOLOGY to 3800 kW with configurable DC and AC voltages making it compatible with all battery technology and manufacturers. Power Electronics is a proven partner in the solar and energy NEMA 3R / IP55 storage market. The PCSK has been designed to be the lowest LCOE solution in the market for storage applications. The Power Electronics Freemaq PCSK offers proven hard- ware to meet storage and grid support challenges.The energy production industry is embracing renewable energy sources. However, high penetration creates power transmission instability challenges, thus Grid Operators require stringent dynamic and static grid support features for solar inverters and Power Conversion Systems (PCS). The MULTI PCSK can support two or three independent battery systems and optimize the storage facility. The converters can perform grid support functions such as: Peak Shaving, Ramp Rate Control, Frequency Regulation, Load Leveling and Voltage Regulation, controlled by a Power Plant Controller or SCADA. The converters stations are turn- key solutions ready for connection to the battery container and MV power distribution wiring. Units are designed for concrete pads or piers, open skids or integrated into full container solutions. POWER ELECTRONICS COMPACT DESIGN - EASY TO SERVICE By providing full front access the Freemaq PCSK series With the Freemaq PCSK, Power Electronics offers its most simplifies the maintenance tasks, reducing the MTTR (and compact solution, achieving 3.8MW in just 12ft long, reducing achieving a lower OPEX). -

Eaton's Power Electronics Portfolio

Eaton’s Power Electronics Portfolio • Bob Yanniello • June 27, 2017 © 2015 Eaton. All Rights Reserved.. © 2015 Eaton. All Rights Reserved.. 2 © 2015 Eaton. All Rights Reserved.. 3 © 2015 Eaton. All Rights Reserved.. 4 Power Xpert Inverter – 1.0 – 2.5 MW Inverter Throat – direct Step-up coupling Transformer Tracker (or AC) power and controls © 2015 Eaton. All Rights Reserved.. 5 Power module design • Latest generation of Semikron Skiip 4 IGBT – integrated driver & heat sink • Rated for 175°C and high cyclic duty applications • Vishay film capacitors • User replaceable modules © 2015 Eaton. All Rights Reserved.. 6 Power Xpert Utility-Scale Solar Inverter 1500Vdc – 98.5% efficiency DC Power Conversion AC Compartment Compartments Compartment Up to 21x 350A contactors with fuses AC Line Filter 3200A Main Breaker with MO and Close LOTO coupled to DC Feeders . Transformer AC Line From . Filter Combiner . boxes Open / 20A with LOTO Close AC Line Contactor Filter opens Positive and UPS Negative DC LOTO SEL Inverter poles 751 Control Relay Power © 2015 Eaton. All Rights Reserved.. 7 Power Xpert™ Energy Storage Inverter 1250 V max • Battery Types • LG Chem (LMO) • Kokam (LTO) • Enerdel (LTO) • Altair Nano (LTO) • ZBB (flow) 500kW outdoor Inverter • Xtreme (ALA) 3MW site (indoor Inverters) • Mitsubishi (LMO) • JCI (NCA) • Samsung (LMO) • SPS/Lischen • Powin • Primus 500kW Compact Pad Mount © 2015 Eaton. All Rights Reserved.. 8 Power Xpert® Energy Storage Inverter Power Xpert Inverter 60A @ 480 Inverter DC VAC connection AC Line Filter To Battery container for aux power To Transformer From Battery AC Line container Filter AC Line Filter Inverter Controls Power Inverter Controller 15A @ 3A @ 120VAC F.O. -

Fundamentals of MOSFET and IGBT Gate Driver Circuits

Application Report SLUA618A–March 2017–Revised October 2018 Fundamentals of MOSFET and IGBT Gate Driver Circuits Laszlo Balogh ABSTRACT The main purpose of this application report is to demonstrate a systematic approach to design high performance gate drive circuits for high speed switching applications. It is an informative collection of topics offering a “one-stop-shopping” to solve the most common design challenges. Therefore, it should be of interest to power electronics engineers at all levels of experience. The most popular circuit solutions and their performance are analyzed, including the effect of parasitic components, transient and extreme operating conditions. The discussion builds from simple to more complex problems starting with an overview of MOSFET technology and switching operation. Design procedure for ground referenced and high side gate drive circuits, AC coupled and transformer isolated solutions are described in great details. A special section deals with the gate drive requirements of the MOSFETs in synchronous rectifier applications. For more information, see the Overview for MOSFET and IGBT Gate Drivers product page. Several, step-by-step numerical design examples complement the application report. This document is also available in Chinese: MOSFET 和 IGBT 栅极驱动器电路的基本原理 Contents 1 Introduction ................................................................................................................... 2 2 MOSFET Technology ...................................................................................................... -

Overview of the DOE Advanced Power Electronics and Electric Motor R&D

VEHICLE TECHNOLOGIES OFFICE Overview of the DOE Advanced Susan Rogers Power Electronics and Electric Steven Boyd Motor R&D Program Advanced Power Electronics and Electric Motors June 17, 2014 Vehicle Technologies Office 1 APEEM R&D Program Vehicle Technologies Office Hybrid Electric Systems R&D Energy Storage Vehicle Systems Advanced Power Electronics & Electric Motors (APEEM) R&D Industry Federal Agencies Academia National Labs 2 APEEM R&D Mission and Budget Develop advanced power electronics, electric motors and electric drive systems to enable large market penetration of hybrid and electric vehicles Meeting program targets will enable market success: increase performance, efficiency and reliability, while lowering cost, weight, and volume FY 2014 Budget R&D emphasis accelerates: • Adoption of wide bandgap Power Electronics semiconductors • Reduction or elimination of 29% 29% Electric Motors rare earth magnets Thermal Management FY 2014 FOAs: 7% • Power Electronics - $6M Testing & Analysis • Wide bandgap commercialization 24% 11% • Incubator - $1.6M FY 14 FOAs • “Off-Roadmap” technology R&D FY 2013 FY 2014 FY 2015 Request $27.2 M $24 M $35.5 M 3 Electric Drive System Components • Electric motor – converts electrical energy to mechanical power for motive power • Inverter – converts high voltage direct current to varying pulses that control and power the electric motor • Charger – modifies and controls electrical energy to re-energize the battery • Converter(s) – increases the battery voltage for the traction drive system and decreases -

Power Electronics for Distributed Energy Systems and Transmission and Distribution Applications

ORNL/TM-2005/230 POWER ELECTRONICS FOR DISTRIBUTED ENERGY SYSTEMS AND TRANSMISSION AND DISTRIBUTION APPLICATIONS L. M. Tolbert T. J. King B. Ozpineci J. B. Campbell G. Muralidharan D. T. Rizy A. S. Sabau H. Zhang* W. Zhang* Y. Xu* H. F. Huq* H. Liu* December 2005 *The University of Tennessee-Knoxville ORNL/TM-2005/230 Engineering Science and Technology Division POWER ELECTRONICS FOR DISTRIBUTED ENERGY SYSTEMS AND TRANSMISSION AND DISTRIBUTION APPLICATIONS L. M. Tolbert T. J. King B. Ozpineci J. B. Campbell G. Muralidharan D. T. Rizy A. S. Sabau H. Zhang W. Zhang Y. Xu H. F. Huq H. Liu Publication Date: December 2005 Prepared by the OAK RIDGE NATIONAL LABORATORY Oak Ridge, Tennessee 37831 managed by UT-BATTELLE, LLC for the U.S. DEPARTMENT OF ENERGY Under contract DE-AC05-00OR22725 DOCUMENT AVAILABILITY Reports produced after January 1, 1996, are generally available free via the U.S. Department of Energy (DOE) Information Bridge. Web site http://www.osti.gov/bridge Not available externally. Reports are available to DOE employees, DOE contractors, Energy Technology Data Exchange (ETDE) representatives, and International Nuclear Information System (INIS) representatives from the following source. Office of Scientific and Technical Information P.O. Box 62 Oak Ridge, TN 37831 Telephone 865-576-8401 Fax 865-576-5728 E-mail [email protected] Web site http://www.osti.gov/contact.html This report was prepared as an account of work sponsored by an agency of the United States Government. Neither the United States Government nor any agency thereof, nor any of their employees, makes any warranty, express or implied, or assumes any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights. -

Data Sheet Freemaq PCSM-Multi PCSM

POWER ELECTRONICS 21 FREEMAQ PCSM FREEMAQ MULTI PCSM UTILITY SCALE MV BATTERY INVERTER POWER CONVERSION SYSTEM FRU FIELD REPLACEABLE UNITS MODULAR DESIGN UP TO 3 INDEPENDENT BESS INPUTS THE INNOVATIVE MEDIUM VOLTAGE CENTRAL STRING ICOOL 3 BATTERY INVERTER 4 QUADRANT The Power Electronics PCSM medium voltage battery inverter is designed for utility scale storage applications, that require the advantages of a central inverter solution but also the modularity of a string architecture. The PCSM can reach 3 LEVEL TOPOLOGY up to a nominal power of 3.6 MVA and it is compatible with all battery technology and manufacturers. It also has the added advantage of having an integrated medium voltage NEMA 3R transformer and switchgear. The MULTI PCSM can support two or three independent battery systems and optimize the storage facility. Power Electronics converters have been designed to be the lowest LCOE solution in the market for storage applications. The Power Electronics Freemaq PCSM offers proven hardwa- re to meet storage and grid support challenges.The energy production industry is embracing renewable energy sources. However, high penetration creates power transmission instability challenges, thus Grid Operators require stringent dynamic and static grid support features for solar inverters and Power Conversion Systems (PCS). The converters can perform grid support functions such as: Peak Shaving, Ramp Rate Control, Frequency Regulation, Load Leveling and Voltage Regulation, controlled by a Power Plant Controller or SCADA. The Freemaq PCSM stations are turn-key solutions ready for connection to the battery contai- ner and MV power distribution wiring. Units are designed for concrete pads or piers. POWER ELECTRONICS REAL TURN-KEY SOLUTION - EASY TO SERVICE With the PCSM, Power Electronics offers a real turn-key By providing full front access the PCSM series simplifies solution, including the MV transformer and switchgear fully the maintenance tasks, reducing the MTTR (and achieving assembled and tested at the factory. -

Lecture Notes on Power Electronics Subject Code – BEE1602

VEER SURENDRA SAI UNIVERSITY OF TECHNOLOGY BURLA, ODISHA, INDIA DEPARTMENT OF ELECTRICAL ENGINEERING Lecture Notes on Power Electronics Subject code – BEE1602 6th Semester B.Tech. (Electrical Engineering) Disclaimer This document does not claim any originality and cannot be used as a substitute for prescribed textbooks. The information presented here is merely a collection by the committee members for their respective teaching assignments. Various sources as mentioned at the end of the document as well as freely available material from internet were consulted for preparing this document. The ownership of the information lies with the respective authors or institutions. Further, this document is not intended to be used for commercial purpose and the committee members are not accountable for any issues, legal or otherwise, arising out of use of this document. The committee members make no representations or warranties with respect to the accuracy or completeness of the contents of this document and specifically disclaim any implied warranties of merchantability or fitness for a particular purpose. The committee members shall be liable for any loss of profit or any other commercial damages, including but not limited to special, incidental, consequential, or other damages. (6TH SEMESTER) POWER ELECTRONICS (3-1-0) MODULE-I (10 HOURS) Thyristors, Static V-I Characteristics of SCR, TRIAC, GTO & IGBT, Turn-On & Turn-OFF Mechanism of SCR, Gate Turnoff Thyristor (GTO) .Power BJTs . Power MOSFETs - Insulated Gate Bipolar Transistors (IGBTs) - Basic Structure and VI Characteristics. Static, dynamic and thermal characteristics. Protection, cooling and mounting techniques. Series and Parallel operation of devices. Triggering and basics of driver circuits. -

Power Semiconductor Devices the Difference

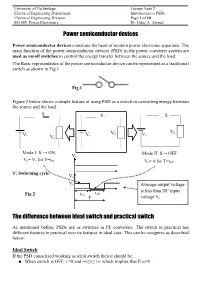

University of Technology Lecture Note 2 Electrical Engineering Department Introduction to PSDs Electrical Engineering Division Page 1 of 10 EG 405: Power Electronics Dr. Oday A. Ahmed Power semiconductor devices Power semiconductor devices constitute the heart of modern power electronic apparatus. The main function of the power semiconductor devices (PSD) in the power converter system are used as on/off switches to control the energy transfer between the source and the load. The Basic representation of the power semiconductor device can be represented as a traditional switch as shown in Fig.1. Fig.1 Figure 2 below shows a simple feature of using PSD as a switch in converting energy between the source and the load. S S S Vo Vo Vs Vs Vs Vo Mode I: S → ON Mode II: S→ OFF Vs Vo= Vs for T=ton V = 0 for T=t o off T: Switching cycle Vo Vs Average output voltage is less than DC input Fig.2 ton toff T voltage Vs The difference between ideal switch and practical switch As mentioned before, PSDs use as switches in PE converters. The switch in practical has different features in practical over its features in ideal case. This can be recognize as described below: Ideal Switch If the PSD considered working as ideal switch then it should be: ■ When switch is OFF, i =0 and -∞≤v≤+∞ which implies that PON=0 University of Technology Lecture Note 2 Electrical Engineering Department Introduction to PSDs Electrical Engineering Division Page 2 of 10 EG 405: Power Electronics Dr. Oday A. Ahmed ■ When switch is ON, V =0 and -∞≤ I ≤+∞ which implies that PON=0 It should be possible to easily turn the switch ON and OFF by applying an appropriate control signal. -

Part I :Power Electronics Chapter One

PART I :POWER ELECTRONICS CHAPTER ONE POWER ELECTRONICS FUNDAMENTALS 1.1 INTRODUCTION The first electronics revolution began in 1948 with the invention of the bipolar silicon transistor at Bell Telephone Laboratories by Bardeen, Bratain, and Schockley. This invention leads to the most recent advanced in electronic technologies seen today. Also, modern microelectronics has evolved over the years from these silicon semiconductors. In 1957, the second electronics revolution started with the development of the four- layer high power commercial thyristor by the General Electric Company in USA. The invention of this device and its later applications in energy processing and motor control fields has initiated a new era of power electronics. From the early 1960s until quite recently, the thyristor and its family was almost universally used as the high power semiconductor switch which leads to introduction of many different types of energy conversion techniques. The energy conversion using power electronics achieves conversion of electric power from one form to another, using a combin- ation of high-power semiconductor devices and passive components, mainly transformers, inductors, and capacitors. The input and output may be alternating current (a.c.) or direct current (d.c.) and may differ in magnitude and/or frequency. The end goals of a power electronic conv- erter are to achieve high efficiency of conversion, minimize size and weight, and achieve desired regulation of the output. Power electronic converters can be classified into four different types on the basis of input and output, dc-dc, dc-ac, ac-dc, and ac-ac, named with the first part referring to the input and the second to the output. -

A Thermal Model for Insulated Gate Bipolar Transistor Module Zhaohui Luo, Hyungkeun Ahn, and Mahmoud A

902 IEEE TRANSACTIONS ON POWER ELECTRONICS, VOL. 19, NO. 4, JULY 2004 A Thermal Model for Insulated Gate Bipolar Transistor Module Zhaohui Luo, Hyungkeun Ahn, and Mahmoud A. El Nokali, Senior Member, IEEE Abstract—A thermal resistor–capacitor ( ) model is intro- the thermal network can be extracted from the thermal dy- duced for the power insulated gate bipolar transistor (IGBT) namic curve [7]. modules used in a three-phase inverter. The parameters of the The manufacturer of IGBT module provides the transient model are extracted from the experimental data for the transient thermal impedance curve of junction to case to the users. In thermal impedance from-junction-to-case j and case-to-am- bient . The accuracy of the model is verified by comparing a real application environment, the IGBT module is mounted its predictions with those resulting from the three–dimensional on a heatsink in order to keep the device temperature in the finite element method simulation. The parameter extraction safe operation area. Natural air, forced air or water-cooling [8] algorithm is easy to adapt to other types of power modules in an are typical methods of cooling used. The thermal behavior of a industrial application environment. system is therefore determined by the thermal impedance of the Index Terms—Finite element method (FEM), insulated gate IGBT from junction to case, the thermal impedance of the inter- bipolar transistor (IGBT), thermal resistor–capacitor ( ) face (thermal grease, etc.) between the IGBT and the heatsink network, transient thermal impedance. in addition to the heatsink thermal behavior. If we assume the system to be linear and use a one-dimensional formulation, I.