Modeling Spiking Neural Networks on Spinnaker

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

The Millennium Technology Prize Laureate 2010 Professor Stephen

1 (9) The Millennium Technology Prize Laureate 2010 “For his invention of the ARM microprocessor and its implementation on silicon chips. This invention has enabled the revolution in mobile electronics. To date, more than 18 billion ARM-based chips have been manufactured and are used in ubiquitous computing applications, such as mobile phones, digital photography and video, music players, fixed and wireless networking, automobiles and health care, benefitting a large number of people all over the world.” Professor Stephen Furber Professor of Computer Engineering, the University of Manchester, United Kingdom Born March 1953 in Manchester, United Kingdom. Timeline 1982 Acorn BBC Micro launched 1983 Acorn starts RISC Machine project with Furber as principal designer 1985 First ARM microprocessor produced 1987 ARM processor debuts as the first RISC processor for Acorn Archimedes desktop computer 1990 Advanced RISC Machines (ARM) spins out of Acorn and Apple Computers collaboration, Furber continues his research of low power computing as a professor at University of Manchester. 1998 ARM listed on the London Stock Exchange and NASDAQ. Over 50 million ARM powered products shipped. 2010 20 billion ARM based chips manufactured Creator of the ARM microprocessor The 2010 Millennium Technology Prize Laureate Steve Furber is the principal designer of the ARM 32- bit RISC microprocessor, an innovation that revolutionised mobile electronics. The ingeniously designed processor enabled the development of cheap, powerful handheld, battery-operated devices. In the past 25 years nearly 20 billion ARM based chips have been manufactured. You may never have heard of ARM microprocessors, but probably use at least one every day. They tick inside our mobile phones, mp3-players, video recorders and home routers. -

Spinnaker Project

10/21/19 The SpiNNaker project Steve Furber ICL Professor of Computer Engineering The University of Manchester 1 200 years ago… • Ada Lovelace, b. 10 Dec. 1815 "I have my hopes, and very distinct ones too, of one day getting cerebral phenomena such that I can put them into mathematical equations--in short, a law or laws for the mutual actions of the molecules of brain. …. I hope to bequeath to the generations a calculus of the nervous system.” 2 1 10/21/19 70 years ago… 3 Bio-inspiration • Can massively-parallel computing resources accelerate our understanding of brain function? • Can our growing understanding of brain function point the way to more efficient parallel, fault-tolerant computation? 4 2 10/21/19 ConvNets - structure • Dense convolution kernels • Abstract neurons • Only feed-forward connections • Trained through backpropagation 5 The cortex - structure Feedback input Feed-forward output Feed-forward input Feedback output • Spiking neurons • Two-dimensional structure • Sparse connectivity 6 3 10/21/19 ConvNets - GPUs • Dense matrix multiplications • 3.2kW • Low precision 7 Cortical models - Supercomputers • Sparse matrix operations • Efficient communication of spikes • 2.3MW 8 4 10/21/19 Cortical models - Neuromorphic hardware • Memory local to computation • Low-power • Real time • 62mW 9 Start-ups and industry interest 5 10/21/19 SpiNNaker project • A million mobile phone processors in one computer • Able to model about 1% of the human brain… • …or 10 mice! 11 SpiNNaker system 12 6 10/21/19 SpiNNaker chip Multi-chip packaging -

B. Tech in Instrumentation & Control Engineering

Nirma University Institute of Technology Department of Instrumentation and Control Engineering B Tech in Instrumentation and Control Engineering 1 | P a g e MA101: Calculus [3 1 0 4] Learning outcomes: On completion of the course student CLO1: will be able to find higher ordered derivatives and hence represent function in power series of (x-a) CLO2: will apply the knowledge of function of several variables , its derivatives in engineering problems CLO3: will apply the knowledge of special functions(Gamma, Beta, Elliptic, Error) and its application in engineering problems CLO4: will apply the knowledge of multiple integration and its application in engineering problems Syllabus: Unit I: Differential Calculus Review of limits, continuity and differentiability, Successive differentiation, Leibnitz theorem (without proof), Indeterminate forms, Taylor’s and Maclaurin’s expansion of single variable, Partial Differentiation, Total derivative, Chain Rule, Implicit function, Euler’s theorem and its applications, Taylor’s and Maclaurin’s expansion of function of several variables, Maxima and Minima of function of several variables, Lagrange’s method of undetermined multipliers, Jacobian. Unit II: Integral Calculus Review of proper and improper integrals, Reduction formulae, Beta-Gamma functions, Error function, Tracing of curves, Rectification, Quadrature, Volume of solid of revolution, Area of surface of revolution, Double integral and evaluation, Change of order of integration, Change of variable, Triple integral and evaluation, Area using double integration, Volume as double and triple integration, Volume of solid by double integration. References: 1. Thomas’ Calculus(Latest edition), Pearson publication. 2. G B Thomas and R. L. Finney, Calculus and Analytic Geometry (Latest edition), Narosa Publication, Delhi. -

Review and Accounts 2012/2013 National Life Stories Chairman’S

Life NATIONAL stories Review and Accounts 2012/2013 National Life Stories Chairman’s When many people think about history, they think about initiated a series of innovative interviewing programmes books and documents, castles or stately homes. In fact history funded almost entirely from sponsorship, charitable and Foreword is all around us, in our own families and communities, in the individual donations and voluntary effort. living memories and experiences of older people. Everyone has a story to tell about their life which is unique to them. Each collection comprises recorded in-depth interviews of Whilst some people have been involved in momentous a high standard, plus content summaries and transcripts to historical events, regardless of age or importance we all assist users. Access is provided via the Sound and Moving have interesting life stories to share. Unfortunately, because Image Catalogue at www.cadensa.bl.uk and a growing memories die when people do, if we don’t record what number of interviews are made available for remote web people tell us, that history can be lost forever. use. Each individual life story interview is several hours long, covering family background, childhood, education, work, National Life Stories (NLS) was established in 1987 and its leisure and later life. mission is: ‘To record the first-hand experiences of as wide a cross section of society as possible, to preserve the recordings, Alongside the British Library’s other oral history holdings, to make them publicly available and encourage their use’. which stretch back to the beginning of the twentieth century, As an independent charitable trust within the Oral History NLS’s recordings form a unique and invaluable record of Section of the British Library, NLS’s key focus and expertise people’s lives in Britain today. -

Year in Review

Year in review For the year ended 31 March 2017 Trustees2 Executive Director YEAR IN REVIEW The Trustees of the Society are the members Dr Julie Maxton of its Council, who are elected by and from Registered address the Fellowship. Council is chaired by the 6 – 9 Carlton House Terrace President of the Society. During 2016/17, London SW1Y 5AG the members of Council were as follows: royalsociety.org President Sir Venki Ramakrishnan Registered Charity Number 207043 Treasurer Professor Anthony Cheetham The Royal Society’s Trustees’ report and Physical Secretary financial statements for the year ended Professor Alexander Halliday 31 March 2017 can be found at: Foreign Secretary royalsociety.org/about-us/funding- Professor Richard Catlow** finances/financial-statements Sir Martyn Poliakoff* Biological Secretary Sir John Skehel Members of Council Professor Gillian Bates** Professor Jean Beggs** Professor Andrea Brand* Sir Keith Burnett Professor Eleanor Campbell** Professor Michael Cates* Professor George Efstathiou Professor Brian Foster Professor Russell Foster** Professor Uta Frith Professor Joanna Haigh Dame Wendy Hall* Dr Hermann Hauser Professor Angela McLean* Dame Georgina Mace* Dame Bridget Ogilvie** Dame Carol Robinson** Dame Nancy Rothwell* Professor Stephen Sparks Professor Ian Stewart Dame Janet Thornton Professor Cheryll Tickle Sir Richard Treisman Professor Simon White * Retired 30 November 2016 ** Appointed 30 November 2016 Cover image Dancing with stars by Imre Potyó, Hungary, capturing the courtship dance of the Danube mayfly (Ephoron virgo). YEAR IN REVIEW 3 Contents President’s foreword .................................. 4 Executive Director’s report .............................. 5 Year in review ...................................... 6 Promoting science and its benefits ...................... 7 Recognising excellence in science ......................21 Supporting outstanding science ..................... -

JTAG 8 2.1 Test Logic

Diploma Thesis University of Applied Sciences Augsburg Department of Computer Science Open On-Chip Debugger Design and Implementation of an On-Chip Debug Solution for Embedded Target Systems based on the ARM7 and ARM9 Family Submitted by Dominic Rath, summer semester 2005 Examiner: Prof. Dr. Hubert Högl Examiner: Prof. Burkhard Stork Diploma Thesis University of Applied Sciences Augsburg Department of Computer Science I affirm that the diploma thesis is my own work, and that it has never been submitted for examination purposes before. All sources and citations used have been quoted as such, and all utilized tools have been mentioned. Dominic Rath Open On-Chip Debugger an On-Chip Debug Solution for Embedded Target Systems based on the ARM7 and ARM9 Family Dominic Rath c 2005 Dominic Rath All rights reserved 10 09 08 07 06 05 6 5 4 3 2 1 First edition: 11 July 2005 Second impression, with corrections: 18 July 2005 Permission is granted to copy, distribute and/or modify this document under the terms of the GNU Free Documentation License, Version 1.2 or any later version published by the Free Software Foundation; with no Invariant Sections, no Front-Cover Texts, and no Back-Cover Texts. A copy of the license is included in the section entitled "GNU Free Documentation License". Contents Contents i List of Figures iv List of Tables v 1 Embedded Systems Debugging 1 1.1 Debug Solutions . 2 Logic Analyzers, Trace Hardware . 2 In-Circuit Emulators, ROM Emulators . 2 Debug Stubs . 3 Integrated Debug Circuitry, On-Chip Debug . 3 1.2 ARM Debug Solutions . -

Mepco Schlenk Engineering College, Sivakasi (Autonomous) Affiliated to Anna University, Chennai 600 025 Regulations: Mepco - R2013 (Full Time) B

MEPCO SCHLENK ENGINEERING COLLEGE, SIVAKASI (AUTONOMOUS) AFFILIATED TO ANNA UNIVERSITY, CHENNAI 600 025 REGULATIONS: MEPCO - R2013 (FULL TIME) B. E. ELECTRONICS AND COMMUNICATION ENGINEERING Department Vision To render services to meet the growing global challenges of Engineering Industries and Organizations by Educating Students to become exemplary Professional Electronics and Communication Engineers of High Ethics Department Mission To enable Graduates evolve as Competent Hardware and Software Engineers needed by Industry with emphasis on virtues contributing to Societal Welfare Programme Educational Objectives (PEOs) PEO-1 Professional Integrate fundamentals and up to date Development approaches derived from the engineering sciences and practice to accomplish professional development in a responsive and innovative manner PEO-2 Team Work Handle multi-faceted and multi-disciplinary and projects to engage in effective teamwork & Leadership exercise leadership with significant legal, social, environmental and economic considerations 60 PEO-3 Lifelong Continually receptive to new technological Learning & and cultural challenges through life-long Virtues learning leading to advanced degrees, publications, presentations, awards and exhibit good citizenship with elegant mannerism Programme Outcomes (POs) PO1 Apply knowledge of mathematics, science, engineering fundamentals and an engineering specialization to the conceptualization of Electronics & Communication engineering models. PO2 Identify, formulate, research literature and solve complex -

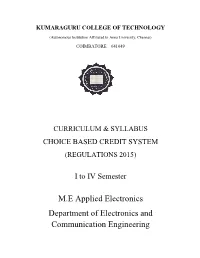

M.E Applied Electronics Department of Electronics and Communication Engineering Department of Electronics and Communication Engineering

KUMARAGURU COLLEGE OF TECHNOLOGY (Autonomous Institution Affiliated to Anna University, Chennai) COIMBATORE – 641049 CURRICULUM & SYLLABUS CHOICE BASED CREDIT SYSTEM (REGULATIONS 2015) I to IV Semester M.E Applied Electronics Department of Electronics and Communication Engineering Department of Electronics and Communication Engineering Vision To be a centre of repute for learning and research with internationally accredited curriculum, state-of-the-art infrastructure and laboratories to enable the students to succeed in globally competitive environments in academics and industry Mission The Department is committed to set standards of excellence in its academic delivery aimed to imbibe right attitude and leadership quality in students to apply the acquired knowledge and skills to meet the challenges of evolving global and local needs adhering to professional ethics. Kumaraguru College of Technology Coimbatore – 641 049 Regulation 2015 CBCS – PG Curriculum Name of the PG Programme: Applied Electronics Foundation Courses (FC) S. Course Course Title Periods/Wk Preferred No. Code & Credits Semester L T P C 1. P15MAT108 Applied Algebra 3 1 0 4 I 2. P15AET103 Advanced Signal Processing 3 1 0 4 I Professional Core (PC) S. Course Course Title Periods /Wk Preferred No. Code & Credits Semester L T P C Specilisation 1: Advanced Digital System 1. P15AET101 3 1 0 4 I Design 2. P15AET102 VLSI Design Techniques 3 0 0 3 I 3. P15AET104 Embedded Systems 3 0 0 3 I Embedded Systems 4. P15AEP101 Laboratory 0 0 3 0 I Analog Integrated Circuit 5. P15AET201 3 1 0 4 II Design Advanced Control 6. P15AET202 3 0 0 3 II Engineering 7. -

Publications Core Magazine, 2012 This

2012 COMMEMORATIVE ISSUE C O RE A Publication of 25 Years of the Fellow Awards the Computer The Origins of Timesharing History Museum An Evening with Walter Isaacson Close up of the Amdahl 470V/6 Computer, 1975. The 470V/6 was the Amdahl Corporation’s fi rst product and ran the same software as IBM System/370 computers but cost less and was smaller and faster. Opposite page: Close-up of IBM 305 RAMAC System Diagram B CORE 2012 / HALL OF FELLOWS DEPARTMENTS MUSEUM UPDATES EXPLORE THE COLLECTION 2 4 6 56 60 58 Contributors An Analog Life An Evening with Oral Histories: Donor Profile Recent Artifact Walter Isaacson The Origins of Donations 3 5 61 Timesharing CEO’s Letter Talking to the Future 7 Museum Donors The President @ CHM C O RE 2012 9 SPECIAL SECTION: TWENTY-FIVE YEARS OF FELLOWS 10 12 14 18 The Fellow Awards Fellows at a Glance Visionary Pioneer 25 Years of Fellows It was 25 years ago that the See an overview of our Fellows— Grace Murray Hopper was a The Computer History Museum Museum began its Fellows where they studied and worked unique individual: a woman in a Fellows often have very inter- program. Since that time, the and what they are known for—in man’s world of computers and esting life trajectories, full of Award has been given to over this two-page chart that shows mathematics and an admiral in dramatic turns and unexpected 60 outstanding individuals in 25 years of Fellows history in an the U.S. Naval Reserve. -

Arm System-On-Chip Architecture.Pdf

Preface Aims This book introduces the concepts and methodologies employed in designing a system-on-chip (SoC) based around a microprocessor core and in designing the microprocessor core itself. The principles of microprocessor design are made con- crete by extensive illustrations based upon the ARM. The aim of the book is to assist the reader in understanding how SoCs and micro- processors are designed and used, and why a modern processor is designed the way that it is. The reader who wishes to know only the general principles should find that the ARM illustrations add substance to issues which can otherwise appear somewhat ethereal; the reader who wishes to understand the design of the ARM should find that the general principles illuminate the rationale for the ARM being as it is. Other microprocessor architectures are not described in this book. The reader who wishes to make a comparative study of architectures will find the required informa- tion on the ARM here but must look elsewhere for information on other designs. Audience The book is intended to be of use to two distinct groups of readers: • Professional hardware and software engineers who are tasked with designing an SoC product which incorporates an ARM processor, or who are evaluating the ARM for a product, should find the book helpful in their duties. Although there is considerable overlap with ARM technical publications, this book provides a broader context with more background. It is not a substitute for the manufac turer's data, since much detail has had to be omitted, but it should be useful as an introductory overview and adjunct to that data. -

Membership of RAE2008 Panels

Membership of RAE2008 panels November 2007 Ref RAE 03/2007 Membership of RAE2008 panels To Heads of HEFCE-funded higher education institutions Heads of HEFCW-funded higher education institutions Heads of SFC-funded higher education institutions Heads of universities in Northern Ireland Of interest to those Research assessment, Research policy, responsible for Planning Reference RAE 03/2007 Publication date November 2007 Enquiries to Raegan Hiles or Davina Madden tel 0117 931 7267 e-mail [email protected] Executive summary Purpose 1. This document lists the membership of the main and sub-panels for the 2008 Research Assessment Exercise (RAE2008). The panels will assess the quality of research in submissions to RAE2008. Key points 2. For the purpose of RAE2008, each academic discipline is assigned to one of 67 units of assessment (UOAs). There is a two-tier panel system: 67 sub-panels of experts, one for each UOA, work under the guidance of 15 main panels. Under each main panel are broadly cognate disciplines whose subjects have similar approaches to research. 3. Panel members are experts drawn from higher education institutions (HEIs) and the wider research community, and are nominated by subject associations and other stakeholder organisations. Each main panel and sub-panel has stipulated criteria and working methods that they will adhere to in making assessments: these were published in January 2006 as RAE 01/2006: RAE2008: Panel criteria and working methods. 4. This list of panel membership is correct at the time of going to print. Should any member retire from the panel or be replaced during 2008, we will update the electronic list available at www.rae.ac.uk under ‘Panels’. -

Spinnaker Applications

SpiNNaker Applications Steve Furber ICL Professor of Computer Engineering The University of Manchester 1 SpiNNaker project • A million mobile phone processors in one computer • Able to model about 1% of the human brain… • …or 10 mice! 2 SpiNNaker chip Multi‐chip packaging by UNISEM Europe SpiNNaker machines SpiNNaker board • HBP platform (864 ARM cores) – 1M cores – 11 cabinets (including server) • Launch 30 March 2016 – then 500k cores – 93 remote users – 5,134 SpiNNaker jobs run SpiNNaker chip (18 ARM cores) SpiNNaker racks (1M ARM cores) 4 SpiNNaker machines • 100 SpiNNaker systems in use – global coverage • 4-node boards – training & small- scale robotics • 48-node boards sales (40 48-node boards) – insect-scale networks loans • multi-board systems • 1M-core HBP platform 5 SpiNNaker applications Computational Neuroscience Simulation 6 Cortical microcolumn 1st full-scale simulation of 1mm2 cortex on neuromorphic & HPC systems • 77,169 neurons, 285M synapses, 2,901 cores • using as benchmark example: • since improved run‐me by x80: 10 hours → 7.5 minutes • work in progress to improve efficiency by x60: real time, cores/3 S.J. van Albada, A.G. Rowley, A. Stokes, J. Senk, M. Hopkins, M. Schmidt, D.R. Lester, M. Diesmann, S.B. Furber, Performance comparison of the digital neuromorphic hardware SpiNNaker and the Neural network simulation software NEST for a full‐scale cortical microcircuit model. Frontiers 2018. 7 Computational Neuroscience • Serotonin modulates Pre Frontal Cortex • neurons express range of serotonin receptors • respond at different timescales • Dorsal Raphe Nucleus stimulation modulates brain rhythms • releases serotonin • Computational model to simulate serotonergic modulation • monitor local effects – firing rates • understand global effect on connected brain regions – oscillation in local field potential Celada, P., et al.