Introduction Actel Logic Modules Xilinx LCA Altera FLEX, Altera MAX

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Intel Quartus Prime Pro Edition User Guide: Partial Reconfiguration Send Feedback

Intel® Quartus® Prime Pro Edition User Guide Partial Reconfiguration Updated for Intel® Quartus® Prime Design Suite: 19.3 Subscribe UG-20136 | 2019.11.18 Send Feedback Latest document on the web: PDF | HTML Contents Contents 1. Creating a Partial Reconfiguration Design.......................................................................4 1.1. Partial Reconfiguration Terminology..........................................................................5 1.2. Partial Reconfiguration Process Sequence..................................................................6 1.3. Internal Host Partial Reconfiguration........................................................................ 7 1.4. External Host Partial Reconfiguration........................................................................ 9 1.5. Partial Reconfiguration Design Considerations............................................................9 1.5.1. Partial Reconfiguration Design Guidelines.................................................... 11 1.5.2. PR File Management.................................................................................12 1.5.3. Evaluating PR Region Initial Conditions....................................................... 16 1.5.4. Creating Wrapper Logic for PR Regions........................................................16 1.5.5. Creating Freeze Logic for PR Regions.......................................................... 17 1.5.6. Resetting the PR Region Registers.............................................................. 18 1.5.7. Promoting -

HB0085: Coreabc V3.7 Handbook

HB0085 Handbook CoreABC v3.7 Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not Microsemi Corporate Headquarters rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to One Enterprise, Aliso Viejo, independently determine suitability of any products and to test and verify the same. The information provided by Microsemi CA 92656 USA hereunder is provided “as is, where is” and with all faults, and the entire risk associated with such information is entirely Within the USA: +1 (800) 713-4113 with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP Outside the USA: +1 (949) 380-6100 rights, whether with regard to such information itself or anything described by such information. Information provided in this Fax: +1 (949) 215-4996 document is proprietary to Microsemi, and Microsemi reserves the right to make any changes to the information in this Email: [email protected] document or to any products and services at any time without notice. -

LATTICE SEMICONDUCTOR CORPORATION (Exact Name of Registrant As Specified in Its Charter)

3333 33 UNITED STATES SECURITIES AND EXCHANGE COMMISSION Washington, D.C. 20549 FORM 10-K (Mark One) ANNUAL REPORT PURSUANT TO SECTION 13 OR 15(d) OF THE SECURITIES EXCHANGE ACT OF 1934 FOR THE FISCAL YEAR ENDED JANUARY 3, 2009 or TRANSITION REPORT PURSUANT TO SECTION 13 OR 15(d) OF THE SECURITIES EXCHANGE ACT OF 1934 FOR THE TRANSITION PERIOD FROM TO Commission file number: 000-18032 LATTICE SEMICONDUCTOR CORPORATION (Exact name of registrant as specified in its charter) Delaware 93-0835214 (State of Incorporation) (I.R.S. Employer Identification Number) 5555 NE Moore Court Hillsboro, Oregon 97124-6421 (Address of principal executive offices) (Zip Code) Registrant’s telephone number, including area code: (503) 268-8000 Securities registered pursuant to Section 12(b) of the Act: (Title of Class) (Name of each exchange on which registered) Common Stock, $.01 par value NASDAQ Global Market Securities registered pursuant to Section 12(g) of the Act: None Indicate by check mark if the registrant is a well-known seasoned issuer, as defined in Rule 405 of the Securities Act. Yes No Indicate by check mark if the registrant is not required to file reports pursuant to Section 13 or Section 15(d) of the Act. Yes No Indicate by check mark whether the registrant (1) has filed all reports required to be filed by Section 13 or 15(d) of the Securities Exchange Act of 1934 during the preceding 12 months (or for such shorter period that the registrant was required to file such reports), and (2) has been subject to such filing requirements for the past 90 days. -

FPGA Design Security Issues: Using the Ispxpga® Family of Fpgas to Achieve High Design Security

White Paper FPGA Design Security Issues: Using the ispXPGA® Family of FPGAs to Achieve High Design Security December 2003 5555 Northeast Moore Court Hillsboro, Oregon 97124 USA Telephone: (503) 268-8000 FAX: (503) 268-8556 www.latticesemi.com WP1010 Using the ispXPGA Family of FPGAs to Lattice Semiconductor Achieve High Design Security Introduction In today’s complex systems, FPGAs are increasingly being used to replace functions traditionally performed by ASICs and even microprocessors. Ten years ago, the FPGA was at the fringe of most designs; today it is often at the heart. With FPGA technology taking gate counts into the millions, a trend accelerated by embedded ASIC-like functionality, the functions performed by the FPGA make an increasingly attractive target for piracy. Many tech- niques have been developed over the years to steal designs from all types of silicon chips. Special considerations must now be made when thinking about protecting valuable Intellectual Property (IP) implemented within the FPGA. The most common FPGA technology in use today is SRAM-based, which is fast and re-configurable, but must be re-configured every time the FPGA is powered up. Typically, an external PROM is used to hold the configuration data for the FPGA. The link between the PROM and FPGA represents a significant security risk. The configuration data is exposed and vulnerable to piracy while the device powers up. Using a non-volatile-based FPGA eliminates this security risk. Traditionally, non-volatile FPGAs were based on Antifuse technology that is secure, but very expensive to use due to its one-time programmability and higher manufacturing costs. -

CHAPTER 3: Combinational Logic Design with Plds

CHAPTER 3: Combinational Logic Design with PLDs LSI chips that can be programmed to perform a specific function have largely supplanted discrete SSI and MSI chips in board-level designs. A programmable logic device (PLD), is an LSI chip that contains a “regular” circuit structure, but that allows the designer to customize it for a specific application. PLDs sold in the market is not customized with specific functions. Instead, it is programmed by the purchaser to perform a function required by a particular application. PLD-based board-level designs often cost less than SSI/MSI designs for a number of reasons. Since PLDs provide more functionality per chip, the total chip and printed- circuit-board (PCB) area are less. Manufacturing costs are reduced in other ways too. A PLD-based board manufacturer needs to keep samples of few, “generic” PLD types, instead of many different MSI part types. This reduces overall inventory requirements and simplifies handling. PLD-type structures also appear as logic elements embedded in LSI chips, where chip count and board areas are not an issue. Despite the fact that a PLD may “waste” a certain number of gates, a PLD structure can actually reduce circuit cost because its “regular” physical structure may use less chip area than a “random logic” circuit. More importantly, the logic function performed by the PLD structure can often be “tweaked” in successive chip revisions by changing just one or a few metal mask layers that define signal connections in the array, instead of requiring a wholesale addition of gates and gate inputs and subsequent re-layout of a “random logic” design. -

Designing with Smartfusion Intelligent Mixed Signal Fpgas Webinar

™ Designing with SmartFusion Wendy Lockhart Sr. Manager, Design Solutions Agenda SmartFusion Overview SmartFusion Design Flows Embedded design FPGA design Analog design MSS Configurator and Embedded Example Ecosystem SmartFusion Design Hardware Actel Corporation © 2010 2 What is SmartFusion? Actel Corporation © 2010 3 SmartFusion: Innovative, Intelligent, Integration Proven FPGA fabric Complete ARM® Cortex™-M3 MCU subsystem...& it’s ‘hard’ Programmable analog In a flash-based device In production now! Actel Corporation © 2010 4 Why SmartFusion is a Smart Decision No-compromise integration Complete ARM Cortex-M3 subsystem running at 100 MHz Proven flash-based FPGA fabric Programmable high-voltage analog Full customization Design the exact system you need Hardware and software co-design IP protection FlashLock® technology with AES encryption Ease-of-use Optimized for hardware and software co-design Actel Corporation © 2010 5 No-Compromise FPGA Fabric Proven flash-based FPGA fabric 60,000 to 500,000 system gates 350 MHz system performance Embedded SRAMs and FIFOs Up to 128 FPGA I/Os Actel Corporation © 2010 6 No-Compromise Microcontroller Subsystem (MSS) 100 MHz 32-bit ARM Cortex-M3 processor Bus matrix with up to 16 Gbps throughput 10/100 Ethernet MAC SPI, I2C, UART, 32-bit Timers Up to 512 KB flash and 64 KB of SRAM External memory controller 8-channel DMA controller 32 GPIOs; Extendable via the FPGA Fabric Up to 41 MSS I/Os Actel Corporation © 2010 7 Programmable Analog Analog compute engine (ACE) -

Identify RTL Debugger Actel Edition Quick Start Guide, August 2008 Copyright and License Agreement

Identify® RTL Debugger Actel Edition Quick Start Guide August 2008 Synopsys, Inc. 600 West California Avenue Sunnyvale, CA 94086, USA (U.S.) +1 408 215-6000 direct (U.S.) +1 408 990-0263 fax www.synplicity.com Copyright and License Agreement Copyright and License Agreement Disclaimer of Warranty Synopsys, Inc. makes no representations or warranties, either expressed or implied, by or with respect to anything in this material, and shall not be liable for any implied warranties of merchantability or fitness for a particular purpose of for any indirect, special or consequential damages. Copyright Notice Copyright © 2008 Synopsys, Inc. All Rights Reserved. Synopsys software products contain certain confidential information of Synopsys, Inc. Use of this copyright notice is precautionary and does not imply publication or disclosure. No part of this material may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language in any form by any means without the prior written permission of Synopsys, Inc. While every precaution has been taken in the preparation of this material, Synopsys, Inc. assumes no responsibility for errors or omissions. This material and the features described herein are subject to change without notice. Trademarks Registered Trademarks (®) Synopsys, AMPS, Astro, Behavior Extracting Synthesis Technology, Cadabra, CATS, Certify, Design Compiler, DesignWare, Formality, HDL Analyst, HSPICE, Identify, iN-Phase, Leda, MAST, ModelTools, NanoSim, OpenVera, PathMill, Physical Compiler, PrimeTime, -

Ice40 Ultraplus Family Data Sheet

iCE40 UltraPlus™ Family Data Sheet FPGA-DS-02008 Version 1.4 August 2017 iCE40 UltraPlus™ Family Data Sheet Copyright Notice Copyright © 2017 Lattice Semiconductor Corporation. All rights reserved. The contents of these materials contain proprietary and confidential information (including trade secrets, copyright, and other Intellectual Property interests) of Lattice Semiconductor Corporation and/or its affiliates. All rights are reserved. You are permitted to use this document and any information contained therein expressly and only for bona fide non-commercial evaluation of products and/or services from Lattice Semiconductor Corporation or its affiliates; and only in connection with your bona fide consideration of purchase or license of products or services from Lattice Semiconductor Corporation or its affiliates, and only in accordance with the terms and conditions stipulated. Contents, (in whole or in part) may not be reproduced, downloaded, disseminated, published, or transferred in any form or by any means, except with the prior written permission of Lattice Semiconductor Corporation and/or its affiliates. Copyright infringement is a violation of federal law subject to criminal and civil penalties. You have no right to copy, modify, create derivative works of, transfer, sublicense, publicly display, distribute or otherwise make these materials available, in whole or in part, to any third party. You are not permitted to reverse engineer, disassemble, or decompile any device or object code provided herewith. Lattice Semiconductor Corporation reserves the right to revoke these permissions and require the destruction or return of any and all Lattice Semiconductor Corporation proprietary materials and/or data. Patents The subject matter described herein may contain one or more inventions claimed in patents or patents pending owned by Lattice Semiconductor Corporation and/or its affiliates. -

Overview of ESA Activities on FPGA Technology

Overview of ESA activities on FPGA technology Microelectronics Presentation Days David Merodio Codinachs European Space Agency Microelectronics Section (TEC-EDM) Microelectronics Presentation Days 30th April 2010 Slide 1/43 Acknowledgments Thanks to all colleagues who contributed from TEC-ED TEC-QCT TEC-QEC Catherine Morlet And all the industry, universities and institutes working on the mentioned activities Microelectronics Presentation Days 30th April 2010 Slide 2/43 Outline Introduction FPGA usage aspects Activities covering the different FPGA aspects European FPGAs SEE-related activities Static tools for FPGA radiation hardness assessment Dynamic tools for FPGA radiation hardness: Fault Injection Radiation testing Quality-related activity PPBI Application Reconfigurability-related activities Reconfigurable Regenerative Processor (Software Defined Radio) DRPM NPI Conclusions Microelectronics Presentation Days 30th April 2010 Slide 3/43 FPGA Introduction: aspects In the FPGA usage there are different aspects (not exhaustive list): (asp1) Capacity and performance (frequency and power consumption) » Related to the internal architecture and technology node used (asp2) Radiation hardness Others: » Addressed at different levels: » ITAR (International Traffic in Arms Process Regulations) Transistor/ Standard Cell The regulations are described in Register Transfer (RTL) Title 22 (Foreign Relations), Chapter I (Department of State), System Subchapter M of the Code of (asp3) Quality Federal Regulations. (asp4) Reconfigurability -

Architecture Description and Packing for Logic Blocks with Hierarchy, Modes and Complex Interconnect

Architecture Description and Packing for Logic Blocks with Hierarchy, Modes and Complex Interconnect Jason Luu, Jason Anderson, and Jonathan Rose The Edward S. Rogers Sr. Department of Electrical and Computer Engineering University of Toronto, Toronto, ON, Canada jluu|janders|[email protected] SRHI D SRLO Reset Type INIT1 Q CE Sync/Async ABSTRACT COUT INIT0 CK SR FF/LAT DX The development of future FPGA fabrics with more sophis- DMUX DI2 D6:1 A6:A1 W6:W1 D ticated and complex logic blocks requires a new CAD flow D O6 FF/LAT O5 DX INIT1 Q DQ D INIT0 CK DI1 SRHI that permits the expression of that complexity and the abil- CE SRLO WEN MC31 SRHI D SRLO CK Q SR DI INIT1 CE INIT0 ity to synthesize to it. In this paper, we present a new logic CK SR CX CMUX block description language that can depict complex intra- DI2 C6:1 A6:A1 W6:W1 C C O6 block interconnect, hierarchy and modes of operation. These FF/LAT O5 CX INIT1 Q CQ D INIT0 CK DI1 CE SRHI SRLO features are necessary to support modern and future FPGA WEN MC31 SRHI CK D SRLO SR CI INIT1 Q CE INIT0 complex soft logic blocks, memory and hard blocks. The key CK SR BX BMUX part of the CAD flow associated with this complexity is the DI2 B6:1 A6:A1 W6:W1 B B O6 packer, which takes the logical atomic pieces of the complex O5 FF/LAT BX INIT1 Q BQ D DI1 INIT0 CK CE SRHI SRLO WEN MC31 SRHI CK blocks and groups them into whole physical entities. -

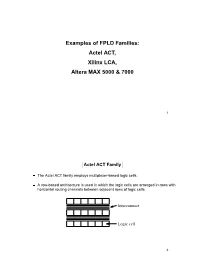

Examples of FPLD Families: Actel ACT, Xilinx LCA, Altera MAX 5000 & 7000

Examples of FPLD Families: Actel ACT, Xilinx LCA, Altera MAX 5000 & 7000 1 Actel ACT Family ¯ The Actel ACT family employs multiplexer-based logic cells. ¯ A row-based architecture is used in which the logic cells are arranged in rows with horizontal routing channels between adjacent rows of logic cells. Interconnect Logic cell 2 ACT 1 Logic Modules ¯ ACT 1 FPGAs use a single type of logic module. Logic Module Logic Module Logic Module M1 A0 F A0 D Actel ACT 0 F1 A1 0 M3 F1 A1 1 '1' 1 SA F1 S F SA 0 F F2 C 0 M2 1 B0 1 B0 S D 0 B1 0 F2 B1 1 F2 '1' 1 SB (a) S SB S3 A S0 S3 S0 '0' S1 O1 S1 O1 B F=(A·B)+(B'·C)+D (b) (c) (d) (a) An Actel FPGA. (b) An ACT 1 logic module. (c) An implementation of an ACT 1 logic module using pass transistors. (d) An example of function implementation by an ACT 1 logic module. 3 ACT 2 and ACT 3 Logic Modules ¯ Both ACT 2 and ACT 3 FPGAs use two types of logic module. C-Module S-Module (ACT 2) S-Module (ACT 3) D00 D00 SED00 SE D01 D01 D01 D10 YOUTD10 YQD10 YQ D11 D11 D11 A1 A1 A1 B1 S1 B1 S1 B1 S1 A0 A0 A0 B0 S0 CLR S0 B0 S0 CLR CLK CLK (a) (b) (c) SE (sequential element) SE 1 1 D D Q Q Z Z D 0 0 Q CLK C2 S S C1 master slave C2 latch latch CLR CLR C1 CLR combinational logic for clock flip-flop macro and clear D 1D Q CLK C1 (d) (e) (a) The C-module used by both ACT 2 and ACT 3 FPGAs. -

Efpgas : Architectural Explorations, System Integration & a Visionary Industrial Survey of Programmable Technologies Syed Zahid Ahmed

eFPGAs : Architectural Explorations, System Integration & a Visionary Industrial Survey of Programmable Technologies Syed Zahid Ahmed To cite this version: Syed Zahid Ahmed. eFPGAs : Architectural Explorations, System Integration & a Visionary Indus- trial Survey of Programmable Technologies. Micro and nanotechnologies/Microelectronics. Université Montpellier II - Sciences et Techniques du Languedoc, 2011. English. tel-00624418 HAL Id: tel-00624418 https://tel.archives-ouvertes.fr/tel-00624418 Submitted on 16 Sep 2011 HAL is a multi-disciplinary open access L’archive ouverte pluridisciplinaire HAL, est archive for the deposit and dissemination of sci- destinée au dépôt et à la diffusion de documents entific research documents, whether they are pub- scientifiques de niveau recherche, publiés ou non, lished or not. The documents may come from émanant des établissements d’enseignement et de teaching and research institutions in France or recherche français ou étrangers, des laboratoires abroad, or from public or private research centers. publics ou privés. Université Montpellier 2 (UM2) École Doctorale I2S LIRMM (Laboratoire d'Informatique, de Robotique et de Microélectronique de Montpellier) Domain: Microelectronics PhD thesis report for partial fulfillment of requirements of Doctorate degree of UM2 Thesis conducted in French Industrial PhD (CIFRE) framework between: Menta & LIRMM lab (Dec.2007 – Feb. 2011) in Montpellier, FRANCE “eFPGAs: Architectural Explorations, System Integration & a Visionary Industrial Survey of Programmable Technologies” eFPGAs: Explorations architecturales, integration système, et une enquête visionnaire industriel des technologies programmable by Syed Zahid AHMED Presented and defended publically on: 22 June 2011 Jury: Mr. Guy GOGNIAT Prof. at STICC/UBS (Lorient, FRANCE) President Mr. Habib MEHREZ Prof. at LIP6/UPMC (Paris, FRANCE) Reviewer Mr.