By S.David Paul Generation (1642-1945) Mechanical

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

8088 8-Bit Hmos Microprocessor 8088 8088-2

8088 8-BIT HMOS MICROPROCESSOR 8088/8088-2 Y 8-Bit Data Bus Interface Y Byte, Word, and Block Operations Y 16-Bit Internal Architecture Y 8-Bit and 16-Bit Signed and Unsigned Arithmetic in Binary or Decimal, Y Direct Addressing Capability to 1 Mbyte of Memory Including Multiply and Divide Y Two Clock Rates: Y Direct Software Compatibility with 8086 CPU Ð 5 MHz for 8088 Ð 8 MHz for 8088-2 Y 14-Word by 16-Bit Register Set with Symmetrical Operations Y Available in EXPRESS Ð Standard Temperature Range Y 24 Operand Addressing Modes Ð Extended Temperature Range The Intel 8088 is a high performance microprocessor implemented in N-channel, depletion load, silicon gate technology (HMOS-II), and packaged in a 40-pin CERDIP package. The processor has attributes of both 8- and 16-bit microprocessors. It is directly compatible with 8086 software and 8080/8085 hardware and periph- erals. 231456±2 Figure 2. 8088 Pin Configuration 231456±1 Figure 1. 8088 CPU Functional Block Diagram August 1990 Order Number: 231456-006 8088 Table 1. Pin Description The following pin function descriptions are for 8088 systems in either minimum or maximum mode. The ``local bus'' in these descriptions is the direct multiplexed bus interface connection to the 8088 (without regard to additional bus buffers). Symbol Pin No. Type Name and Function AD7±AD0 9±16 I/O ADDRESS DATA BUS: These lines constitute the time multiplexed memory/IO address (T1) and data (T2, T3, Tw, T4) bus. These lines are active HIGH and float to 3-state OFF during interrupt acknowledge and local bus ``hold acknowledge''. -

Computer Organization and Architecture Designing for Performance Ninth Edition

COMPUTER ORGANIZATION AND ARCHITECTURE DESIGNING FOR PERFORMANCE NINTH EDITION William Stallings Boston Columbus Indianapolis New York San Francisco Upper Saddle River Amsterdam Cape Town Dubai London Madrid Milan Munich Paris Montréal Toronto Delhi Mexico City São Paulo Sydney Hong Kong Seoul Singapore Taipei Tokyo Editorial Director: Marcia Horton Designer: Bruce Kenselaar Executive Editor: Tracy Dunkelberger Manager, Visual Research: Karen Sanatar Associate Editor: Carole Snyder Manager, Rights and Permissions: Mike Joyce Director of Marketing: Patrice Jones Text Permission Coordinator: Jen Roach Marketing Manager: Yez Alayan Cover Art: Charles Bowman/Robert Harding Marketing Coordinator: Kathryn Ferranti Lead Media Project Manager: Daniel Sandin Marketing Assistant: Emma Snider Full-Service Project Management: Shiny Rajesh/ Director of Production: Vince O’Brien Integra Software Services Pvt. Ltd. Managing Editor: Jeff Holcomb Composition: Integra Software Services Pvt. Ltd. Production Project Manager: Kayla Smith-Tarbox Printer/Binder: Edward Brothers Production Editor: Pat Brown Cover Printer: Lehigh-Phoenix Color/Hagerstown Manufacturing Buyer: Pat Brown Text Font: Times Ten-Roman Creative Director: Jayne Conte Credits: Figure 2.14: reprinted with permission from The Computer Language Company, Inc. Figure 17.10: Buyya, Rajkumar, High-Performance Cluster Computing: Architectures and Systems, Vol I, 1st edition, ©1999. Reprinted and Electronically reproduced by permission of Pearson Education, Inc. Upper Saddle River, New Jersey, Figure 17.11: Reprinted with permission from Ethernet Alliance. Credits and acknowledgments borrowed from other sources and reproduced, with permission, in this textbook appear on the appropriate page within text. Copyright © 2013, 2010, 2006 by Pearson Education, Inc., publishing as Prentice Hall. All rights reserved. Manufactured in the United States of America. -

Lecture Notes in Assembly Language

Lecture Notes in Assembly Language Short introduction to low-level programming Piotr Fulmański Łódź, 12 czerwca 2015 Spis treści Spis treści iii 1 Before we begin1 1.1 Simple assembler.................................... 1 1.1.1 Excercise 1 ................................... 2 1.1.2 Excercise 2 ................................... 3 1.1.3 Excercise 3 ................................... 3 1.1.4 Excercise 4 ................................... 5 1.1.5 Excercise 5 ................................... 6 1.2 Improvements, part I: addressing........................... 8 1.2.1 Excercise 6 ................................... 11 1.3 Improvements, part II: indirect addressing...................... 11 1.4 Improvements, part III: labels............................. 18 1.4.1 Excercise 7: find substring in a string .................... 19 1.4.2 Excercise 8: improved polynomial....................... 21 1.5 Improvements, part IV: flag register ......................... 23 1.6 Improvements, part V: the stack ........................... 24 1.6.1 Excercise 12................................... 26 1.7 Improvements, part VI – function stack frame.................... 29 1.8 Finall excercises..................................... 34 1.8.1 Excercise 13................................... 34 1.8.2 Excercise 14................................... 34 1.8.3 Excercise 15................................... 34 1.8.4 Excercise 16................................... 34 iii iv SPIS TREŚCI 1.8.5 Excercise 17................................... 34 2 First program 37 2.1 Compiling, -

CISC Processor - Intel X86

Architecture of Computers and Parallel Systems Part 4: Intel x86 History Ing. Petr Olivka [email protected] Department of Computer Science FEI VSB-TUO Architecture of Computers and Parallel Systems Part 4: Intel x86 History Ing. Petr Olivka [email protected] Department of Computer Science FEI VSB-TUO Architecture of Computers and Parallel Systems Part 4: Intel x86 History Ing. Petr Olivka [email protected] Department of Computer Science FEI VSB-TUO CISC Processor - Intel x86 This chapter will introduce the CISC processors evolution. We will try to illustrate the history on one typical processor, because the comparison of multiple processors simultaneously would not be clear for readers. But the selection of one typical processor is complicated due to a variety of products and manufactures in the past 30 years. We have decided to describe in this presentation one of the best- known and longest mass-produced processors in existence. We definitely do not want to say that it is the best technology or that these are processors with the highest performance! The Intel x86 processors are the selected product line. Intel 8080 (Year-Technology-Transistors-Frequency-Data bus-Address Bus) Y: 1974 T: NMOS 6μm Tr: 6000 F: 2MHz D: 8b A: 16b This 8 bit processor is not directly the first member of x86 series, but it can not be skipped. It is one of the first commercially successful microprocessors. This microprocessor became the basis for a number of the first single-board computers and its instruction set inspired other manufacturers to develop 8-bit processors. -

How Microprocessors Work E 1 of 64 ZM

How Microprocessors Work e 1 of 64 ZM How Microprocessors Work ZAHIDMEHBOOB +923215020706 [email protected] 2003 BS(IT) PRESTION UNIVERSITY How Microprocessors Work The computer you are using to read this page uses a microprocessor to do its work. The microprocessor is the heart of any normal computer, whether it is a desktop machine, a server or a laptop. The microprocessor you are using might be a Pentium, a K6, a PowerPC, a Sparc or any of the many other brands and types of microprocessors, but they all do approximately the same thing in approximately the same way. If you have ever wondered what the microprocessor in your computer is doing, or if you have ever wondered about the differences between types of microprocessors, then read on. Microprocessor History A microprocessor -- also known as a CPU or central processing unit -- is a complete computation engine that is fabricated on a single chip. The first microprocessor was the Intel [email protected] +923215020706 (2003) How Microprocessors Work e 2 of 64 ZM 4004, introduced in 1971. The 4004 was not very powerful -- all it could do was add and subtract, and it could only do that 4 bits at a time. But it was amazing that everything was on one chip. Prior to the 4004, engineers built computers either from collections of chips or from discrete components (transistors wired one at a time). The 4004 powered one of the first portable electronic calculators. The first microprocessor to make it into a home computer was the Intel 8080, a complete 8- bit computer on one chip, introduced in 1974. -

A Compiler Target Model for Line Associative Registers

University of Kentucky UKnowledge Theses and Dissertations--Electrical and Computer Engineering Electrical and Computer Engineering 2019 A Compiler Target Model for Line Associative Registers Paul S. Eberhart University of Kentucky, [email protected] Digital Object Identifier: https://doi.org/10.13023/etd.2019.141 Right click to open a feedback form in a new tab to let us know how this document benefits ou.y Recommended Citation Eberhart, Paul S., "A Compiler Target Model for Line Associative Registers" (2019). Theses and Dissertations--Electrical and Computer Engineering. 138. https://uknowledge.uky.edu/ece_etds/138 This Master's Thesis is brought to you for free and open access by the Electrical and Computer Engineering at UKnowledge. It has been accepted for inclusion in Theses and Dissertations--Electrical and Computer Engineering by an authorized administrator of UKnowledge. For more information, please contact [email protected]. STUDENT AGREEMENT: I represent that my thesis or dissertation and abstract are my original work. Proper attribution has been given to all outside sources. I understand that I am solely responsible for obtaining any needed copyright permissions. I have obtained needed written permission statement(s) from the owner(s) of each third-party copyrighted matter to be included in my work, allowing electronic distribution (if such use is not permitted by the fair use doctrine) which will be submitted to UKnowledge as Additional File. I hereby grant to The University of Kentucky and its agents the irrevocable, non-exclusive, and royalty-free license to archive and make accessible my work in whole or in part in all forms of media, now or hereafter known. -

Communication Theory II

Microprocessor (COM 9323) Lecture 2: Review on Intel Family Ahmed Elnakib, PhD Assistant Professor, Mansoura University, Egypt Feb 17th, 2016 1 Text Book/References Textbook: 1. The Intel Microprocessors, Architecture, Programming and Interfacing, 8th edition, Barry B. Brey, Prentice Hall, 2009 2. Assembly Language for x86 processors, 6th edition, K. R. Irvine, Prentice Hall, 2011 References: 1. Computer Architecture: A Quantitative Approach, 5th edition, J. Hennessy, D. Patterson, Elsevier, 2012. 2. The 80x86 Family, Design, Programming and Interfacing, 3rd edition, Prentice Hall, 2002 3. The 80x86 IBM PC and Compatible Computers, Assembly Language, Design, and Interfacing, 4th edition, M.A. Mazidi and J.G. Mazidi, Prentice Hall, 2003 2 Lecture Objectives 1. Provide an overview of the various 80X86 and Pentium family members 2. Define the contents of the memory system in the personal computer 3. Convert between binary, decimal, and hexadecimal numbers 4. Differentiate and represent numeric and alphabetic information as integers, floating-point, BCD, and ASCII data 5. Understand basic computer terminology (bit, byte, data, real memory system, protected mode memory system, Windows, DOS, I/O) 3 Brief History of the Computers o1946 The first generation of Computer ENIAC (Electrical and Numerical Integrator and Calculator) was started to be used based on the vacuum tube technology, University of Pennsylvania o1970s entire CPU was put in a single chip. (1971 the first microprocessor of Intel 4004 (4-bit data bus and 2300 transistors and 45 instructions) 4 Brief History of the Computers (cont’d) oLate 1970s Intel 8080/85 appeared with 8-bit data bus and 16-bit address bus and used from traffic light controllers to homemade computers (8085: 246 instruction set, RISC*) o1981 First PC was introduced by IBM with Intel 8088 (CISC**: over 20,000 instructions) microprocessor oMotorola emerged with 6800. -

Open PDF in New Window

BEST AVAILABLE COPY i The pur'pose of this DIGITAL COMPUTER Itop*"°a""-'"""neesietter' YNEWSLETTER . W OFFICf OF NIVAM RUSEARCMI • MATNEMWTICAL SCIENCES DIVISION Vol. 9, No. 2 Editors: Gordon D. Goldstein April 1957 Albrecht J. Neumann TABLE OF CONTENTS It o Page No. W- COMPUTERS. U. S. A. "1.Air Force Armament Center, ARDC, Eglin AFB, Florida 1 2. Air Force Cambridge Research Center, Bedford, Mass. 1 3. Autonetics, RECOMP, Downey, Calif. 2 4. Corps of Engineers, U. S. Army 2 5. IBM 709. New York, New York 3 6. Lincoln Laboratory TX-2, M.I.T., Lexington, Mass. 4 7. Litton Industries 20 and 40 DDA, Beverly Hills, Calif. 5 8. Naval Air Test Centcr, Naval Air Station, Patuxent River, Maryland 5 9. National Cash Register Co. NC 304, Dayton, Ohio 6 10. Naval Air Missile Test Center, RAYDAC, Point Mugu, Calif. 7 11. New York Naval Shipyard, Brooklyn, New York 7 12. Philco, TRANSAC. Philadelphia, Penna. 7 13. Western Reserve Univ., Cleveland, Ohio 8 COMPUTING CENTERS I. Univ. of California, Radiation Lab., Livermore, Calif. 9 2. Univ. of California, SWAC, Los Angeles, Calif. 10 3. Electronic Associates, Inc., Princeton Computation Center, Princeton, New Jersey 10 4. Franklin Institute Laboratories, Computing Center, Philadelphia, Penna. 11 5. George Washington Univ., Logistics Research Project, Washington, D. C. 11 6. M.I.T., WHIRLWIND I, Cambridge, Mass. 12 7. National Bureau of Standards, Applied Mathematics Div., Washington, D.C. 12 8. Naval Proving Ground, Naval Ordnance Computation Center, Dahlgren, Virgin-.a 12 9. Ramo Wooldridge Corp., Digital Computing Center, Los Angeles, Calif. -

Hereby the Screen Stands in For, and Thereby Occludes, the Deeper Workings of the Computer Itself

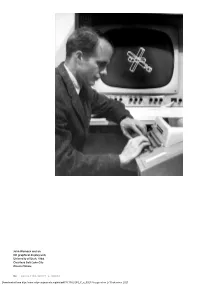

John Warnock and an IDI graphical display unit, University of Utah, 1968. Courtesy Salt Lake City Deseret News . 24 doi:10.1162/GREY_a_00233 Downloaded from http://www.mitpressjournals.org/doi/pdf/10.1162/GREY_a_00233 by guest on 27 September 2021 The Random-Access Image: Memory and the History of the Computer Screen JACOB GABOURY A memory is a means for displacing in time various events which depend upon the same information. —J. Presper Eckert Jr. 1 When we speak of graphics, we think of images. Be it the windowed interface of a personal computer, the tactile swipe of icons across a mobile device, or the surreal effects of computer-enhanced film and video games—all are graphics. Understandably, then, computer graphics are most often understood as the images displayed on a computer screen. This pairing of the image and the screen is so natural that we rarely theorize the screen as a medium itself, one with a heterogeneous history that develops in parallel with other visual and computa - tional forms. 2 What then, of the screen? To be sure, the computer screen follows in the tradition of the visual frame that delimits, contains, and produces the image. 3 It is also the skin of the interface that allows us to engage with, augment, and relate to technical things. 4 But the computer screen was also a cathode ray tube (CRT) phosphorescing in response to an electron beam, modified by a grid of randomly accessible memory that stores, maps, and transforms thousands of bits in real time. The screen is not simply an enduring technique or evocative metaphor; it is a hardware object whose transformations have shaped the ma - terial conditions of our visual culture. -

Computer Oral History Collection, 1969-1973, 1977

Computer Oral History Collection, 1969-1973, 1977 Interviewee: Morris Rubinoff Interviewer: Richard R. Mertz Date: May 17, 1971 Repository: Archives Center, National Museum of American History MERTZ: Professor Rubinoff, would you care to describe your early training and background and influences. RUBINOFF: The early training is at the University of Toronto in mathematics and physics as an undergraduate, and then in physics as a graduate. The physics was tested in research projects during World War II, which was related to the proximity fuse. In fact, a strong interest in computational techniques, numerical methods was developed then, and also in switching devices because right after the War the proximity fuse techniques were used to make measurements of the angular motions of projectiles in flight. To do this it was necessary to calculate trajectories. Calculating trajectories is an interesting problem since it relates to what made the ENIAC so interesting at Aberdeen. They were using it for calculating trajectories, unknown to me at the time. We were calculating trajectories by hand at the University of Toronto using a method which is often referred to as the Richardson method. So the whole technique of numerical analysis and numerical computation got to be very intriguing to me. MERTZ: Was this done on a Friden [or] Marchant type calculator? RUBINOFF: MERTZ: This was a War project at the University of Toronto? RUBINOFF: This was a post-War project. It was an outgrowth of a war project on proximity fuse. It was supported by the Canadian Army who were very interested in finding out what made liquid filled shell tumble rather than fly properly when they went through space. -

Computer Architectures an Overview

Computer Architectures An Overview PDF generated using the open source mwlib toolkit. See http://code.pediapress.com/ for more information. PDF generated at: Sat, 25 Feb 2012 22:35:32 UTC Contents Articles Microarchitecture 1 x86 7 PowerPC 23 IBM POWER 33 MIPS architecture 39 SPARC 57 ARM architecture 65 DEC Alpha 80 AlphaStation 92 AlphaServer 95 Very long instruction word 103 Instruction-level parallelism 107 Explicitly parallel instruction computing 108 References Article Sources and Contributors 111 Image Sources, Licenses and Contributors 113 Article Licenses License 114 Microarchitecture 1 Microarchitecture In computer engineering, microarchitecture (sometimes abbreviated to µarch or uarch), also called computer organization, is the way a given instruction set architecture (ISA) is implemented on a processor. A given ISA may be implemented with different microarchitectures.[1] Implementations might vary due to different goals of a given design or due to shifts in technology.[2] Computer architecture is the combination of microarchitecture and instruction set design. Relation to instruction set architecture The ISA is roughly the same as the programming model of a processor as seen by an assembly language programmer or compiler writer. The ISA includes the execution model, processor registers, address and data formats among other things. The Intel Core microarchitecture microarchitecture includes the constituent parts of the processor and how these interconnect and interoperate to implement the ISA. The microarchitecture of a machine is usually represented as (more or less detailed) diagrams that describe the interconnections of the various microarchitectural elements of the machine, which may be everything from single gates and registers, to complete arithmetic logic units (ALU)s and even larger elements. -

Museum Monthly Reports

.J LI j' .. ... ' .J t / . oJ , EXHIBITS AND AR~HJVES D::::PhRTIV1Et\'Y' -- OCTOBER '83 REPORT STAFFING: "'1eredith Stelling, Cooro i na tor Gregory Welch, Operations Manager/Research Bill Wisheart , Registr~r/Photo and Video Archives Beth Par kh urst, Re search RECENT ARTIFACT AC0UISITIONS (since October 1, 1983): X239. 83 Monr oe High Speed Adding Calculator, gift of Lee Swanson. X240.83 Vari-typer, gift of Lee Swanson. X241.83 HP-65 Programmable Calculator, gift of Stephen and Barbara Gross. X241.83 BIAX memory cores, gift of G.B. Westrom. X243.83 - X259.83 The University of Illinios Department of Computer Science Collection of Drawing Instruments, Slide Rules, Calculators and Circuit Boards. X243.83 Smith's Im proved Protactor. 7 X246.83 ILLIAC III Ci rcuit Boards. /o X2~7. 83 ILLIAC II Ci r cuit Board. /0 X250.e3 Keuffel & Esser Cylind rical Slide Rule. ? X260.83 - X274.83 The SAGE AN/SFQ-7 computer. Gi ft of The National 1'1useum of Science and Technology, Ontario. X2r,r . 83 1/2 naste r console ~ C5l5U X2f,} . [;3 "· ,o.onet j c Dr U':l Uni t. 5. (f(5D ~ I X2',2 . P3 IRM 7J8 printer. /C1t7 X2 G ~ . 83.1':>, - E 5 RAda r Operato r's Consoles. ~~ 107.J7.J X7r.t. £'3.Z>. - E 5 Auxiliary Consoles. -------6?:!O/02J7..) X2C,S . 83?l, - E 5 Operator's Chairs. 50 I X7 :- F. f' 3 I RIv! 2 G Car d Pu n c h . / CJ7) X767 . S3 IB"'1 723 Ca rd Recorne r.