2 Ghz to 67 Ghz, 500 Mhz Bandwidth Envelope Detector ADL6012

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Energy-Detecting Receivers for Wake-Up Radio Applications

Energy-Detecting Receivers for Wake-Up Radio Applications Vivek Mangal Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy under the Executive Committee of the Graduate School of Arts and Sciences COLUMBIA UNIVERSITY 2020 © 2019 Vivek Mangal All Rights Reserved Abstract Energy-Detecting Receivers for Wake-Up Radio Applications Vivek Mangal In an energy-limited wireless sensor node application, the main transceiver for communication has to operate in deep sleep mode when inactive to prolong the node battery lifetime. Wake-up is among the most efficient scheme which uses an always ON low-power receiver called the wake-up receiver to turn ON the main receiver when required. Energy-detecting receivers are the best fit for such low power operations. This thesis discusses the energy-detecting receiver design; challenges; techniques to enhance sensitivity, selectivity; and multi-access operation. Self-mixers instead of the conventional envelope detectors are proposed and proved to be op- timal for signal detection in these energy-detection receivers. A fully integrated wake-up receiver using the self-mixer in 65 nm LP CMOS technology has a sensitivity of −79.1 dBm at 434 MHz. With scaling, time-encoded signal processing leveraging switching speeds have become attractive. Baseband circuits employing time-encoded matched filter and comparator with DC offset compen- sation loop are used to operate the receiver at 420 pW power. Another prototype at 1.016 GHz is sensitive to −74 dBm signal while consuming 470 pW. The proposed architecture has 8 dB better sensitivity at 10 dB lower power consumption across receiver prototypes. -

EE426/506 Class Notes 4/23/2015 John Stensby

EE426/506 Class Notes 4/23/2015 John Stensby Chapter 2: Basic Modulation Techniques In most communication systems, the modulated signal has the form xcc (t) A(t)cos[ t (t)], (2-1) where c is known as the carrier frequency, A(t) is the envelope and (t) is the phase. Amplitude A(t) and phase (t) may depend on message m(t). When A(t) depends linearly on the message, and is a constant independent of m, we have linear modulation. When (t) depends on m(t), we have nonlinear modulation. Linear Modulation Double Sideband (DSB) is the first form of linear modulation we will consider. The general form of a DSB signal is x(t)Am(t)cos[tDSB cc0 ], (2-2) where Ac and are constants. For convenience, we will assume that = 0. Figures 2-1a through 2-1c depict a block diagram of a DSB modulator, a sinusoidal message m and the DSB time domain wave form xDSB(t), respectively. Note that every sign change in m(t) results in a ° 180 phase shift in the transmitted signal xDSB(t). DSB is very popular when used to transmit digital data. In this application, m(t) is a digital waveform that switches between +1 and -1 volts. Hence, m(t) switches the phase of the transmitted carrier by radians. For this reason, for a ±1 binary message, the modulation is called phase-shift keying. The Fourier transform of xDSB is A X(j)x(t)M(jj)M(jj)F c , (2-3) DSB DSB2 c c Latest Updates at http://www.ece.uah.edu/courses/ee426/ 2-1 EE426/506 Class Notes 4/23/2015 John Stensby m(t) a) xDSB(t) = Acm(t)cosct Accosct m(t) b) t (t) DSB x c) t Figure 2-1: a) Block diagram of a DSB modulator. -

Signi\L PURITY CONS IDERI\TIONS for FREQUEN<:Y Sn1 Tiles I ZED Llel\DEND EQU I Pr1ent David L. Kel:Na General Instrument

SIGNi\L PURITY CONS IDERI\TIONS FOR FREQUEN<:Y Sn1 TilES I ZED llEl\DEND EQU I Pr1ENT David L. Kel:na General Instrument, Jerrold Division ABSTRACT BASIC OVERVIEW OF THE PLL As cabl~ television system band Before we evoluate the system for wirlths increase and frequency plans pro its noise performance, let us first re liferate, more manufacturers are turning view the b~sic operation of a chase to synth~sized frequency agile head~nd locked loop. A simple phase-locked loop channel converters. Uith this new ap consists of a voltage controlled oscil proach using phased lo~ked loops and dual lator, or VCO, a digital divider, a chase conversion come spurious signals and detector, a reference frequency sour~e, nois~ sources not encountered before in and an integrator or loop filter. Figure crystal controlled channel converters. 1 represents such a system. Important characteristics of these These system components function ~s headend converters including phas~ noise, a s~rvo loop sue~ that when the·vco is spurious sign3ls generated by the compar phase-locked to the reference, the output ison frequ~ncy, and residual frequency frequency and phase of the digital divi a~d phase modulation, are evaluated for der is equal to the frequency and phase their subjective impact on the output of the referenc~. This makes the average signal to the cable. D3ta is presented output of the phase detector zero and, which shows the correlation between sub therefore, the output of the loop filter jective picture degradation and measured remains unchanged. Should a disturbance headend synthesizer noise contribution. -

Amplitude Modulation “AM” with Envelope Detector

Amplitude Modulation “AM” with Envelope Detector Large S/N limit m1< s(t) ≅ sin ωm t ≤ 1 Recei ved = y(t) = Ac [1 + m s( t)] cos ωc t + nc (t)cos ωc t + ns (t)s in ωct j ωct = Re {Y (t)e } slowly varying y, low-pass filtered (envelope) “overmodulation” = distortion (“undermodulation = wasted power) Lec 16b.6-1 2/2/01 T1 Amplitude Modulation “AM” with Envelope Detector Recei ved = y(t) = Ac [1 + m s( t)] cos ωc t + nc (t)cos ωc t + ns (t)s in ωct j ωct = Re {Y (t)e } slowly varying Im {Y (t)} Y(f ) 2W Y(t) ns(t) n(t) R e {Y(t) } f 0 0 fc A [1 + m s(t)] nc(t) N = kT c o 2 Lec 16b.6-2 2/2/01 T2 Amplitude Modulation “AM” with Envelope Detector Im {Y (t)} Y(f ) 2W Y(t) ns(t) n(t) R e {Y(t) } f 0 0 fc A [1 + m s(t)] nc(t) N = kT c o 2 Y(t) ≅ A [1 + m s(t)] + n (t) N c c envelope = detected signal + noise 2 2 2 2 2 Note: 4WNo = nc cos ωc t + ns sin ωc t = nc 222 Sout 222 2 Ac ms (t) ≅ Ac m s (t) nc (t) = Nout 4WNo Lec 16b.6-3 2/2/01 T3 Amplitude Modulation “AM” with Envelope Detector 222 Sout 222 2 Ac ms (t) ≅ Ac m s (t) nc (t) = Nout 4WNo 2 2 A 2 (1 + m s(t)) Sin ( c ) 2 ≅ where Sin = y signal(t) Nin 4WNo 22 ∆ SNi i 1m+ s (t) 11+ 2 Noi se figure FAM = = ≥ = 3 2 ⇒ FAM ≥ 3 2 SNo o 2m 22s 1 provided that Ac >> nc (large S/N limit) Lec 16b.6-4 2/2/01 T4 AM Performance (small S/N limit) Im {Y } φ (t) n A1c [ + m s(t)] n(t) ≅ Ac [1 + m s( t)] cos φn (t) φn (t) R e {}Y Y(t) ≅ n(t) + A cos φ (t) + A m s( t)cos φ (t) c n c n multiplicative noise! Want Sin Nin ≥ 10 for fully i ntel ligibl e AM ⇒ "AM threshold" ( i.e. -

Low-Power RFED Wake-Up Receiver Design for Low-Cost Wireless Sensor Network Applications

sensors Article Low-Power RFED Wake-Up Receiver Design for Low-Cost Wireless Sensor Network Applications David Galante-Sempere , Dailos Ramos-Valido, Sunil Lalchand Khemchandani and Javier del Pino * Institute for Applied Microelectronics (IUMA), University of Las Palmas de Gran Canaria (ULPGC), 35017 Las Palmas de Gran Canaria, Spain; [email protected] (D.G.-S.); [email protected] (D.R.-V.); [email protected] (S.L.K.) * Correspondence: [email protected] Received: 28 September 2020; Accepted: 6 November 2020; Published: 10 November 2020 Abstract: The development of wake-up receivers (WuR) has recently received a lot of interest from both academia and industry researchers, primarily because of their major impact on the improvement of the performance of wireless sensor networks (WSNs). In this paper, we present the development of three different radiofrequency envelope detection (RFED) based WuRs operating at the 868 MHz industrial, scientific and medical (ISM) band. These circuits can find application in densely populated WSNs, which are fundamental components of Internet-of-Things (IoT) or Internet-of-Everything (IoE) applications. The aim of this work is to provide circuits with high integrability and a low cost-per-node, so as to facilitate the implementation of sensor nodes in low-cost IoT applications. In order to demonstrate the feasibility of implementing a WuR with commercially available off-chip components, the design of an RFED WuR in a PCB mount is presented. The circuit is validated in a real scenario by testing the WuR in a system with a pattern recognizer (AS3933), an MCU (MSP430G2553 from TI), a transceiver (CC1101 from TI) and a T/R switch (ADG918). -

Easy Fourier Analysis

SpectrumDCInformationSignal term at 2won signal cthe positivenegative Half is up This half is .3 x-axis .5 shifted. down shifted. Charan Langton, TheEditor Carrier fm = -1 fm = 1 -9 9 -9, fc-9, -8, = -8, -8-7 -7 -7 7, fc7 7,8,= 8 8,9 9 -9, -8, -7 7, 8, 9 SIGNAL PROCESSING & SIMULATION NEWSLETTER Baseband, Passband Signals and Amplitude Modulation The most salient feature of information signals is that they are generally low frequency. Sometimes this is due to the nature of data itself such as human voice which has frequency components from 300 Hz to app. 20 KHz. Other times, such as data from a digital circuit inside a computer, the low rates are due to hardware limitations. Due to their low frequency content, the information signals have a spectrum such as that in the figure below. There are a lot of low frequency components and the one-sided spectrum is located near the zero frequency. .......... Figure 1 - The spectrum of an information signal is usually limited to low frequencies The hypothetical signal above has four sinusoids, all of which are fairly close to zero. The frequency range of this signal extends from zero to a maximum frequency of fm. We say that this signal has a bandwidth of fm. In the time domain this 4 component signal may looks as shown in Figure 2. Figure 2 - Time domain low frequency information signal Now let’s modulate this signal, which means we are going to transfer it to a higher (usually much higher) frequency. Just as information signals are characterized by their low frequency, the transmission medium, or carriers are characterized by their high frequency. -

A Novel Wide-Band Envelope Detector

RMO3B-5 A Novel Wide-Band Envelope Detector Yanping Zhou, Guochi Huang, Sangwook Nam* and Byung-Sung Kim School of Information and Communication, Sungkyunkwan University, Suwon, Korea *School of Electrical Engineering and INMC, Seoul National University, Seoul, Korea Abstract — In this paper, we present a novel wide-band envelope detector comprising a fully-differential operational transconductance amplifier (OTA), a full-wave rectifier and a peak detector. To enhance the frequency performance of the envelop detector, we utilize a gyrator-C active inductor load in the OTA for wider bandwidth. Additionally, it is Fig. 1. Envelope detector with OTA-rectifier-peak-detector shown that the high-speed rectifier of the envelope detector requires high bias current instead of the sub-threshold bias open loop. condition. The experimental results show that the proposed envelope detector can work from 100-Hz to 1.6-GHz with an input dynamic range of 50-dB at 100-Hz and 40-dB at 1.6- GHz, respectively. The envelope detector was fabricated on the TSMC 0.18-um CMOS process with an active area of 0.652 mm2. 3BIndex Terms — Envelope detector, Peak detector, OTA, Rectifier, Gyrator-C active inductor, Wide-band. I. INTRODUCTION The envelope detector is extensively applied in the control and energy estimation systems [1]-[3] to track the amplitude of input signals. Recently, many systems require envelope detectors capable of treating with high frequency input signals, such as embedded RFIC test bench [4], AM/ASK receiver and so on. For this reason, Fig. 2. Schematic diagram of the cascode OTA circuit. this work is dedicated to realize a high-frequency and wide-band envelope detector. -

An FSK and OOK Compatible RF Demodulator for Wake up Receivers

J. Low Power Electron. Appl. 2015, 5, 274-290; doi:10.3390/jlpea5040274 OPEN ACCESS Journal of Low Power Electronics and Applications ISSN 2079-9268 www.mdpi.com/journal/jlpea Article An FSK and OOK Compatible RF Demodulator for Wake Up Receivers Thierry Taris 1,*, Hassène Kraimia 2, Didier Belot 3 and Yann Deval 1 1 University of Bordeaux, IMS Lab, 341 Cours de la Liberation, Talence 33405, France; E-Mail:[email protected] 2 BeSpoon, 17 rue du lac Saint André, 73372 Le Bourget du Lac, France; E-Mail: [email protected] 3 CEA Leti, 17 av des Martyrs, 38000 Grenoble, France; E-Mail: [email protected] * Author to whom correspondence should be addressed; E-Mail: [email protected]; Tel.: +33-540-002-769 (ext. 123); Fax: +33-556-371-545. Academic Editor: Domenico Zito Received: 23 April 2015 / Accepted: 4 November 2015 / Published: 30 November 2015 Abstract: This work proposes a novel demodulation circuit to address the implementation of Wake-Up Receivers (Wu-Rx) in Wireless Sensor Nodes (WSN). This RF demodulator, namely Modulated Oscillator for envelOpe Detection (MOOD), is compatible with both FSK and OOK/ASK modulation schemes. The system embeds an LC oscillator, an envelope detector and a base-band amplifier. To optimize the trade-off between RF performances and power consumption, the cross-coupled based oscillator is biased in moderate inversion region. The proof of concept is implemented in a 65 nm CMOS technology and is intended for the 2.4 GHz ISM band. With a supply voltage of 0.5 V, the demodulator consumes 120 μW and demonstrates the demodulation of OOK and FSK at a data rate of 500 kbps. -

Pulsed Class-G RF Amplifier System

Pulsed Class-G RF Amplifier System By Kevin Maulhardt Kevin Haskett Senior Project ELECTRICAL ENGINEERING DEPARTMENT California Polytechnic State University San Luis Obispo 2012 TABLE OF CONTENTS Section Page I. Table of Contents ……………………………….............................................................i II. List of Figures ………….…………………………......................................................ii III. List of Tables ………….………………………….....................................................iii IV. Acknowledgments……………….…………………………………………………………………….…iv V. Abstract ……………………………………………………………………………………………………v VI. Introduction ………………………………………………………………………………………..1 A. Establishing the Problem: High PAR Signal Analysis …….………………………..2 VII. Requirements and Specifications ……………………………………………………..4 A. Functional Decomposition ……………………….………………………………………..6 VIII. Design ……………………………………………………………………………………………………8 A. Envelope Detection …………………………….………………………………………………8 B. Hysteretic Comparator ……………………………………………………………….10 C. Voltage Doubler …………………………………………………………………………..13 D. Complete Design …………………………………………………………………………..16 IX. Test Plans ………………………………………………………………………………………………….18 X. Integration and Test Results …..…………………………………………………………..21 XI. Conclusion ………………………………………………………………………………………………….29 XII. Bibliography ………………………………………………………………………………………30 XIII. Appendices ………………………………………………………………………………………33 A. Appendix A: Senior Project Analysis ……………………………………………………33 B. Appendix B: Schedule …………………………………………………………………………..35 C. Appendix C: Cost and Production Analysis ………………………………………..37 -

Peak Detector And/Or Envelope Detector — a Detailed Analysis —

Peak Detector and/or Envelope Detector — A Detailed Analysis — Predrag Pejović April 7, 2018 Abstract In this document, a simple circuit constructed using a diode, a resistor, and a capacitor, utilized as a peak detector and/or as an envelope detector is analyzed. The analysis is approached by applying approximate methods and by a mix of exact and numerical methods, aiming design guidelines and understanding of the circuit operation. Approximate and exact approaches are compared, and a region where the approximate analysis provides adequate answers is identified. Ability of the circuit to track the envelope variations is analyzed, and it is shown to depend both on the circuit time constant and the output voltage value, i.e. the modulation signal frequency and the modulation index. Relevant relations are derived and presented. Finally, distortion of the output voltage caused by the output voltage ripple is addressed, and averaged model of the circuit is derived. It is shown that average of the output voltage over the carrier period is increased about three times when filtering of the output voltage is applied. Transfer function for averaged waveforms of the envelope detector is derived, containing slight attenuation and a real pole at the double of the carrier frequency. c 2018 Predrag Pejović, This work is licensed under a Creative Commons Attribution-ShareAlike 4.0 International License. 1 Introduction Peak detector and/or envelope detector, built as a circuit of Fig. 1 is frequent in electrical engineering curricula and usually the first circuit built by enthusiasts in amateur radio clubs. The author of this document is no exception: still remembers his joy after this simple circuit demonstrated its operation. -

A Fast Envelope Detector

, ,- Accelerator Division e Alternating Gradient Synchrotron Department BROOKHAVEN NATIONAL LABORATORY Upton, New York 11973 Accelerator Division Technical Note AGS7&D/Tech. Note No. 3%- \ ,-- A FAST ENVELOPE DETECTOR by D. Ciardullo December 29, 1993 a A FAST ENVELOPE DETECTOR INTRODUCTION Traditional AM demodulating methods include both synchronous (product detector) and non-synchronous (rectification) techniques. While each has its merits, both methods require some amount of filtering to accomplish their goal of envelope detection. In certain applications (for example, when the detection scheme is utilized within a feedback loop), the resulting circuit delays present severe limitations to the system's response time. This paper describes a wideband, active envelope detector with a response time on the order of lpsec. The circuit described has a demodulation bandwidth of DC=350kHz, and provides a high degree of linearity over a dynamic range in excess of 40dB. The device is designed for broadband carrier operation (1MHz to 5MHz), but can easily be adapted to demodulate carriers in other ranges (up to VHF) . The circuit described was developed to provide a real-time monitor for an amplitude modulated rf signal swept in frequency from 1MHz to 5MHz. Although the specific accuracy, linearity and dynamic range requirements could have been satisfied using more conventional detector techniques, its inclusion as part of a feedback loop within a larger system was the ultimate motivation for developing this circuit. Standard average envelope detectors generally utilize a signal rectification/ filtering combination which requires a time constant much greater than one rf period (at the lowest carrier frequency) to maintain reasonable amplitude accuracy. -

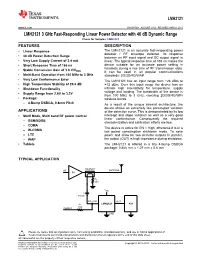

LMH2121 3 Ghz Fast-Responding Linear Power Detector with 40 Db Dynamic Range Check for Samples: LMH2121

LMH2121 www.ti.com SNVS876A –AUGUST 2012–REVISED MARCH 2013 LMH2121 3 GHz Fast-Responding Linear Power Detector with 40 dB Dynamic Range Check for Samples: LMH2121 1FEATURES DESCRIPTION The LMH2121 is an accurate fast-responding power 2• Linear Response detector / RF envelope detector. Its response • 40 dB Power Detection Range between an RF input signal and DC output signal is • Very Low Supply Current of 3.4 mA linear. The typical response time of 165 ns makes the • Short Response Time of 165 ns device suitable for an accurate power setting in handsets during a rise time of RF transmission slots. • Stable Conversion Gain of 3.6 V/V RMS It can be used in all popular communications • Multi-Band Operation from 100 MHz to 3 GHz standards: 2G/3G/4G/WAP. • Very Low Conformance Error The LMH2121 has an input range from −28 dBm to • High Temperature Stability of ±0.5 dB +12 dBm. Over this input range the device has an • Shutdown Functionality intrinsic high insensitivity for temperature, supply voltage and loading. The bandwidth of the device is • Supply Range from 2.6V to 3.3V from 100 MHz to 3 GHz, covering 2G/3G/4G/WiFi • Package: wireless bands. – 4-Bump DSBGA, 0.4mm Pitch As a result of the unique internal architecture, the device shows an extremely low part-to-part variation APPLICATIONS of the detection curve. This is demonstrated by its low • Multi Mode, Multi band RF power control intercept and slope variation as well as a very good linear conformance. Consequently the required – GSM/EDGE characterization and calibration efforts are low.