R8C/2G Group Hardware Manual RENESAS MCU R8C FAMILY / R8C/2X SERIES

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Familias De Microcontroladores

INTRODUCCION Un microcontrolador es un circuito integrado tiene en su interior todas las características de un computador, es decir, programa y circuitos periféricos para CPU, RAM, una memoria de entrada y salida. Muy regularmente los microcontroladores poseen además convertidores análogo - digital, temporizadores, contadores y un sistema para permitir la comunicación en serie y en paralelo. Se pueden crear muchas aplicaciones con los microcontroladores. Estas aplicaciones de los microcontroladores son ilimitadas, entre ellas podemos mencionar: sistemas de alarmas, iluminación, paneles publicitarios, etc. Controles automáticos para la Industria en general. Entre ellos control de motores DC/AC y motores de paso a paso, control de máquinas, control de temperatura, tiempo; adquisición de datos mediante sensores, etc. HISTORIA El primer microprocesador fue el Intel 4004 de 4 bits, lanzado en 1971, seguido por el Intel 8008 y otros más capaces. Sin embargo, ambos procesadores requieren circuitos adicionales para implementar un sistema de trabajo, elevando el costo del sistema total. Los ingenieros de Texas Instruments Gary Boone y Michael Cochran lograron crear el primer microcontrolador, TMS 1000, en 1971; fue comercializado en 1974. Combina memoria ROM, memoria RAM, microprocesador y reloj en un chip y estaba destinada a los sistemas embebidos.2 Debido en parte a la existencia del TMS 1000,3 Intel desarrolló un sistema de ordenador en un chip optimizado para aplicaciones de control, el Intel 8048, que comenzó a comercializarse en 1977.3 Combina memoria RAM y ROM en el mismo chip y puede encontrarse en más de mil millones de teclados de compatible IBM PC, y otras numerosas aplicaciones. El en ese momento presidente de Intel, Luke J. -

Renesas MCU M16C Family (R32C/M32C/M16C/R8C)

2008.01 Renesas MCU M16C Family (R32C/M32C/M16C/R8C) www.renesas.com World’s No. 1* Flash MCUs !! index Roadmap Total shipments of Rewriting possible during operation, and CPU Architecture World’s No. 1 1,000,000,000 units!! World’s No. 1 program/erase cycles increased to 100,000! E2dataFlash substantially improves the functionality and performance of data Flash MCUs Thanks to strong demand, total flash MCU Flash MCUs flash, allowing data to be rewritten independently while the MCU is operating. Concepts Proof No. 1 shipments reached the 1 billion mark in March 2007. Proof No. 4 Guaranteed program/erase cycles have been increased to 100,000, and data Renesas flash MCUs are used in a wide range of save times are two orders of magnitude faster than external E2PROM. consumer, industrial and automotive applications. (E2dataFlash: E2PROM emulation data flash memory) Product Lineup Development Tools No. 1 lineup of flash MCUs with 40µsec./byte high-speed flash World’s No. 1 over 300 products in 30 series!! World’s No. 1 programming!! Development Flash MCUs Flash MCUs Tools from Divided into high-end, middle, and low-end classes, Flash MCU technology supports high-speed Renesas Partners Proof No. 2 the flash MCU lineup is built on the most advanced Proof No. 5 programming at a rate of 512KB every 20 seconds technology. Flexible support is provided for (total time required for reprogramming, including Middleware/ increasingly large and complex software. erasing and programming). Demo Sets Functions/ Application Fields Memory Capacity High-speed flash memory supporting Comprehensive support and World’s No. -

Embedded Operating Systems

7 Embedded Operating Systems Claudio Scordino1, Errico Guidieri1, Bruno Morelli1, Andrea Marongiu2,3, Giuseppe Tagliavini3 and Paolo Gai1 1Evidence SRL, Italy 2Swiss Federal Institute of Technology in Zurich (ETHZ), Switzerland 3University of Bologna, Italy In this chapter, we will provide a description of existing open-source operating systems (OSs) which have been analyzed with the objective of providing a porting for the reference architecture described in Chapter 2. Among the various possibilities, the ERIKA Enterprise RTOS (Real-Time Operating System) and Linux with preemption patches have been selected. A description of the porting effort on the reference architecture has also been provided. 7.1 Introduction In the past, OSs for high-performance computing (HPC) were based on custom-tailored solutions to fully exploit all performance opportunities of supercomputers. Nowadays, instead, HPC systems are being moved away from in-house OSs to more generic OS solutions like Linux. Such a trend can be observed in the TOP500 list [1] that includes the 500 most powerful supercomputers in the world, in which Linux dominates the competition. In fact, in around 20 years, Linux has been capable of conquering all the TOP500 list from scratch (for the first time in November 2017). Each manufacturer, however, still implements specific changes to the Linux OS to better exploit specific computer hardware features. This is especially true in the case of computing nodes in which lightweight kernels are used to speed up the computation. 173 174 Embedded Operating Systems Figure 7.1 Number of Linux-based supercomputers in the TOP500 list. Linux is a full-featured OS, originally designed to be used in server or desktop environments. -

Parameter Files for Flash Memory Programmer PG-FP5 Released

Tool News RENESAS TOOL NEWS on March 29, 2012: 120329/tn7 Parameter Files for Flash Memory Programmer PG-FP5 Released We have revised and newly published parameter files for the flash memory programmer PG- FP5. These files save information about the MCUs they support in the text format, and the PG-FP5 uses this information to program the flash memories of those MCUs. For an overview of the PG-FP5, go to: https://www.renesas.com/pg_fp5 The above URL is one of our global sites. 1. Released Parameter Files and Their Versions 1.1 Newly Published Parameter Files (1) For RL78 family - PR5-R5F10R V1.00 (for RL78/L12 group) (2) For R8C family - PR5-R8C5X V1.00 (for R8C/5x series) 1.2 Revised Parameter Files (1) For RL78 family - PR5-R5F104 V1.03 (for RL78/G14 group) (2) For 78K family - PR5-78F1845 V1.02 (for 78K0R/Fx3) NOTE: Only the release note included in PR5-78F1845 has been updated. The parameter file itself is same as one in V1.01. - PR5-78F8058 V1.02 (for UPD78F8058) (3) For R8C family - PR5-R8C3X V1.01 (for R8C/3x series) - PR5-R8CLX V1.01 (for R8C/Lx series) (4) For V850 family - PR5-70F3786 V1.01 (for V850ES/Jx3-E) - PR5-70F3738 V1.03 (for V850ES/Jx3-L) - PR5-70F4012 V1.03 (for V850E2/Fx4) 2. Device Support Updated In the UPD70F3735, UPD70F3736, UPD70F3737, and UPD70F3738 MCUs, which belong to the V850ES/Jx3-L, an improvement has already been made so that their flash memories can be programmed when used in a main-clock frequency range (an fx range) of 5 to 10 MHz. -

Formal Fault Injection Vulnerability Detection in Binaries: a Software

Formal fault injection vulnerability detection in binaries : a software process and hardware validation Nisrine Jafri To cite this version: Nisrine Jafri. Formal fault injection vulnerability detection in binaries : a software process and hard- ware validation. Cryptography and Security [cs.CR]. Université Rennes 1, 2019. English. NNT : 2019REN1S014. tel-02385208 HAL Id: tel-02385208 https://tel.archives-ouvertes.fr/tel-02385208 Submitted on 28 Nov 2019 HAL is a multi-disciplinary open access L’archive ouverte pluridisciplinaire HAL, est archive for the deposit and dissemination of sci- destinée au dépôt et à la diffusion de documents entific research documents, whether they are pub- scientifiques de niveau recherche, publiés ou non, lished or not. The documents may come from émanant des établissements d’enseignement et de teaching and research institutions in France or recherche français ou étrangers, des laboratoires abroad, or from public or private research centers. publics ou privés. T HÈSE DE DOCTORAT DE L’UNIVERSITE DE RENNES 1 COMUE UNIVERSITE BRETAGNE LOIRE Ecole Doctorale N°601 Mathèmatique et Sciences et Technologies de l’Information et de la Communication Spécialité : Informatique Par « Nisrine JAFRI » « Formal Fault Injection Vulnerability Detection in Binaries » «A Software Process and Hardware Validation» Thèse présentée et soutenue à RENNES , le 25 mars 2019 Unité de recherche : Inria, TAMIS team Thèse N°: Rapporteurs avant soutenance : Marie-Laure POTET, Professeur des Universités, ENSIMAG Jean-Yves MARION, Professeur des Universités, Université de Lorraine Composition du jury : Président : Pierre-Alain FOUQUE, Professeur des Universités, Université Rennes 1 Examinateurs : Leijla BATINA, Professeur des Université s, Université Radboud de Nimegue Shivam BHASIN, Chercheur, Université technologique de Singapour Sylvain GUILLEY, Professeur des Universités, Télécom ParisTech Annelie HEUSER, Chercheur, CNRS Dir. -

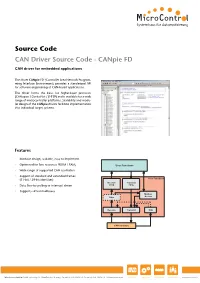

Datasheet CAN Driver Source Code

Source Code CAN Driver Source Code - CANpie FD CAN driver for embedded applications The driver CANpie FD (Controller Area Network Program- ming Interface Environment) provides a standarized API for software engineering of CAN-based applications. The driver forms the basis for higher-layer protocols (CANopen / DeviceNet / J1939) and is available for a wide range of microcontroller platforms. Scalability and modu- lar design of the CANpie drivers facilitate implementation into individual target systems. Features • Modular design, scalable, easy to implement • Optimized for low resources (ROM / RAM) User Functions • Wide range of supported CAN controllers • Support of standard and extended frames (11-bit / 29-bit identifier) Core Functions Receive Transmit • Data flow by polling or interrupt driven FIFO FIFO • Supports virtual mailboxes Mailbox Access Filter Receive Transmit IRQ CAN hardware MicroControl GmbH & Co. KG · Junkersring 23 · 53844 Troisdorf · Germany · Fon +49 (0) 2241 256 59 - 0 · Fax +49 (0) 2241 256 59 - 11 · [email protected] I/O Module Steuerungen Protokollstacks Dienstleistungen www.microcontrol.net Technical Data CAN driver source code - CANpie FD Identifier • Standard Frame (11-bit) • Extended Frame (29-bit) Formats • Data Frame • Remote Frame • Error Frame (Receive) Monitoring of fault conditions • ACK (depending on controller) • Bit Error • Format Error • CRC Error • Stuff Error Dataflow • Interrupt • Polling Special Features • Mailbox access • Software Filter Order Number Description / CAN Controller 50.10.079 -

User Manual for Emload , Version 3.14

emLoad Software Version 3.14p Manual revision 0 A product of SEGGER Microcontroller GmbH 2/128 User manual for emLoad , version 3.14 Disclaimer Specifications written in this manual are believed to be accurate, but are not guaranteed to be entirely free of error. Specifications in this manual may be changed for functional or performance improvements without notice. Please make sure your manual is the latest edition. While the information herein is as- sumed to be accurate, SEGGER Microcontroller GmbH (the manufacturer) as- sumes no responsibility for any errors or omissions and makes and you receive no warranties. The manufacturer specifically disclaims any implied warranty of fitness for a particular purpose. Copyright notice The latest version of this manual is available as PDF file in the download area of our website at www.segger.com. You are welcome to copy and distribute the file as well as the printed version. You may not extract portions of this manual or modify the PDF file in any way without the prior written permission of the manufacturer. The software described in this document is furnished under a li- cense and may only be used or copied in accordance with the terms of such a license. 2020 SEGGER Microcontroller GmbH, Monheim am Rhein / Germany Trademarks Names mentioned in this manual may be trademarks of their respective com- panies. Brand and product names are trademarks or registered trademarks of their re- spective holders. 2020 SEGGER Microcontroller GmbH User manual for emLoad , version 3.14 3/128 Contact / registration Please register the software via email. This way we can make sure you will re- ceive updates or notifications of updates as soon as they become available. -

Renesas General-Purpose Microcontrollers/Microprocessors Lineup Catalog

Renesas General-Purpose Microcontrollers/Microprocessors Lineup Catalog Notes: Renesas General-Purpose Microcontrollers/Microprocessors 1. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information. 2. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein. 3. Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or Lineup Catalog others. 4. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from such alteration, modification, copy or otherwise misappropriation of Renesas Electronics product. 5. Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. -

RL78/G14 RESH-OS-MC-20001 Rev.1.00 Power Tool 120 Deg

APPLICATION NOTE RL78/G14 RESH-OS-MC-20001 Rev.1.00 Power Tool 120 deg. Reference Development Nov 03, 2011 Introduction This document will provide an overview of power tool 120 degree reference development. This solution is based on Renesas Electronics' next-generation MCU (RL78 family), which combines advanced features from both the 78K and R8C families. Same as mainstream power tool products in market, BLDC control is used in this solution. Target Device RL78/G14 Group Contents 1. Overview ........................................................................................................................................... 2 2. System Diagram................................................................................................................................ 3 3. Configuration of R5F104BE .............................................................................................................. 4 4. Control theory.................................................................................................................................... 9 5. Hardware structure.......................................................................................................................... 13 6. Hardware and test data................................................................................................................... 19 7. Software flowchart........................................................................................................................... 22 APPENDIX ............................................................................................................................................. -

2019 Embedded Markets Study Integrating Iot and Advanced Technology Designs, Application Development & Processing Environments March 2019

2019 Embedded Markets Study Integrating IoT and Advanced Technology Designs, Application Development & Processing Environments March 2019 Presented By: © 2019 AspenCore All Rights Reserved 2 Preliminary Comments • Results: Data from this study is highly projectable at 95% confidence with +/-3.15% confidence interval. Other consistencies with data from previous versions of this study also support a high level of confidence that the data reflects accurately the EETimes and Embedded.com audience’s usage of advance technologies, software and hardware development tools, chips, operating systems, FPGA vendors, and the entire ecosystem of their embedded development work environment and projects with which they are engaged. • Historical: The EETimes/Embedded.com Embedded Markets Study was last conducted in 2017. This report often compares results for 2019 to 2017 and in some cases to 2015 and earlier. This study was first fielded over 20 years ago and has seen vast changes in technology evolution over that period of time. • Consistently High Confidence: Remarkable consistency over the years has monitored both fast and slow moving market changes. A few surprises are shown this year as well, but overall trends are largely confirmed. • New Technologies and IoT: Emerging markets and technologies are also tracked in this study. New data regarding IoT and advanced technologies (IIoT, embedded vision, embedded speech, VR, AR, machine learning, AI and other cognitive capabilities) are all included. 3 Purpose and Methodology • Purpose: To profile the findings of the 2019 Embedded Markets Study comprehensive survey of the embedded systems markets worldwide. Findings include technology used, all aspects of the embedded development process, IoT, emerging technologies, tools used, work environment, applications developed for, methods/ processes, operating systems used, reasons for using chips and technology, and brands and specific chips being considered by embedded developers. -

RX Family Brochure

RX FAMILY Renesas 32-Bit Microcontrollers 2020.04 Mid-range 32-bit microcontrollers built around an exclusive CPU core developed by Renesas Maintaining and Advancing the Renesas Tradition FACTORY OFFICE HOME CONTENT Positioning of the RX Family ........................................................................04 RX Family Solutions .....................................................................................08 RX Core Features ..........................................................................................16 RXv2 Core Features ......................................................................................18 RXv3 Core Features ......................................................................................19 • The following new products have been added: RX700/RX600 Series ....................................................................................20 RX700 Series: RX72M, RX72N, RX72T RX200 Series ................................................................................................22 RX600 Series: RX66N, RX66T RX100 Series ................................................................................................24 RX200 Series: RX23W, RX23E-A RX for Motor Control (RX-T) .........................................................................26 RX100 Series: RX13T RX Family Motor Control ..............................................................................28 • Information on the following solutions has been added: RX Family Development Tools ......................................................................30 -

The Embedded Experts

The Embedded Experts Debug Probes Software Tools RTOS File System Compression Connectivity Security & IoT User Interface Production Debug Probes J-Link SEGGER Embedded Studio n Features n J-Link Debug Probes n Supports Arm® Cortex®-M / R / A cores, including the 64-bit cores (ARMv8-A) and Arm® 7 / 9 / 11, Microchip PIC32, Renesas RX, RISC-V and Silicon Labs 8051 SEGGER J-Links are the most widely used line of also adds support for corner cases that cannot be debug probes available today. They have proven their supported without such intelligence. n Maximum JTAG speed 15 MHz, J-Link ULTRA+ / PRO: 50 MHz worth for more than 15 years with over 1 Mio units in A sample for such a scenario is: Accessing a slowly n Download speed up to 1.5 MB/s (J-Link® / J-Link® PLUS), 3 MB/s (J-Link® ULTRA+ / PRO) the field. This popularity stems from the unparalleled running CPU at high target interface speeds. J-Links n Power profiling (J-Link® ULTRA+ / PRO) performance, extensive feature set, large number of are the most robust probe in these situations. n Very fast flash loader supported CPUs and compatibility with all popular n Supported by all popular debuggers development environments. n Software Development Kit (SDK) n Support for different debug interfaces: JTAG / SWD / FINE / SPD / ICSP For customers who want to build their n Debug smarter and faster with J-Link! own applications using J-Link, and for n Serial Wire Viewer (SWV) with up to 7.5 / 25 MHz supported With up to 3 MByte per second download speed IDE vendors who implement J-Link n Host interface: USB, Ethernet to RAM and record-breaking flashloaders, and with support for their IDE, SEGGER n Power over USB the ability to set an unlimited number of breakpoints offers a J-Link SDK which n Support for adaptive clocking in flash memory of MCUs, J-Link debug probes comes with the J-Link DLL, n Multi-core debugging supported are undoubtedly the best choice to optimize your the API documentation and debugging and flash programming experience.