VME Bus Tutorial

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

University of California at Berkeley College of Engineering Department of Electrical Engineering and Computer Science

University of California at Berkeley College of Engineering Department of Electrical Engineering and Computer Science EECS 61C, Fall 2003 Lab 2: Strings and pointers; the GDB debugger PRELIMINARY VERSION Goals To learn to use the gdb debugger to debug string and pointer programs in C. Reading Sections 5.1-5.5, in K&R GDB Reference Card (linked to class page under “resources.”) Optional: Complete GDB documentation (http://www.gnu.org/manual/gdb-5.1.1/gdb.html) Note: GDB currently only works on the following machines: • torus.cs.berkeley.edu • rhombus.cs.berkeley.edu • pentagon.cs.berkeley.edu Please ssh into one of these machines before starting the lab. Basic tasks in GDB There are two ways to start the debugger: 1. In EMACS, type M-x gdb, then type gdb <filename> 2. Run gdb <filename> from the command line The following are fundamental operations in gdb. Please make sure you know the gdb commands for the following operations before you proceed. 1. How do you run a program in gdb? 2. How do you pass arguments to a program when using gdb? 3. How do you set a breakpoint in a program? 4. How do you set a breakpoint which which only occurs when a set of conditions is true (eg when certain variables are a certain value)? 5. How do you execute the next line of C code in the program after a break? 1 6. If the next line is a function call, you'll execute the call in one step. How do you execute the C code, line by line, inside the function call? 7. -

Getting Started with Your VXI-1394 Interface for Windows NT/98 And

VXI Getting Started with Your VXI-1394 Interface for Windows NT/98 VXI-1394 Interface for Windows NT/98 November 1999 Edition Part Number 322109D-01 Worldwide Technical Support and Product Information www.ni.com National Instruments Corporate Headquarters 11500 North Mopac Expressway Austin, Texas 78759-3504 USA Tel: 512 794 0100 Worldwide Offices Australia 03 9879 5166, Austria 0662 45 79 90 0, Belgium 02 757 00 20, Brazil 011 284 5011, Canada (Calgary) 403 274 9391, Canada (Ontario) 905 785 0085, Canada (Québec) 514 694 8521, China 0755 3904939, Denmark 45 76 26 00, Finland 09 725 725 11, France 01 48 14 24 24, Germany 089 741 31 30, Greece 30 1 42 96 427, Hong Kong 2645 3186, India 91805275406, Israel 03 6120092, Italy 02 413091, Japan 03 5472 2970, Korea 02 596 7456, Mexico (D.F.) 5 280 7625, Mexico (Monterrey) 8 357 7695, Netherlands 0348 433466, Norway 32 27 73 00, Poland 48 22 528 94 06, Portugal 351 1 726 9011, Singapore 2265886, Spain 91 640 0085, Sweden 08 587 895 00, Switzerland 056 200 51 51, Taiwan 02 2377 1200, United Kingdom 01635 523545 For further support information, see the Technical Support Resources appendix. To comment on the documentation, send e-mail to [email protected] © Copyright 1998, 1999 National Instruments Corporation. All rights reserved. Important Information Warranty The National Instruments VXI-1394 board is warranted against defects in materials and workmanship for a period of one year from the date of shipment, as evidenced by receipts or other documentation. National Instruments will, at its option, repair or replace equipment that proves to be defective during the warranty period. -

Allgemeines Abkürzungsverzeichnis

Allgemeines Abkürzungsverzeichnis L. -

M32R Debugger and Trace

M32R Debugger and Trace TRACE32 Online Help TRACE32 Directory TRACE32 Index TRACE32 Documents ...................................................................................................................... ICD In-Circuit Debugger ................................................................................................................ Processor Architecture Manuals .............................................................................................. M32R ......................................................................................................................................... M32R Debugger and Trace .................................................................................................. 1 Introduction ....................................................................................................................... 4 Brief Overview of Documents for New Users 4 Warning .............................................................................................................................. 5 Quick Start ......................................................................................................................... 6 Troubleshooting ................................................................................................................ 9 SYStem.Up Errors 9 Memory Access Errors 9 FAQ ..................................................................................................................................... 9 CPU specific SYStem Settings and Restrictions .......................................................... -

Mac OS 8 Update

K Service Source Mac OS 8 Update Known problems, Internet Access, and Installation Mac OS 8 Update Document Contents - 1 Document Contents • Introduction • About Mac OS 8 • About Internet Access What To Do First Additional Software Auto-Dial and Auto-Disconnect Settings TCP/IP Connection Options and Internet Access Length of Configuration Names Modem Scripts & Password Length Proxies and Other Internet Config Settings Web Browser Issues Troubleshooting • About Mac OS Runtime for Java Version 1.0.2 • About Mac OS Personal Web Sharing • Installing Mac OS 8 • Upgrading Workgroup Server 9650 & 7350 Software Mac OS 8 Update Introduction - 2 Introduction Mac OS 8 is the most significant update to the Macintosh operating system since 1984. The updated system gives users PowerPC-native multitasking, an efficient desktop with new pop-up windows and spring-loaded folders, and a fully integrated suite of Internet services. This document provides information about Mac OS 8 that supplements the information in the Mac OS installation manual. For a detailed description of Mac OS 8, useful tips for using the system, troubleshooting, late-breaking news, and links for online technical support, visit the Mac OS Info Center at http://ip.apple.com/infocenter. Or browse the Mac OS 8 topic in the Apple Technical Library at http:// tilsp1.info.apple.com. Mac OS 8 Update About Mac OS 8 - 3 About Mac OS 8 Read this section for information about known problems with the Mac OS 8 update and possible solutions. Known Problems and Compatibility Issues Apple Language Kits and Mac OS 8 Apple's Language Kits require an updater for full functionality with this version of the Mac OS. -

PRE LIM INARY KDII-D Processor Manual (PDP-Ll/04)

PRE LIM I N A R Y KDII-D Processor Manual (PDP-ll/04) The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation. Digital Equipment Corporation assumes no responsibility for any errors that may appear in this manual. Copyright C 1975 by Digital Equipment Corporation Written by PDP-II Engineering PREFACE OVE~ALt DESCRIPTION 3 8 0 INsT~UCTION SET 3~1 Introduction 1~2 Addressing ModIs 3.3 Instruction Timing l@4 In~truet1on Dtlcriptlonl le!5 Dlffer~ncei a,tween KOlle and KOllS ]0 6 Programming Diftereneel B~twlen pepita ).7 SUI L~tency Tim@1 CPu OPERlTING 5PECIFICATID~S 5 e 0 DETAILED HARDWARE DESC~ltTION 5.1 IntrOduction 5 m2 Data path Circuitry 5.2g1 General D~serlpt1on 5.2,,2 ALU 5,2 .. 3 Scratch Pad Mtmory 5.2,.3.1 Scratch P~d Circuitry 5.2.3.2 SCrateh P~d Addr~11 MUltlplex.r 5.2.3.3 SCrateh Pad Regilter 5 0 2 .. 4 B J:H'!qilil ter 5.2 .. 4.1 B ReQister CircuItry 5.2 .. 4.2 8 L~G MUltl~lex@r 5,2.5 AMUX 5.2.6 Pfoeellof statuI Word (PSW) 5.3 Con<Htion COd@i 5.3.1 G~neral De~erl~tlon 5.3.2 Carry and overflow Decode 5.3.3 Ayte Multiplexing 5.4 UNIBUS Addf@$5 and Data Interfaces S.4 g 1 U~IBUS Dr1v~rl and ~lee1Vtrl 5.4@2 Bus Addr~s~ Generation 5 8 4111 Internal Addrf$$ D@coder 5 0 4,.4 Bus Data Line Interface S.5 Instruet10n DeCoding 5.5,,1 General De~er1pt1nn 5;5.2 Instruction Re91lt~r 5.5,,3 Instruetlon Decoder 5.5.3 0 1 Doubl~ O~erand InltrYetions 5.5.3.2 Single Operand Inltruetlons 5,5.3.3 Branch In$truetionl 5 8 5.3 6 4 Op~rate rn~truet1ons 5.6 Auil11ary ALU Control 5.6.1 G~ntral Delcrlptlon 5.6.2 COntrol Circuitry 5.6.2.1 Double Op@rand Instructions 5.6.2.2 Singl@ nDef~nd Instruet10ns PaQe 3 5.7 Data Transfer Control 5,7,1 General Descr1ption 5,7,2 Control CIrcuItry 5,7,2,1 Procelsor Cloek Inhibit 5,7,2.2 UNIBUS Synchronization 5,7.2,3 BUs Control 5.7,2.4 MSyN/SSYN Timeout 5,7.2.5 Bus Error. -

Publication Title 1-1962

publication_title print_identifier online_identifier publisher_name date_monograph_published_print 1-1962 - AIEE General Principles Upon Which Temperature 978-1-5044-0149-4 IEEE 1962 Limits Are Based in the rating of Electric Equipment 1-1969 - IEEE General Priniciples for Temperature Limits in the 978-1-5044-0150-0 IEEE 1968 Rating of Electric Equipment 1-1986 - IEEE Standard General Principles for Temperature Limits in the Rating of Electric Equipment and for the 978-0-7381-2985-3 IEEE 1986 Evaluation of Electrical Insulation 1-2000 - IEEE Recommended Practice - General Principles for Temperature Limits in the Rating of Electrical Equipment and 978-0-7381-2717-0 IEEE 2001 for the Evaluation of Electrical Insulation 100-2000 - The Authoritative Dictionary of IEEE Standards 978-0-7381-2601-2 IEEE 2000 Terms, Seventh Edition 1000-1987 - An American National Standard IEEE Standard for 0-7381-4593-9 IEEE 1988 Mechanical Core Specifications for Microcomputers 1000-1987 - IEEE Standard for an 8-Bit Backplane Interface: 978-0-7381-2756-9 IEEE 1988 STEbus 1001-1988 - IEEE Guide for Interfacing Dispersed Storage and 0-7381-4134-8 IEEE 1989 Generation Facilities With Electric Utility Systems 1002-1987 - IEEE Standard Taxonomy for Software Engineering 0-7381-0399-3 IEEE 1987 Standards 1003.0-1995 - Guide to the POSIX(R) Open System 978-0-7381-3138-2 IEEE 1994 Environment (OSE) 1003.1, 2004 Edition - IEEE Standard for Information Technology - Portable Operating System Interface (POSIX(R)) - 978-0-7381-4040-7 IEEE 2004 Base Definitions 1003.1, 2013 -

PPC7A10 at Our Website: Click HERE Powerx Product Manual PPC7A

Full-service, independent repair center -~ ARTISAN® with experienced engineers and technicians on staff. TECHNOLOGY GROUP ~I We buy your excess, underutilized, and idle equipment along with credit for buybacks and trade-ins. Custom engineering Your definitive source so your equipment works exactly as you specify. for quality pre-owned • Critical and expedited services • Leasing / Rentals/ Demos equipment. • In stock/ Ready-to-ship • !TAR-certified secure asset solutions Expert team I Trust guarantee I 100% satisfaction Artisan Technology Group (217) 352-9330 | [email protected] | artisantg.com All trademarks, brand names, and brands appearing herein are the property o f their respective owners. Find the Abaco Systems / Radstone PPC7A10 at our website: Click HERE PowerX Product Manual PPC7A Appendix C - PPC7A This appendix contains hardware information for PPC7A boards. The information contained in this document must be used in conjunction with PowerX Quick Start, PowerX User Guides and/or the PowerX product Manual. Link Settings...................................................................................................................................... C-3 Default Link Settings............................................................................................................................... C-3 RTC Standby Supply Voltage Link (E1)................................................................................................. C-4 FLASH Write Enable Links (E3 and E9)............................................................................................... -

VM E Bus S Ingle -B Oard C Om Puter

DATASHEET KEY FEATURES 2eSST VMEbus protocol with The Motorola MVME6100 The promise of the VME 320MB/s transfer rate across series provides more than just Renaissance is innovation, the VMEbus faster VMEbus transfer rates; it performance and investment provides balanced performance protection. The MVME6100 MPC7457 PowerPC® processor from the processor, memory series from Motorola delivers running at up to 1.267 GHz subsystem, local buses and I/O on this promise. The innovative 128-bit AltiVec coprocessor for subsystems. Customers looking design of the MVME6100 parallel processing, ideal for for a technology refresh for their provides a high performance data-intensive applications application, while maintaining platform that allows customers backwards compatibility with to leverage their investment in Up to 2GB of on-board DDR their existing VMEbus infra- their VME infrastructure. ECC memory and 128MB of structure, can upgrade to the fl ash memory for demanding The MVME6100 series supports MVME6100 series and applications booting a variety of operating take advantage of its enhanced systems including a complete Two 33/66/100 MHz PMC-X performance features. range of real-time operating sites allow the addition of systems and kernels. A VxWorks industry-standard, application- board support package and specifi c modules Linux support are available for Dual Gigabit Ethernet interfaces the MVME6100 series. for high performance networking The MVME6100 series is the fi rst VMEbus single-board computer (SBC) designed with the Tundra Tsi148 VMEbus interface chip offering two edge source synchronous transfer (2eSST) VMEbus performance. The 2eSST protocol enables the VMEbus to run at a practical bandwidth of 320MB/s in most cases. -

Processes, System Calls and More

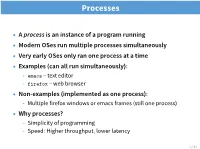

Processes • A process is an instance of a program running • Modern OSes run multiple processes simultaneously • Very early OSes only ran one process at a time • Examples (can all run simultaneously): - emacs – text editor - firefox – web browser • Non-examples (implemented as one process): - Multiple firefox windows or emacs frames (still one process) • Why processes? - Simplicity of programming - Speed: Higher throughput, lower latency 1 / 43 A process’s view of the world • Each process has own view of machine - Its own address space - Its own open files - Its own virtual CPU (through preemptive multitasking) • *(char *)0xc000 dierent in P1 & P2 • Simplifies programming model - gcc does not care that firefox is running • Sometimes want interaction between processes - Simplest is through files: emacs edits file, gcc compiles it - More complicated: Shell/command, Window manager/app. 2 / 43 Outline 1 Application/Kernel Interface 2 User view of processes 3 Kernel view of processes 3 / 43 System Calls • Systems calls are the interface between processes and the kernel • A process invokes a system call to request operating system services • fork(), waitpid(), open(), close() • Note: Signals are another common mechanism to allow the kernel to notify the application of an important event (e.g., Ctrl-C) - Signals are like interrupts/exceptions for application code 4 / 43 System Call Soware Stack Application 1 5 Syscall Library unprivileged code 4 2 privileged 3 code Kernel 5 / 43 Kernel Privilege • Hardware provides two or more privilege levels (or protection rings) • Kernel code runs at a higher privilege level than applications • Typically called Kernel Mode vs. User Mode • Code running in kernel mode gains access to certain CPU features - Accessing restricted features (e.g. -

A Not So Short Introduction to Pcie

Practical introduction to PCI Express with FPGAs Michal HUSEJKO, John EVANS [email protected] IT-PES-ES v 1.0 Agenda • What is PCIe ? o System Level View o PCIe data transfer protocol • PCIe system architecture • PCIe with FPGAs o Hard IP with Altera/Xilinx FPGAs o Soft IP (PLDA) o External PCIe PHY (Gennum) v 1.0 System Level View • Interconnection • Top-down tree hierarchy • PCI/PCIe configuration space • Protocol v 1.0 Interconnection • Serial interconnection • Dual uni-directional • Lane, Link, Port • Scalable o Gen1 2.5/ Gen2 5.0/ Gen3 8.0 GT/s o Number of lanes in FPGAs: x1, x2, x4, x8 • Gen1/2 8b10b • Gen3 128b/130b v 1.0 Image taken from “Introduction to PCI Express” Tree hierarchy • Top-down tree hierarchy with single host • 3 types of devices: Root Complex, Endpoint, Switch • Point-to-point connection between devices without sideband signalling • 2 types of ports: downstream/upstream • Configuration space Image taken from “Introduction to PCI Express” v 1.0 PCIe Configuration space • Similar to PCI conf space – binary compatible for first 256 bytes • Defines device(system) capabilities • Clearly identifies device in the system o Device ID o Vendor ID o Function ID o All above • and defines memory space allocated to device. v 1.0 PCIe transfer protocol • Transaction categories • Protocol • Implementation of the protocol v 1.0 Transaction categories • Configuration – move downstream • Memory – address based routing • IO – address based routing • Message – ID based routing v 1.0 Transaction Types v 1.0 Table taken from “PCI -

NI Vxipc-486 500 Series Lynxos Manual

Full-service, independent repair center -~ ARTISAN® with experienced engineers and technicians on staff. TECHNOLOGY GROUP ~I We buy your excess, underutilized, and idle equipment along with credit for buybacks and trade-ins. Custom engineering Your definitive source so your equipment works exactly as you specify. for quality pre-owned • Critical and expedited services • Leasing / Rentals/ Demos equipment. • In stock/ Ready-to-ship • !TAR-certified secure asset solutions Expert team I Trust guarantee I 100% satisfaction Artisan Technology Group (217) 352-9330 | [email protected] | artisantg.com All trademarks, brand names, and brands appearing herein are the property o f their respective owners. Find the National Instruments VXIpc-486 Model 566 at our website: Click HERE Getting Started with Your NI-VXI™ Software for the VXIpc™-486 Model 500 Series and LynxOS bus September 1995 Edition Part Number 321006A-01 © Copyright 1995 National Instruments Corporation. All Rights Reserved. National Instruments Corporate Headquarters 6504 Bridge Point Parkway Austin, TX 78730-5039 (512) 794-0100 Technical support fax: (800) 328-2203 (512) 794-5678 Branch Offices: Australia 03 9 879 9422, Austria 0662 45 79 90 0, Belgium 02 757 00 20, Canada (Ontario) 519 622 9310, Canada (Québec) 514 694 8521, Denmark 45 76 26 00, Finland 90 527 2321, France 1 48 14 24 24, Germany 089 741 31 30, Hong Kong 2645 3186, Italy 02 48301892, Japan 03 5472 2970, Korea 02 596 7456, Mexico 95 800 010 0793, Netherlands 0348 433466, Norway 32 84 84 00, Singapore 2265886, Spain 91 640 0085, Sweden 08 730 49 70, Switzerland 056 200 51 51, Taiwan 02 377 1200, U.K.