Design and Implementation of High Performance DDR3 SDRAM Controller

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

2GB DDR3 SDRAM 72Bit SO-DIMM

Apacer Memory Product Specification 2GB DDR3 SDRAM 72bit SO-DIMM Speed Max CAS Component Number of Part Number Bandwidth Density Organization Grade Frequency Latency Composition Rank 0C 78.A2GCB.AF10C 8.5GB/sec 1066Mbps 533MHz CL7 2GB 256Mx72 256Mx8 * 9 1 Specifications z Support ECC error detection and correction z On DIMM Thermal Sensor: YES z Density:2GB z Organization – 256 word x 72 bits, 1rank z Mounting 9 pieces of 2G bits DDR3 SDRAM sealed FBGA z Package: 204-pin socket type small outline dual in line memory module (SO-DIMM) --- PCB height: 30.0mm --- Lead pitch: 0.6mm (pin) --- Lead-free (RoHS compliant) z Power supply: VDD = 1.5V + 0.075V z Eight internal banks for concurrent operation ( components) z Interface: SSTL_15 z Burst lengths (BL): 8 and 4 with Burst Chop (BC) z /CAS Latency (CL): 6,7,8,9 z /CAS Write latency (CWL): 5,6,7 z Precharge: Auto precharge option for each burst access z Refresh: Auto-refresh, self-refresh z Refresh cycles --- Average refresh period 7.8㎲ at 0℃ < TC < +85℃ 3.9㎲ at +85℃ < TC < +95℃ z Operating case temperature range --- TC = 0℃ to +95℃ z Serial presence detect (SPD) z VDDSPD = 3.0V to 3.6V Apacer Memory Product Specification Features z Double-data-rate architecture; two data transfers per clock cycle. z The high-speed data transfer is realized by the 8 bits prefetch pipelined architecture. z Bi-directional differential data strobe (DQS and /DQS) is transmitted/received with data for capturing data at the receiver. z DQS is edge-aligned with data for READs; center aligned with data for WRITEs. -

Dual-DIMM DDR2 and DDR3 SDRAM Board Design Guidelines, External

5. Dual-DIMM DDR2 and DDR3 SDRAM Board Design Guidelines June 2012 EMI_DG_005-4.1 EMI_DG_005-4.1 This chapter describes guidelines for implementing dual unbuffered DIMM (UDIMM) DDR2 and DDR3 SDRAM interfaces. This chapter discusses the impact on signal integrity of the data signal with the following conditions in a dual-DIMM configuration: ■ Populating just one slot versus populating both slots ■ Populating slot 1 versus slot 2 when only one DIMM is used ■ On-die termination (ODT) setting of 75 Ω versus an ODT setting of 150 Ω f For detailed information about a single-DIMM DDR2 SDRAM interface, refer to the DDR2 and DDR3 SDRAM Board Design Guidelines chapter. DDR2 SDRAM This section describes guidelines for implementing a dual slot unbuffered DDR2 SDRAM interface, operating at up to 400-MHz and 800-Mbps data rates. Figure 5–1 shows a typical DQS, DQ, and DM signal topology for a dual-DIMM interface configuration using the ODT feature of the DDR2 SDRAM components. Figure 5–1. Dual-DIMM DDR2 SDRAM Interface Configuration (1) VTT Ω RT = 54 DDR2 SDRAM DIMMs (Receiver) Board Trace FPGA Slot 1 Slot 2 (Driver) Board Trace Board Trace Note to Figure 5–1: (1) The parallel termination resistor RT = 54 Ω to VTT at the FPGA end of the line is optional for devices that support dynamic on-chip termination (OCT). © 2012 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. -

Double-Data Rate DDR Memory Review

International Journal of Advanced Engineering and Nano Technology (IJAENT) ISSN: 2347-6389, Volume-2 Issue-2, January 2015 Double-Data Rate DDR Memory Review Ahmed Shamil Mustafa, Mohammed Jabbar Mohammed, Muthana Najim Abdulleh technique became DDR. The technology, synchronous Abstract —Computer is one most important twenty-first century dynamic random access memory (SDRAM) was discovered technology, the large volume of data and store it makes of old in the beginning 1990s to make the computer more powerful, memories are not enough. In this paper we offer a historical in that time was used Traditional DRAM an asynchronous overview of Double Data Rate (DDR) memory being play a key interface it means work independently of the processor. With role in the development of computer with also who passed him in the end of the nineties of the last century and the beginning of addition to the basics of their work and develop in the future. 2000s, specifically in 2000 became a priority for developers Index Terms —Double-Data Rate DDR, Synchronous Dynamic and manufacturers is to produce or something development Random Access Memory (SDRAM) new to increase the performance of the computer, DDR double data rate ( also called DDR 1) is a new interface I. INTRODUCTION method was developed, this made data transfer on both the In the twenty-first century with technology developments, rising and falling edges of the clock signal it has the ability to the entry of the computer at all areas of scientific and social transfer data twice faster than earlier versions, such as life. With the increased demand for computer and the large SDRAM, the had used lower clock rate (100-200MHz), less volume of data has become the task of manufacturing power (2.5v) and high speed(1600-3200 MB/s). -

Technical Note Is to Provide an Figure 9: DQS WRITE Postamble and Preamble

TN-46-05 GENERAL DDR SDRAM FUNCTIONALITY TECHNICAL GENERAL DDR SDRAM NOTE FUNCTIONALITY INTRODUCTION The migration from single data rate synchronous Table of Contents DRAM (SDR) to double data rate synchronous DRAM DDR vs. SDR Functionality ............................... 2 (DDR) memory is upon us. Although there are many Table 1: SDR to DDR Quick Reference ................. 1 similarities, DDR technology also provides notable Figure 1: Functional Block Diagram .................... 2 product enhancements. Figure 4: Example of DDR Command Bus .......... 3 In general, double data rate memory provides 2n-Prefetch Architecture ................................. 3 source-synchronous data capture at a rate of twice the Figure 2: Block Diagram 2n-Prefetch READ ........ 3 clock frequency. Therefore, a DDR266 device with a Figure 3: Block Diagram 2n-Prefetch WRITE ....... 3 clock frequency of 133 MHz has a peak data transfer rate of 266 Mb/s or 2.1 GB/s for a x64 DIMM. This is Minimum Time Slots ........................................ 3 accomplished by utilizing a 2n-prefetch architecture Figure 5: 2n-Prefetch READ Slot Timing ............. 4 where the internal data bus is twice the width of the Figure 6: 2n-Prefetch WRITE Slot Timing ............ 5 external data bus and data capture occurs twice per Figure 7: READ Command Slots ........................... 6 clock cycle. To provide high-speed signal integrity, the Strobe-Based Data Bus ..................................... 4 DDR SDRAM utilizes a bidirectional data strobe, Preamble and Postamble ................................. 7 SSTL_2 interface with differential inputs and clocks. Figure 8: DQS READ Postamble and Preamble ... 7 The objective of this technical note is to provide an Figure 9: DQS WRITE Postamble and Preamble . 8 overview of the 2n-prefetch architecture, a strobe-based SSTL_2 Interface .............................................. -

Design and Implementation of High Speed DDR SDRAM Controller on FPGA

International Journal of Engineering Research & Technology (IJERT) ISSN: 2278-0181 Vol. 4 Issue 07, July-2015 Design and Implementation of High Speed DDR SDRAM Controller on FPGA Veena H K Dr. A H Masthan Ali M.Tech Student, Department of ECE, Associate Professor, Department of ECE, Sambhram Institute of Technology, Bangalore, Sambhram Institute of Technology, Bangalore, Karnataka, India Karnataka, India Abstract — The dedicated memory controller is important is and column. To point to a location in the memory these three the applications in high end applications where it doesn’t are mandatory. The ACTIVE command signal along with contains microprocessors. Command signals for memory registered address bits point to the specific bank and row to be refresh, read and write operation and SDRAM initialisation has accessed. And column is given by READ/WRITE signal been provided by memory controller. Our work will focus on along with the registered address bits that shall point to a FPGA implementation of Double Data Rate (DDR) SDRAM location for burst access. The DDR SDRAM interface makes controller. The DDR SDRAM controller is located in between higher transfer rates possible compared to single data rate the DDR SDRAM and bus master. The operations of DDR (SDR) SDRAM, by more firm control of the timing of the SDRAM controller is to simplify the SDRAM command data and clock signals. Implementations frequently have to use interface to the standard system read/ write interface and also schemes such as phase-locked loops (PLL) and self- optimization of the access time of read/write cycle. The proposed design will offers effective power utilization, reduce the gate calibration to reach the required timing precision [1][2]. -

AN 436: Using DDR3 SDRAM in Stratix III and Stratix IV Devices.Pdf

AN 436: Using DDR3 SDRAM in Stratix III and Stratix IV Devices © November 2008 AN-436-4.0 Introduction DDR3 SDRAM is the latest generation of DDR SDRAM technology, with improvements that include lower power consumption, higher data bandwidth, enhanced signal quality with multiple on-die termination (ODT) selection and output driver impedance control. DDR3 SDRAM brings higher memory performance to a broad range of applications, such as PCs, embedded processor systems, image processing, storage, communications, and networking. Although DDR2 SDRAM is currently the more popular SDRAM, to save system power and increase system performance you should consider using DDR3 SDRAM. DDR3 SDRAM offers lower power by using 1.5 V for the supply and I/O voltage compared to the 1.8-V supply and I/O voltage used by DDR2 SDRAM. DDR3 SDRAM also has better maximum throughput compared to DDR2 SDRAM by increasing the data rate per pin and the number of banks (8 banks are standard). 1 The Altera® ALTMEMPHY megafunction and DDR3 SDRAM high-performance controller only support local interfaces running at half the rate of the memory interface. Altera Stratix® III and Stratix IV devices support DDR3 SDRAM interfaces with dedicated DQS, write-, and read-leveling circuitry. Table 1 displays the maximum clock frequency for DDR3 SDRAM in Stratix III devices. Table 1. DDR3 SDRAM Maximum Clock Frequency Supported in Stratix III Devices (Note 1), (2) Speed Grade fMAX (MHz) –2 533 (3) –3 and I3 400 –4, 4L, and I4L at 1.1 V 333 (4), (5) –4, 4L, and I4L at 0.9 V Not supported Notes to Table 1: (1) Numbers are preliminary until characterization is final. -

High Bandwidth Memory for Graphics Applications Contents

High Bandwidth Memory for Graphics Applications Contents • Differences in Requirements: System Memory vs. Graphics Memory • Timeline of Graphics Memory Standards • GDDR2 • GDDR3 • GDDR4 • GDDR5 SGRAM • Problems with GDDR • Solution ‐ Introduction to HBM • Performance comparisons with GDDR5 • Benchmarks • Hybrid Memory Cube Differences in Requirements System Memory Graphics Memory • Optimized for low latency • Optimized for high bandwidth • Short burst vector loads • Long burst vector loads • Equal read/write latency ratio • Low read/write latency ratio • Very general solutions and designs • Designs can be very haphazard Brief History of Graphics Memory Types • Ancient History: VRAM, WRAM, MDRAM, SGRAM • Bridge to modern times: GDDR2 • The first modern standard: GDDR4 • Rapidly outclassed: GDDR4 • Current state: GDDR5 GDDR2 • First implemented with Nvidia GeForce FX 5800 (2003) • Midway point between DDR and ‘true’ DDR2 • Stepping stone towards DDR‐based graphics memory • Second‐generation GDDR2 based on DDR2 GDDR3 • Designed by ATI Technologies , first used by Nvidia GeForce FX 5700 (2004) • Based off of the same technological base as DDR2 • Lower heat and power consumption • Uses internal terminators and a 32‐bit bus GDDR4 • Based on DDR3, designed by Samsung from 2005‐2007 • Introduced Data Bus Inversion (DBI) • Doubled prefetch size to 8n • Used on ATI Radeon 2xxx and 3xxx, never became commercially viable GDDR5 SGRAM • Based on DDR3 SDRAM memory • Inherits benefits of GDDR4 • First used in AMD Radeon HD 4870 video cards (2008) • Current -

DDR3 SODIMM Product Datasheet

DDR3 SODIMM Product Datasheet 廣 穎 電 通 股 份 有 限 公 司 Silicon Power Computer & Communications Inc. TEL: 886-2 8797-8833 FAX: 886-2 8751-6595 台北市114內湖區洲子街106號7樓 7F, No.106, ZHO-Z ST. NEIHU DIST, 114, TAIPEI, TAIWAN, R.O.C This document is a general product description and is subject to change without notice DDR3 SODIMM Product Datasheet Index Index...................................................................................................................................................................... 2 Revision History ................................................................................................................................................ 3 Description .......................................................................................................................................................... 4 Features ............................................................................................................................................................... 5 Pin Assignments................................................................................................................................................ 7 Pin Description................................................................................................................................................... 8 Environmental Requirements......................................................................................................................... 9 Absolute Maximum DC Ratings.................................................................................................................... -

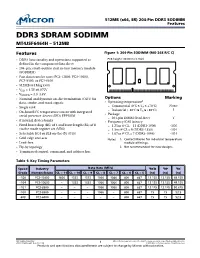

512MB (X64, SR) 204-Pin DDR3 SODIMM Features DDR3 SDRAM SODIMM MT4JSF6464H – 512MB

512MB (x64, SR) 204-Pin DDR3 SODIMM Features DDR3 SDRAM SODIMM MT4JSF6464H – 512MB Features Figure 1: 204-Pin SODIMM (MO-268 R/C C) • DDR3 functionality and operations supported as PCB height: 30.0mm (1.18in) defined in the component data sheet • 204-pin, small-outline dual in-line memory module (SODIMM) • Fast data transfer rates: PC3-12800, PC3-10600, PC3-8500, or PC3-6400 • 512MB (64 Meg x 64) • VDD = 1.5V ±0.075V • VDDSPD = 3.0–3.6V • Nominal and dynamic on-die termination (ODT) for Options Marking 1 data, strobe, and mask signals • Operating temperature – Commercial (0°C ≤ T ≤ +70°C) None • Single rank A – Industrial (–40°C ≤ T ≤ +85°C) I • On-board I2C temperature sensor with integrated A Package serial presence-detect (SPD) EEPROM • – 204-pin DIMM (lead-free) Y 8 internal device banks • • Frequency/CAS latency • Fixed burst chop (BC) of 4 and burst length (BL) of 8 – 1.25ns @ CL = 11 (DDR3-1600) -1G6 via the mode register set (MRS) – 1.5ns @ CL = 9 (DDR3-1333) -1G4 • Selectable BC4 or BL8 on-the-fly (OTF) – 1.87ns @ CL = 7 (DDR3-1066) -1G1 • Gold edge contacts Notes: 1. Contact Micron for industrial temperature • Lead-free module offerings. • Fly-by topology 2. Not recommended for new designs. • Terminated control, command, and address bus Table 1: Key Timing Parameters Speed Industry Data Rate (MT/s) tRCD tRP tRC Grade Nomenclature CL = 11 CL = 10 CL = 9 CL = 8 CL = 7 CL = 6 CL = 5 (ns) (ns) (ns) -1G6 PC3-12800 1600 1333 1333 1066 1066 800 667 13.125 13.125 48.125 -1G4 PC3-10600 – 1333 1333 1066 1066 800 667 13.125 13.125 49.125 -1G1 PC3-8500 – – – 1066 1066 800 667 13.125 13.125 50.625 -1G0 PC3-8500 – – – 1066 – 800 667 15 15 52.5 -80B PC3-6400 – – – – – 800 667 15 15 52.5 PDF: 09005aef82b2f090 Micron Technology, Inc. -

"Low-Power Support Using Texas Instruments SN74SSTV16857 and SN74SSTV16859"

Application Report SCEA020 - February 2001 Low-Power Support Using Texas Instruments SN74SSTV16857 and SN74SSTV16859 DDR-DIMM Registers Stephen M. Nolan Standard Linear & Logic ABSTRACT The Texas Instruments SN74SSTV16857 and SN74SSTV16859 registers support the low-power mode of the DDR-DIMM. This application report explains the low-power mode and the features of the registers that support the low-power mode. Also, the considerations that the system designer must be aware of when implementing the low-power state of a registered memory module are explained. The sequence that must be followed to utilize the register properly is detailed, including the interpretation of the associated register timing specifications. Finally, the different static- and dynamic-current specifications are analyzed, along with examples of how to calculate the dynamic operating current requirement of the registers. Contents Introduction . 2 Background and Features of Registers. 5 Sequence of Entering and Exiting the Low-Power State. 6 Considerations of Register. 6 How tinact and tact Are Characterized. 9 Dynamic- and Static-Current Specifications. 9 ICC Static Standby Current. 9 ICC Static Operating Current. 10 ICCD Dynamic Operating Current – Clock Only. 10 ICCD Dynamic Operating Current – Each Data Input. 11 Calculating Power Consumption in the Application. 11 Summary . 12 Glossary . 12 List of Figures 1 SN74SSTV16857 . 3 2 SN74SSTV16859 . 4 3 Parameter Measurement Information (VDD = 2.5 V ± 0.2 V). 9 1 SCEA020 Introduction The widespread demand for more main-memory capacity and bandwidth in computer systems has lead to the development of the JEDEC standard for DDR-SDRAM-based, 184-pin, registered memory modules. These DDR DIMMs provide twice the data-bus bandwidth of previous-generation single-data-rate (SDR) memory systems. -

AMD Athlon Northbridge with 4X AGP and Next Generation Memory

AMD AthlonTM Northbridge with 4x AGP and Next Generation Memory Subsystem Chetana Keltcher, Jim Kelly, Ramani Krishnan, John Peck, Steve Polzin, Sridhar Subramanian, Fred Weber Advanced Micro Devices, Sunnyvale, CA * AMD Athlon was formerly code-named AMD-K7 1 Outline of the Talk • Introduction • Architecture • Clocking and Gearbox • Performance • Silicon Statistics • Conclusion 2 Introduction • NorthBridge: “Electronic traffic cop” that directs data flow between the main memory and the rest of the system • Bridge the gap between processor speed and memory speed – Higher bandwidth busses • Example: AGP 2.0, EV6 and AMD Athlon system bus – Better memory technology • Example: Double data rate SDRAM, RDRAM 3 System Block Diagram 100MHz for PC-100 SDRAM AMD Athlon 200MHz for DDR SDRAM System Bus 533-800MHz for RDRAM DRAM CPU 200 MHz, 64 bits NorthBridge Scaleable to 400 MHz 66MHz, 32 bits (1x,2x,4x) Graphics CPU AGP Bus Device 33MHz, 32 bits PCI PCI Bus Devices SouthBridge ISA Bus IDE USBSerial Printer Port Port 4 Features of the AMD Athlon Northbridge • Can support one or two AMD Athlon or EV6 processors • 200MHz data rate (scaleable to 400MHz), 64-bit processor interface • 33MHz, 32-bit PCI 2.2 compliant interface • 66MHz, 32-bit AGP 2.0 compliant interface supports 1x, 2x and 4x data transfer modes • Versions for SDRAM, DDR SDRAM and RDRAM memory • Single bit error correction and multiple bit error detection (ECC) • Distributed Graphics Aperture Remapping Table (GART) • Power management features including powerdown self-refresh of SDRAM -

Powerpc 440GP Embedded Processor

PRODUCT BRIEF PowerPC 440GP Embedded Processor With speeds of up to 500 MHz and a rich peripheral mix, the PowerPC 440GP embedded processor offers exceptional performance, design flexibility, and robust features for demanding networking, storage and other embedded applications. Its high level of integration — including on-chip SRAM, low power dissipation and small footprint simplify board design and help reduce manufacturing costs. Benefits • Delivers 400 MHz to 500 MHz per- The PowerPC 440 Core link speed of 10 or 100 Mbytes/s in full- or half- To enhance overall throughput, the PowerPC 440 duplex mode, and supports one MII, two RMII or formance (CPU) superscalar core incorporates a 7-stage pipeline two SMII ports. • State-of -the-art peripherals and executes up to two instructions per cycle. Its External Interface including DDR SDRAM and PCI-X large 32-Kbyte data cache and 32-Kbyte instruction cache are 64-way set-associative. To accommodate connectivity with other devices, • On-chip Ethernet for built-in Versatile configurations enhance performance the PowerPC 440GP offers a 32-bit bus supporting up to eight ROM, EPROM, SRAM, Flash, or slave networking tuning while optional parity protection preserves data integrity. For additional system performance, peripheral I/O devices. External bus mastering is • Performance-enhancing features the PowerPC 440 core includes dynamic branch also supported. including superscalar operation, prediction and 24 digital signal processing (DSP) Standard Peripherals large L1 caches, and high-speed bus instructions, as well as non-blocking caches that Functionality is further enhanced with a variety of can be managed in either write-through or write- technology on-chip peripherals.