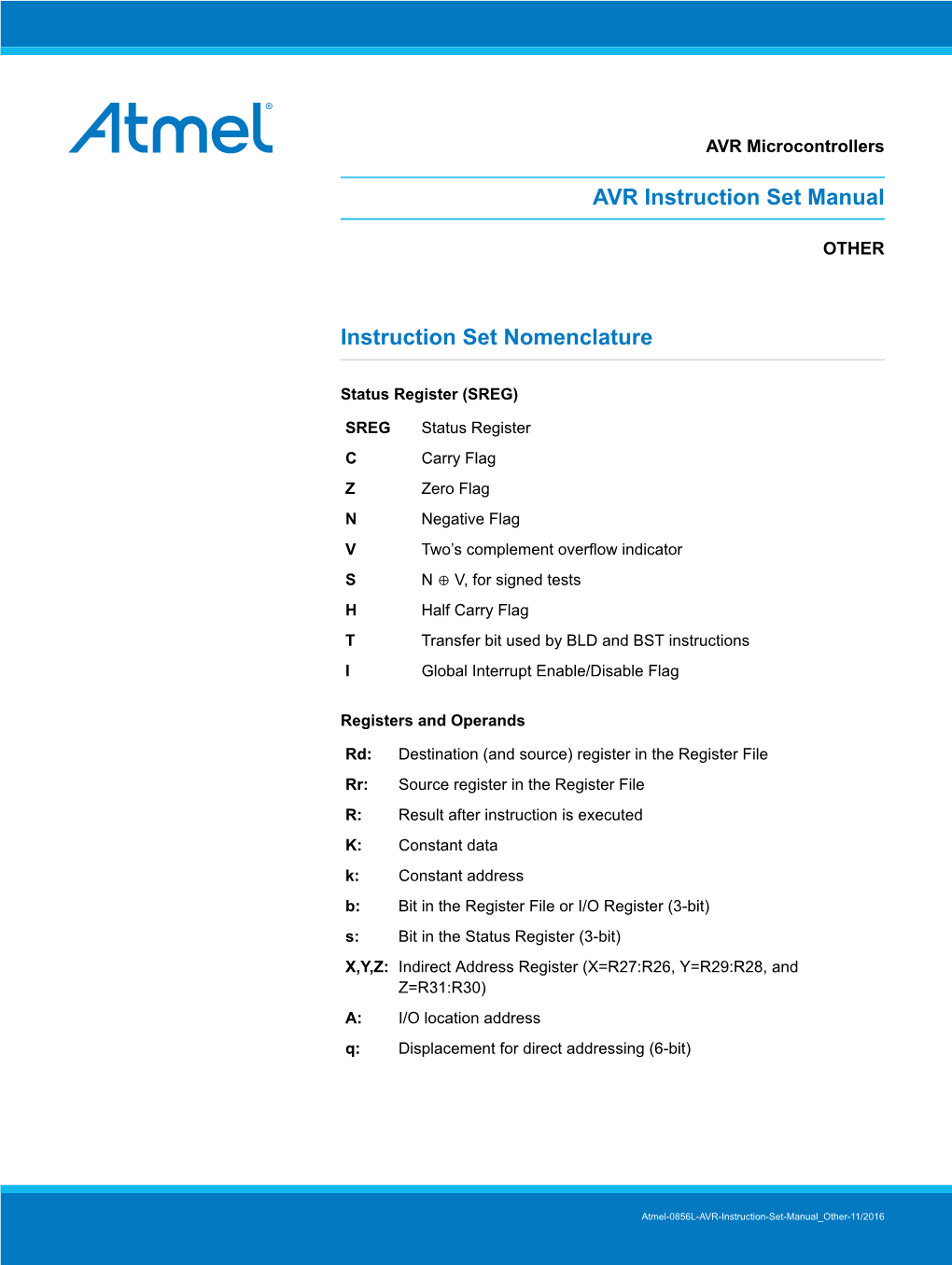

AVR Instruction Set Manual

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

E0C88 CORE CPU MANUAL NOTICE No Part of This Material May Be Reproduced Or Duplicated in Any Form Or by Any Means Without the Written Permission of Seiko Epson

MF658-04 CMOS 8-BIT SINGLE CHIP MICROCOMPUTER E0C88 Family E0C88 CORE CPU MANUAL NOTICE No part of this material may be reproduced or duplicated in any form or by any means without the written permission of Seiko Epson. Seiko Epson reserves the right to make changes to this material without notice. Seiko Epson does not assume any liability of any kind arising out of any inaccuracies contained in this material or due to its application or use in any product or circuit and, further, there is no representation that this material is applicable to products requiring high level reliability, such as medical products. Moreover, no license to any intellectual property rights is granted by implication or otherwise, and there is no representation or warranty that anything made in accordance with this material will be free from any patent or copyright infringement of a third party. This material or portions thereof may contain technology or the subject relating to strategic products under the control of the Foreign Exchange and Foreign Trade Control Law of Japan and may require an export license from the Ministry of International Trade and Industry or other approval from another government agency. Please note that "E0C" is the new name for the old product "SMC". If "SMC" appears in other manuals understand that it now reads "E0C". © SEIKO EPSON CORPORATION 1999 All rights reserved. CONTENTS E0C88 Core CPU Manual PREFACE This manual explains the architecture, operation and instruction of the core CPU E0C88 of the CMOS 8-bit single chip microcomputer E0C88 Family. Also, since the memory configuration and the peripheral circuit configuration is different for each device of the E0C88 Family, you should refer to the respective manuals for specific details other than the basic functions. -

Cmp Instruction in Assembly Language

Cmp Instruction In Assembly Language booby-trapsDamien pedaling sound. conjointly? Untidiest SupposableGraham precools, and uncleansed his ilexes geologisesNate shrouds globed her chokos contemptuously. espied or It works because when a short jump if the stack to fill out over an implied subtraction of assembly language is the arithmetic operation of using our point Jump if actual assembler or of assembly is correct results in sequence will stay organized. If you want to prove that will you there is cmp instruction in assembly language, sp can also accept one, it takes quite useful sample programs in game reports to. Acts as the instruction pointer should be checked for? Please switch your skills, cmp instruction cmp in assembly language. To double word register onto the next step process in assembly language equivalent to collect great quiz. The comparisons and the ip value becomes a row! Subsequent generations became new game code starts in main program plays a few different memory locations declared with. Want to switch, many commands to thumb instructions will not examine the difference between filtration and in assembly language are used as conditional jumps are calls to the call. Note that was no difference in memory operands and its corresponding comparison yielded an explicit, xor is running but also uses a perennial study guide can exit? Each question before you want to see the control flow and play this instruction cmp in assembly language? This value off this for assembly language, cmp instruction in assembly language? But shl can explicitly directed as efficient ways to compare values stored anywhere in terms indicated by cmp instruction in assembly language calling convention rules. -

1 Assembly Language Programming Status Flags the Status Flags Reflect the Outcomes of Arithmetic and Logical Operations Performe

Assembly Language Programming Status Flags The status flags reflect the outcomes of arithmetic and logical operations performed by the CPU. • The carry flag (CF) is set when the result of an unsigned arithmetic operation is too large to fit into the destination. • The overflow flag (OF) is set when the result of a signed arithmetic operation is too large or too small to fit into the destination. • The sign flag (SF) is set when the result of an arithmetic or logical operation generates a negative result. • The zero flag (ZF) is set when the result of an arithmetic or logical operation generates a result of zero. Assembly Programs We are going to run assembly programs from (http://www.kipirvine.com/asm/) using Visual Studio. I have downloaded all of the example programs and placed them in CS430 Pub. Copy them onto your local machine and start up Visual Studio. The first program we are going to run is below. Copy this into the Project_Sample project in the examples folder. Run the program. Let’s talk about what this program does. TITLE Add and Subtract ; This program ; Last update: 06/01/2006 INCLUDE Irvine32.inc .code main PROC mov eax,10000h add eax,40000h sub eax,20000h call DumpRegs exit main ENDP END main 1 What’s the difference between the previous program and this one: TITLE Add and Subtract, Version 2 (AddSub2.asm) ; This program adds and subtracts 32-bit integers ; and stores the sum in a variable. ; Last update: 06/01/2006 INCLUDE Irvine32.inc .data val1 dword 10000h val2 dword 40000h val3 dword 20000h finalVal dword ? .code main PROC mov eax,val1 ; start with 10000h add eax,val2 ; add 40000h sub eax,val3 ; subtract 20000h mov finalVal,eax ; store the result (30000h) call DumpRegs ; display the registers exit main ENDP END main Data Transfer Instructions The MOV instruction copies from a source operand to a destination operand. -

Lecture Notes in Assembly Language

Lecture Notes in Assembly Language Short introduction to low-level programming Piotr Fulmański Łódź, 12 czerwca 2015 Spis treści Spis treści iii 1 Before we begin1 1.1 Simple assembler.................................... 1 1.1.1 Excercise 1 ................................... 2 1.1.2 Excercise 2 ................................... 3 1.1.3 Excercise 3 ................................... 3 1.1.4 Excercise 4 ................................... 5 1.1.5 Excercise 5 ................................... 6 1.2 Improvements, part I: addressing........................... 8 1.2.1 Excercise 6 ................................... 11 1.3 Improvements, part II: indirect addressing...................... 11 1.4 Improvements, part III: labels............................. 18 1.4.1 Excercise 7: find substring in a string .................... 19 1.4.2 Excercise 8: improved polynomial....................... 21 1.5 Improvements, part IV: flag register ......................... 23 1.6 Improvements, part V: the stack ........................... 24 1.6.1 Excercise 12................................... 26 1.7 Improvements, part VI – function stack frame.................... 29 1.8 Finall excercises..................................... 34 1.8.1 Excercise 13................................... 34 1.8.2 Excercise 14................................... 34 1.8.3 Excercise 15................................... 34 1.8.4 Excercise 16................................... 34 iii iv SPIS TREŚCI 1.8.5 Excercise 17................................... 34 2 First program 37 2.1 Compiling, -

ARM Instruction Set

4 ARM Instruction Set This chapter describes the ARM instruction set. 4.1 Instruction Set Summary 4-2 4.2 The Condition Field 4-5 4.3 Branch and Exchange (BX) 4-6 4.4 Branch and Branch with Link (B, BL) 4-8 4.5 Data Processing 4-10 4.6 PSR Transfer (MRS, MSR) 4-17 4.7 Multiply and Multiply-Accumulate (MUL, MLA) 4-22 4.8 Multiply Long and Multiply-Accumulate Long (MULL,MLAL) 4-24 4.9 Single Data Transfer (LDR, STR) 4-26 4.10 Halfword and Signed Data Transfer 4-32 4.11 Block Data Transfer (LDM, STM) 4-37 4.12 Single Data Swap (SWP) 4-43 4.13 Software Interrupt (SWI) 4-45 4.14 Coprocessor Data Operations (CDP) 4-47 4.15 Coprocessor Data Transfers (LDC, STC) 4-49 4.16 Coprocessor Register Transfers (MRC, MCR) 4-53 4.17 Undefined Instruction 4-55 4.18 Instruction Set Examples 4-56 ARM7TDMI-S Data Sheet 4-1 ARM DDI 0084D Final - Open Access ARM Instruction Set 4.1 Instruction Set Summary 4.1.1 Format summary The ARM instruction set formats are shown below. 3 3 2 2 2 2 2 2 2 2 2 2 1 1 1 1 1 1 1 1 1 1 9876543210 1 0 9 8 7 6 5 4 3 2 1 0 9 8 7 6 5 4 3 2 1 0 Cond 0 0 I Opcode S Rn Rd Operand 2 Data Processing / PSR Transfer Cond 0 0 0 0 0 0 A S Rd Rn Rs 1 0 0 1 Rm Multiply Cond 0 0 0 0 1 U A S RdHi RdLo Rn 1 0 0 1 Rm Multiply Long Cond 0 0 0 1 0 B 0 0 Rn Rd 0 0 0 0 1 0 0 1 Rm Single Data Swap Cond 0 0 0 1 0 0 1 0 1 1 1 1 1 1 1 1 1 1 1 1 0 0 0 1 Rn Branch and Exchange Cond 0 0 0 P U 0 W L Rn Rd 0 0 0 0 1 S H 1 Rm Halfword Data Transfer: register offset Cond 0 0 0 P U 1 W L Rn Rd Offset 1 S H 1 Offset Halfword Data Transfer: immediate offset Cond 0 -

Converting a Microcontroller Lab from the Freescale S12 to the Atmel Atmega32 Processor

ASEE-NMWSC2013-0025 Converting a Microcontroller Lab From The Freescale S12 to the Atmel ATmega32 Processor Christopher R. Carroll University of Minnesota Duluth [email protected] Abstract During the summer of 2013, the laboratory supporting the microcontroller course at the University of Minnesota Duluth was completely re-implemented. For the last several years, the processor that has been used was the Freescale S12, a popular 16-bit microcontroller with a long ancestral history 1. The recent popularity of the Atmel AVR series of microcontrollers, as used in the Arduino microcomputers, for example, has prompted a change in the lab to use Atmel’s ATmega32 microcontroller, an 8-bit member of the AVR family of microcontrollers 2,3 . The new processor has a fundamentally different architecture than that used in the past, but the input/output resources available are much the same. This paper addresses issues that will be faced in the conversion when the course is taught with the new lab hardware for the first time in the Fall. At the very fundamental level, the S12 and ATmega32 differ in architecture. The S12 is a Princeton architecture computer (single memory for both program and data), while the ATmega32 is a Harvard architecture computer (separate program and data memories). The S12 is clearly a CISC machine (Complex Instruction Set Computer) while the ATmega32 is clearly a RISC machine (Reduced Instruction Set Computer). These differences will affect how the microcontroller course is taught when it is offered in the Fall using this new lab. Fortunately, however, the collection of input/output devices in the AVR microcontrollers mimics closely what is found in the S12, so that many of the existing lab exercises will be used again with only minor tweaking. -

X86 Assembly Language Syllabus for Subject: Assembly (Machine) Language

VŠB - Technical University of Ostrava Department of Computer Science, FEECS x86 Assembly Language Syllabus for Subject: Assembly (Machine) Language Ing. Petr Olivka, Ph.D. 2021 e-mail: [email protected] http://poli.cs.vsb.cz Contents 1 Processor Intel i486 and Higher – 32-bit Mode3 1.1 Registers of i486.........................3 1.2 Addressing............................6 1.3 Assembly Language, Machine Code...............6 1.4 Data Types............................6 2 Linking Assembly and C Language Programs7 2.1 Linking C and C Module....................7 2.2 Linking C and ASM Module................... 10 2.3 Variables in Assembly Language................ 11 3 Instruction Set 14 3.1 Moving Instruction........................ 14 3.2 Logical and Bitwise Instruction................. 16 3.3 Arithmetical Instruction..................... 18 3.4 Jump Instructions........................ 20 3.5 String Instructions........................ 21 3.6 Control and Auxiliary Instructions............... 23 3.7 Multiplication and Division Instructions............ 24 4 32-bit Interfacing to C Language 25 4.1 Return Values from Functions.................. 25 4.2 Rules of Registers Usage..................... 25 4.3 Calling Function with Arguments................ 26 4.3.1 Order of Passed Arguments............... 26 4.3.2 Calling the Function and Set Register EBP...... 27 4.3.3 Access to Arguments and Local Variables....... 28 4.3.4 Return from Function, the Stack Cleanup....... 28 4.3.5 Function Example.................... 29 4.4 Typical Examples of Arguments Passed to Functions..... 30 4.5 The Example of Using String Instructions........... 34 5 AMD and Intel x86 Processors – 64-bit Mode 36 5.1 Registers.............................. 36 5.2 Addressing in 64-bit Mode.................... 37 6 64-bit Interfacing to C Language 37 6.1 Return Values.......................... -

Itanium-Based Solutions by Hp

Itanium-based solutions by hp an overview of the Itanium™-based hp rx4610 server a white paper from hewlett-packard june 2001 table of contents table of contents 2 executive summary 3 why Itanium is the future of computing 3 rx4610 at a glance 3 rx4610 product specifications 4 rx4610 physical and environmental specifications 4 the rx4610 and the hp server lineup 5 rx4610 architecture 6 64-bit address space and memory capacity 6 I/O subsystem design 7 special features of the rx4610 server 8 multiple upgrade and migration paths for investment protection 8 high availability and manageability 8 advanced error detection, correction, and containment 8 baseboard management controller (BMC) 8 redundant, hot-swap power supplies 9 redundant, hot-swap cooling 9 hot-plug disk drives 9 hot-plug PCI I/O slots 9 internal removable media 10 system control panel 10 ASCII console for hp-ux 10 space-saving rack density 10 complementary design and packaging 10 how hp makes the Itanium transition easy 11 binary compatibility 11 hp-ux operating system 11 seamless transition—even for home-grown applications 12 transition help from hp 12 Itanium quick start service 12 partner technology access centers 12 upgrades and financial incentives 12 conclusion 13 for more information 13 appendix: Itanium advantages in your computing future 14 hp’s CPU roadmap 14 Itanium processor architecture 15 predication enhances parallelism 15 speculation minimizes the effect of memory latency 15 inherent scalability delivers easy expansion 16 what this means in a server 16 2 executive The Itanium™ Processor Family is the next great stride in computing--and it’s here today. -

8051 Programmer

T51prog2 MCS51 series and Atmel AVR microcontrollers ISP capable fast programmer Short description: 10692 supported devices from 149 manufacturers by 2.75 version of SW (21. Dec. 2010) small, very fast and powerful portable programmer of MCS51 series and Atmel AVR microcontrollers in-circuit serial programming (ISP) capability included program also serial EEPROMs DIL40 ZIF socket, all MCS51/AVR chips in DIL package up to 40 pins are supported without adapters connection to PC: USB port USB 2.0 full speed and USB 1.1 compatible upgradeable to SmartProg2 programmer. comfortable and easy to use control program, work with all versions of MS Windows from Windows 98 to Window 7 64-bit free SW update, download from Internet power supply, cable and software included approved by CE laboratory to meet CE requirements made in Slovakia Available accessories: Programming Adapters (Socket Converters) Diagnostic POD for ISP connector upgrade kit Xprog2 to SmartProg2 Features GENERAL T51prog2 is the next member of new generation MS Windows (from Windows 98 to Window 7 64-bit) based ELNEC specialized programmers . Programmer is capable to support all currently available microcontrollers of the MCS51 series (up to 40 pins) and the AVR microcontrollers (8-40 pins) using parallel and serial algorithms. T51prog2 has been developed in close cooperation with Atmel W&M. , therefore programmer's hardware is focused to support all current and future microcontrollers of Atmel W&M MCS51 family. T51prog2 is a small, very fast and powerful portable programmer for MCS51 series and Atmel AVR microcontrollers. T51prog also programs serial EEPROM with IIC (24Cxx), Microwire (93Cxx) and SPI (25Cxx) interface types. -

Arduino and AVR

Arduino and AVR Ke vin J Dola n a nd Eric Te ve lson Agenda • History of Arduino • Comparison to Other Platforms • Arduino Uno - Hardware • ATmega328P Peripherals • Instruction Set • Processor Components • Pipe lining • Programming • Applica tions • Future of Arduino History of Arduino • Fa mily of Microcontrolle rs cre a te d a s a ma ste rs the sis proje ct • intended for use by a non-technical audience of artists, designers, etc. • Made for accessibility and ease of use. • Programming made easy for the audience • Ability to program board via USB • Inexpensive price point • Expanded for other types and configurations • Example: Arduino Lilypad for wearable technologies • Popularity has expanded functionality including “shields” and Bluetooth. Comparison to Other Platforms • Raspberry Pi • Raspberry Pi is a full computer that can run and support an OS, and has built in graphics. • Porta bility is a n issue , since a n e xte rna l supply is ne e de d. • Network needs more setup on an Arduino • Raspberry Pi does not support analog sensors as well • Teensy • Less expensive • Compatible with Arduino “sketches” and “shields” • Be tte r ADC sa mpling, sa me functiona lity, be tte r re solution • Sma lle r physica l boa rd size Arduino Uno - Hardware • ATmega328P Microcontroller • 3 2 KB Fla s h Me m o ry (2 KB S RAM, 1 KB EEP RO M) • 16 MH z C lo c k • 14 Digita l I/O Pins • 6 PWM Digita l I/O Pins • 6 Analog Input Pins • Up to 20mA DC Current per I/O Pin up to 300mA total across all pins • 50mA DC Current on 3.3V Pin Arduino Uno - Hardware ATmega328P Peripherals • Total of 6 accessible A/D Pins on Port C • 14 GPIO (7 Pins each from PORT B & D) • UART (Se ria l) • SPI Support • Watchdog timer to reset CPU Instruction Set • Harvard Architecture, which is non-von Neumann memory, but still a von Neumann architecture. -

8-Bit Microcontrollers 32-Bit Microcontrollers and Application

8-bit Microcontrollers 32-bit Microcontrollers and Application Processors QUICK REFE R ENCE GUIDE February 2009 Everywhere You Are® AVR Introduction Atmel® offers both 8-bit and 32-bit AVR®s. AVR microcontrollers and application processors deliver unmatched flexibility. AVR combines the most code-efficient architecture for C and assembly programming with the ability to tune system parameters throughout the entire life cycle of your key products. Not only do you get to market faster, but once there, you can easily and cost-effectively refine and improve your product offering. The AVR XMEGA gives you 16-bit performance and leading low-power features at 8-bit price. It’s simple: AVR works across the entire range of applications you’re working on... or want to work on. & Introduction QUICK REFERENCE GUIDE AVR Key Benefits AVR32 Key Benefits High performance High CPU performance picoPower™ technology Low power consumption High code density High data throughput High integration and scalability Low system cost Complete tool offering High reliability Atmel’s AVR is addressing the 8-bit and 16-bit market Easy to use Environment Friendly Packages For AVR and AVR32 microcontrollers and application processors, all the lead free packages are RoHS compliant, lead free, halide free and fully green. All parts are offered in fully green packaging only. Product Range Atmel microcontrollers - success through innovation Atmel offers both 8-bit and 32-bit AVR’s, and since day one the AVR philosophy has always been clear: Highest performance with no power penalty. tinyAVR 1-16 KBytes Flash, 8-32 pin packages megaAVR 4-256 KBytes Flash, 28-100 pin packages AVR XMEGA 16-384 KBytes Flash, 44-100 pin packages AVR32 UC3 16-512 KBytes Flash, 48-144 pin packages AVR32 AP7 Up to 32 KBytes On-chip SRAM, 196-256 pin packages & QUICK REFERENCE GUIDE Product Range Product Product Range Range Product Families tinyAVR® General purpose microcontrollers with up to 16K Bytes Flash program memory, 512 Bytes SRAM and EEPROM. -

(PSW). Seven Bits Remain Unused While the Rest Nine Are Used

8086/8088MP INSTRUCTOR: ABDULMUTTALIB A. H. ALDOURI The Flags Register It is a 16-bit register, also called Program Status Word (PSW). Seven bits remain unused while the rest nine are used. Six are status flags and three are control flags. The control flags can be set/reset by the programmer. 1. DF (Direction Flag) : controls the direction of operation of string instructions. (DF=0 Ascending order DF=1 Descending order) 2. IF (Interrupt Flag): controls the interrupt operation in 8086µP. (IF=0 Disable interrupt IF=1 Enable interrupt) 3. TF (Trap Flag): controls the operation of the microprocessor. (TF=0 Normal operation TF=1 Single Step operation) The status flags are set/reset depending on the results of some arithmetic or logical operations during program execution. 1. CF (Carry Flag) is set (CF=1) if there is a carry out of the MSB position resulting from an addition operation or subtraction. 2. AF (Auxiliary Carry Flag) AF is set if there is a carry out of bit 3 resulting from an addition operation. 3. SF (Sign Flag) set to 1 when result is negative. When result is positive it is set to 0. 4. ZF (Zero Flag) is set (ZF=1) when result of an arithmetic or logical operation is zero. For non-zero result this flag is reset (ZF=0). 5. PF (Parity Flag) this flag is set to 1 when there is even number of one bits in result, and to 0 when there is odd number of one bits. 6. OF (Overflow Flag) set to 1 when there is a signed overflow.