Fm Demodulation Using a Digital Radio and Digital Signal Processing

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Discrete Cosine Transform Based Image Fusion Techniques VPS Naidu MSDF Lab, FMCD, National Aerospace Laboratories, Bangalore, INDIA E.Mail: [email protected]

View metadata, citation and similar papers at core.ac.uk brought to you by CORE provided by NAL-IR Journal of Communication, Navigation and Signal Processing (January 2012) Vol. 1, No. 1, pp. 35-45 Discrete Cosine Transform based Image Fusion Techniques VPS Naidu MSDF Lab, FMCD, National Aerospace Laboratories, Bangalore, INDIA E.mail: [email protected] Abstract: Six different types of image fusion algorithms based on 1 discrete cosine transform (DCT) were developed and their , k 1 0 performance was evaluated. Fusion performance is not good while N Where (k ) 1 and using the algorithms with block size less than 8x8 and also the block 1 2 size equivalent to the image size itself. DCTe and DCTmx based , 1 k 1 N 1 1 image fusion algorithms performed well. These algorithms are very N 1 simple and might be suitable for real time applications. 1 , k 0 Keywords: DCT, Contrast measure, Image fusion 2 N 2 (k 1 ) I. INTRODUCTION 2 , 1 k 2 N 2 1 Off late, different image fusion algorithms have been developed N 2 to merge the multiple images into a single image that contain all useful information. Pixel averaging of the source images k 1 & k 2 discrete frequency variables (n1 , n 2 ) pixel index (the images to be fused) is the simplest image fusion technique and it often produces undesirable side effects in the fused image Similarly, the 2D inverse discrete cosine transform is defined including reduced contrast. To overcome this side effects many as: researchers have developed multi resolution [1-3], multi scale [4,5] and statistical signal processing [6,7] based image fusion x(n1 , n 2 ) (k 1 ) (k 2 ) N 1 N 1 techniques. -

Digital Signals

Technical Information Digital Signals 1 1 bit t Part 1 Fundamentals Technical Information Part 1: Fundamentals Part 2: Self-operated Regulators Part 3: Control Valves Part 4: Communication Part 5: Building Automation Part 6: Process Automation Should you have any further questions or suggestions, please do not hesitate to contact us: SAMSON AG Phone (+49 69) 4 00 94 67 V74 / Schulung Telefax (+49 69) 4 00 97 16 Weismüllerstraße 3 E-Mail: [email protected] D-60314 Frankfurt Internet: http://www.samson.de Part 1 ⋅ L150EN Digital Signals Range of values and discretization . 5 Bits and bytes in hexadecimal notation. 7 Digital encoding of information. 8 Advantages of digital signal processing . 10 High interference immunity. 10 Short-time and permanent storage . 11 Flexible processing . 11 Various transmission options . 11 Transmission of digital signals . 12 Bit-parallel transmission. 12 Bit-serial transmission . 12 Appendix A1: Additional Literature. 14 99/12 ⋅ SAMSON AG CONTENTS 3 Fundamentals ⋅ Digital Signals V74/ DKE ⋅ SAMSON AG 4 Part 1 ⋅ L150EN Digital Signals In electronic signal and information processing and transmission, digital technology is increasingly being used because, in various applications, digi- tal signal transmission has many advantages over analog signal transmis- sion. Numerous and very successful applications of digital technology include the continuously growing number of PCs, the communication net- work ISDN as well as the increasing use of digital control stations (Direct Di- gital Control: DDC). Unlike analog technology which uses continuous signals, digital technology continuous or encodes the information into discrete signal states (Fig. 1). When only two discrete signals states are assigned per digital signal, these signals are termed binary si- gnals. -

How I Came up with the Discrete Cosine Transform Nasir Ahmed Electrical and Computer Engineering Department, University of New Mexico, Albuquerque, New Mexico 87131

mxT*L. BImL4L. PRocEsSlNG 1,4-5 (1991) How I Came Up with the Discrete Cosine Transform Nasir Ahmed Electrical and Computer Engineering Department, University of New Mexico, Albuquerque, New Mexico 87131 During the late sixties and early seventies, there to study a “cosine transform” using Chebyshev poly- was a great deal of research activity related to digital nomials of the form orthogonal transforms and their use for image data compression. As such, there were a large number of T,(m) = (l/N)‘/“, m = 1, 2, . , N transforms being introduced with claims of better per- formance relative to others transforms. Such compari- em- lh) h = 1 2 N T,(m) = (2/N)‘%os 2N t ,...) . sons were typically made on a qualitative basis, by viewing a set of “standard” images that had been sub- jected to data compression using transform coding The motivation for looking into such “cosine func- techniques. At the same time, a number of researchers tions” was that they closely resembled KLT basis were doing some excellent work on making compari- functions for a range of values of the correlation coef- sons on a quantitative basis. In particular, researchers ficient p (in the covariance matrix). Further, this at the University of Southern California’s Image Pro- range of values for p was relevant to image data per- cessing Institute (Bill Pratt, Harry Andrews, Ali Ha- taining to a variety of applications. bibi, and others) and the University of California at Much to my disappointment, NSF did not fund the Los Angeles (Judea Pearl) played a key role. -

Lecture 25 Demodulation and the Superheterodyne Receiver EE445-10

EE447 Lecture 6 Lecture 25 Demodulation and the Superheterodyne Receiver EE445-10 HW7;5-4,5-7,5-13a-d,5-23,5-31 Due next Monday, 29th 1 Figure 4–29 Superheterodyne receiver. m(t) 2 Couch, Digital and Analog Communication Systems, Seventh Edition ©2007 Pearson Education, Inc. All rights reserved. 0-13-142492-0 1 EE447 Lecture 6 Synchronous Demodulation s(t) LPF m(t) 2Cos(2πfct) •Only method for DSB-SC, USB-SC, LSB-SC •AM with carrier •Envelope Detection – Input SNR >~10 dB required •Synchronous Detection – (no threshold effect) •Note the 2 on the LO normalizes the output amplitude 3 Figure 4–24 PLL used for coherent detection of AM. 4 Couch, Digital and Analog Communication Systems, Seventh Edition ©2007 Pearson Education, Inc. All rights reserved. 0-13-142492-0 2 EE447 Lecture 6 Envelope Detector C • Ac • (1+ a • m(t)) Where C is a constant C • Ac • a • m(t)) 5 Envelope Detector Distortion Hi Frequency m(t) Slope overload IF Frequency Present in Output signal 6 3 EE447 Lecture 6 Superheterodyne Receiver EE445-09 7 8 4 EE447 Lecture 6 9 Super-Heterodyne AM Receiver 10 5 EE447 Lecture 6 Super-Heterodyne AM Receiver 11 RF Filter • Provides Image Rejection fimage=fLO+fif • Reduces amplitude of interfering signals far from the carrier frequency • Reduces the amount of LO signal that radiates from the Antenna stop 2/22 12 6 EE447 Lecture 6 Figure 4–30 Spectra of signals and transfer function of an RF amplifier in a superheterodyne receiver. 13 Couch, Digital and Analog Communication Systems, Seventh Edition ©2007 Pearson Education, Inc. -

Reception Performance Improvement of AM/FM Tuner by Digital Signal Processing Technology

Reception performance improvement of AM/FM tuner by digital signal processing technology Akira Hatakeyama Osamu Keishima Kiyotaka Nakagawa Yoshiaki Inoue Takehiro Sakai Hirokazu Matsunaga Abstract With developments in digital technology, CDs, MDs, DVDs, HDDs and digital media have become the mainstream of car AV products. In terms of broadcasting media, various types of digital broadcasting have begun in countries all over the world. Thus, there is a demand for smaller and thinner products, in order to enhance radio performance and to achieve consolidation with the above-mentioned digital media in limited space. Due to these circumstances, we are attaining such performance enhancement through digital signal processing for AM/FM IF and beyond, and both tuner miniaturization and lighter products have been realized. The digital signal processing tuner which we will introduce was developed with Freescale Semiconductor, Inc. for the 2005 line model. In this paper, we explain regarding the function outline, characteristics, and main tech- nology involved. 22 Reception performance improvement of AM/FM tuner by digital signal processing technology Introduction1. Introduction from IF signals, interference and noise prevention perfor- 1 mance have surpassed those of analog systems. In recent years, CDs, MDs, DVDs, and digital media have become the mainstream in the car AV market. 2.2 Goals of digitalization In terms of broadcast media, with terrestrial digital The following items were the goals in the develop- TV and audio broadcasting, and satellite broadcasting ment of this digital processing platform for radio: having begun in Japan, while overseas DAB (digital audio ①Improvements in performance (differentiation with broadcasting) is used mainly in Europe and SDARS (satel- other companies through software algorithms) lite digital audio radio service) and IBOC (in band on ・Reduction in noise (improvements in AM/FM noise channel) are used in the United States, digital broadcast- reduction performance, and FM multi-pass perfor- ing is expected to increase in the future. -

Next-Generation Photonic Transport Network Using Digital Signal Processing

Next-Generation Photonic Transport Network Using Digital Signal Processing Yasuhiko Aoki Hisao Nakashima Shoichiro Oda Paparao Palacharla Coherent optical-fiber transmission technology using digital signal processing is being actively researched and developed for use in transmitting high-speed signals of the 100-Gb/s class over long distances. It is expected that network capacity can be further expanded by operating a flexible photonic network having high spectral efficiency achieved by applying an optimal modulation format and signal processing algorithm depending on the transmission distance and required bit rate between transmit and receive nodes. A system that uses such adaptive modulation technology should be able to assign in real time a transmission path between a transmitter and receiver. Furthermore, in the research and development stage, optical transmission characteristics for each modulation format and signal processing algorithm to be used by the system should be evaluated under emulated quasi-field conditions. We first discuss how the use of transmitters and receivers supporting multiple modulation formats can affect network capacity. We then introduce an evaluation platform consisting of a coherent receiver based on a field programmable gate array (FPGA) and polarization mode dispersion/polarization dependent loss (PMD/PDL) emulators with a recirculating-loop experimental system. Finally, we report the results of using this platform to evaluate the transmission characteristics of 112-Gb/s dual-polarization, quadrature phase shift keying (DP-QPSK) signals by emulating the factors that degrade signal transmission in a real environment. 1. Introduction amplifiers—which is becoming a limiting factor In the field of optical communications in system capacity—can be efficiently used. -

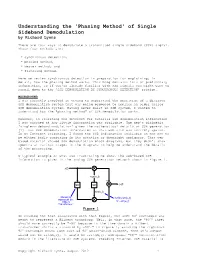

Of Single Sideband Demodulation by Richard Lyons

Understanding the 'Phasing Method' of Single Sideband Demodulation by Richard Lyons There are four ways to demodulate a transmitted single sideband (SSB) signal. Those four methods are: • synchronous detection, • phasing method, • Weaver method, and • filtering method. Here we review synchronous detection in preparation for explaining, in detail, how the phasing method works. This blog contains lots of preliminary information, so if you're already familiar with SSB signals you might want to scroll down to the 'SSB DEMODULATION BY SYNCHRONOUS DETECTION' section. BACKGROUND I was recently involved in trying to understand the operation of a discrete SSB demodulation system that was being proposed to replace an older analog SSB demodulation system. Having never built an SSB system, I wanted to understand how the "phasing method" of SSB demodulation works. However, in searching the Internet for tutorial SSB demodulation information I was shocked at how little information was available. The web's wikipedia 'single-sideband modulation' gives the mathematical details of SSB generation [1]. But SSB demodulation information at that web site was terribly sparse. In my Internet searching, I found the SSB information available on the net to be either badly confusing in its notation or downright ambiguous. That web- based material showed SSB demodulation block diagrams, but they didn't show spectra at various stages in the diagrams to help me understand the details of the processing. A typical example of what was frustrating me about the web-based SSB information is given in the analog SSB generation network shown in Figure 1. x(t) cos(ωct) + 90o 90o y(t) – sin(ωct) Meant to Is this sin(ω t) represent the c Hilbert or –sin(ωct) Transformer. -

Digital Signal Processing: Theory and Practice, Hardware and Software

AC 2009-959: DIGITAL SIGNAL PROCESSING: THEORY AND PRACTICE, HARDWARE AND SOFTWARE Wei PAN, Idaho State University Wei Pan is Assistant Professor and Director of VLSI Laboratory, Electrical Engineering Department, Idaho State University. She has several years of industrial experience including Siemens (project engineering/management.) Dr. Pan is an active member of ASEE and IEEE and serves on the membership committee of the IEEE Education Society. S. Hossein Mousavinezhad, Idaho State University S. Hossein Mousavinezhad is Professor and Chair, Electrical Engineering Department, Idaho State University. Dr. Mousavinezhad is active in ASEE and IEEE and is an ABET program evaluator. Hossein is the founding general chair of the IEEE International Conferences on Electro Information Technology. Kenyon Hart, Idaho State University Kenyon Hart is Specialist Engineer and Associate Lecturer, Electrical Engineering Department, Idaho State University, Pocatello, Idaho. Page 14.491.1 Page © American Society for Engineering Education, 2009 Digital Signal Processing, Theory/Practice, HW/SW Abstract Digital Signal Processing (DSP) is a course offered by many Electrical and Computer Engineering (ECE) programs. In our school we offer a senior-level, first-year graduate course with both lecture and laboratory sections. Our experience has shown that some students consider the subject matter to be too theoretical, relying heavily on mathematical concepts and abstraction. There are several visible applications of DSP including: cellular communication systems, digital image processing and biomedical signal processing. Authors have incorporated many examples utilizing software packages including MATLAB/MATHCAD in the course and also used classroom demonstrations to help students visualize some difficult (but important) concepts such as digital filters and their design, various signal transformations, convolution, difference equations modeling, signals/systems classifications and power spectral estimation as well as optimal filters. -

An Analysis of a Quadrature Double-Sideband/Frequency Modulated Communication System

Scholars' Mine Masters Theses Student Theses and Dissertations 1970 An analysis of a quadrature double-sideband/frequency modulated communication system Denny Ray Townson Follow this and additional works at: https://scholarsmine.mst.edu/masters_theses Part of the Electrical and Computer Engineering Commons Department: Recommended Citation Townson, Denny Ray, "An analysis of a quadrature double-sideband/frequency modulated communication system" (1970). Masters Theses. 7225. https://scholarsmine.mst.edu/masters_theses/7225 This thesis is brought to you by Scholars' Mine, a service of the Missouri S&T Library and Learning Resources. This work is protected by U. S. Copyright Law. Unauthorized use including reproduction for redistribution requires the permission of the copyright holder. For more information, please contact [email protected]. AN ANALYSIS OF A QUADRATURE DOUBLE- SIDEBAND/FREQUENCY MODULATED COMMUNICATION SYSTEM BY DENNY RAY TOWNSON, 1947- A THESIS Presented to the Faculty of the Graduate School of the UNIVERSITY OF MISSOURI - ROLLA In Partial Fulfillment of the Requirements for the Degree MASTER OF SCIENCE IN ELECTRICAL ENGINEERING 1970 ii ABSTRACT A QDSB/FM communication system is analyzed with emphasis placed on the QDSB demodulation process and the AGC action in the FM transmitter. The effect of noise in both the pilot and message signals is investigated. The detection gain and mean square error is calculated for the QDSB baseband demodulation process. The mean square error is also evaluated for the QDSB/FM system. The AGC circuit is simulated on a digital computer. Errors introduced into the AGC system are analyzed with emphasis placed on nonlinear gain functions for the voltage con trolled amplifier. -

E2L005 ROTCH a Day in the Life of the RF Spectrum

A Day in the Life of the RF Spectrum by James E. Cooley B.S., Computer Engineering Northwestern University (1999) Submitted to the Program of Media Arts and Sciences, School of Architecture and Planning, In partial fulfillment of the requirement for the degree of MASTER OF SCIENCE IN MEDIA ARTS AND SCIENCES at the MASSACHUSETTS INSTITUTE OF TECHNOLOGY September 2005 © Massachusetts Institute of Technology, 2005. All rights reserved. Signature of Author: Program in Media Arts and Sciences August 5, 2005 Certified by: Andrew B. Lippman Senior Research Scientist of Media Arts and Sciences Program in Media Arts and Sciences Thesis Supervisor Accepted by: Andrew B. Lippman Chairman, Departmental Committee on Graduate Studies Program in Media Arts and Sciences tMASSACHUSETT NSE IT 'F TECHNOLOG Y E2L005 ROTCH A Day in the Life of the RF Spectrum by James E. Cooley Submitted to the Program of Media Arts and Sciences, School of Architecture and Planning, September 2005 in partial fulfillment of the requirement for the degree of Master of Science in Media Arts and Sciences Abstract There is a misguided perception that RF spectrum space is fully allocated and fully used though even a superficial study of actual spectrum usage by measuring local RF energy shows it largely empty of radiation. Traditional regulation uses a fence-off policy, in which competing uses are isolated by frequency and/or geography. We seek to modernize this strategy. Given advances in radio technology that can lead to fully cooperative broadcast, relay, and reception designs, we begin by studying the existing radio environment in a qualitative manner. -

![Arxiv:1306.0942V2 [Cond-Mat.Mtrl-Sci] 7 Jun 2013](https://docslib.b-cdn.net/cover/1341/arxiv-1306-0942v2-cond-mat-mtrl-sci-7-jun-2013-1331341.webp)

Arxiv:1306.0942V2 [Cond-Mat.Mtrl-Sci] 7 Jun 2013

Bipolar electrical switching in metal-metal contacts Gaurav Gandhi1, a) and Varun Aggarwal1, b) mLabs, New Delhi, India Electrical switching has been observed in carefully designed metal-insulator-metal devices built at small geometries. These devices are also commonly known as mem- ristors and consist of specific materials such as transition metal oxides, chalcogenides, perovskites, oxides with valence defects, or a combination of an inert and an electro- chemically active electrode. No simple physical device has been reported to exhibit electrical switching. We have discovered that a simple point-contact or a granu- lar arrangement formed of metal pieces exhibits bipolar switching. These devices, referred to as coherers, were considered as one-way electrical fuses. We have identi- fied the state variable governing the resistance state and can program the device to switch between multiple stable resistance states. Our observations render previously postulated thermal mechanisms for their resistance-change as inadequate. These de- vices constitute the missing canonical physical implementations for memristor, often referred as the fourth passive element. Apart from the theoretical advance in un- derstanding metallic contacts, the current discovery provides a simple memristor to physicists and engineers for widespread experimentation, hitherto impossible. arXiv:1306.0942v2 [cond-mat.mtrl-sci] 7 Jun 2013 a)Electronic mail: [email protected] b)Electronic mail: [email protected] 1 I. INTRODUCTION Leon Chua defines a memristor as any two-terminal electronic device that is devoid of an internal power-source and is capable of switching between two resistance states upon application of an appropriate voltage or current signal that can be sensed by applying a relatively much smaller sensing signal1. -

Multiplexing and Sampling Theory

Multiplexing and Sampling Theory THE ECONOMY OF MULTIPLEXING contact type determine its current carrying capacity. For instance, laboratory instrument relays typically switch Sampled-Data Systems up to 3A, while industrial applications use larger relays An ideal data acquisition system uses a single ADC for to switch higher currents, often 5 to 10A. each measurement channel. In this way, all data are captured in parallel and events in each channel can be Solid-state switches, on the other hand, are much faster compared in real time. But using a multiplexer, Figure than relays and can reach sampling rates of several MHz. 3.01, that switches among the inputs of multiple chan- However, these devices can’t handle inputs higher than nels and drives a single ADC can substantially reduce 25V, and they are not well suited for isolated applica- the cost of a system. This approach is used in so-called tions. Moreover, solid-state devices are typically limited sampled-data systems. The higher the sample rate, the to handling currents of only one mA or less. closer the system mimics the ideal data acquisition system. But only a few specialized data acquisition Another characteristic that varies between mechani- systems require sample rates of extraordinary speed. cal relays and solid-state switches is called ON resis- Most applications can cope with the more modest tance. An ideal mechanical switch or relay contact sample rates typically offered by mainstream data pair has zero ON resistance. But real devices such acquisition systems. as common reed-relay contacts are 0.010 W or less, a quality analog switch can be 10 to 100 W, and an Solid State Switches vs.