Motherboard Glossary

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

2004 Gamers' Hardware Upgrade Guide

Ace’s Hardware 2004 Gamers’ Hardware Upgrade Guide 2004 Gamers’ Hardware Upgrade Guide By Johan De Gelas – January 2004 Introduction Last week, we showed you a preview of the Athlon 64 3400+. Today, we'll investigate this new CPU as an upgrade to an existing system. How much performance do you gain when upgrading? What about the other features aside from performance, such as Cool'n'Quiet and more thermal and mechanical safety? As always, we start with a base system to be upgraded. This time around, our base system is equipped with an Athlon XP 2100+, as previous polls among our readers show that the faster versions of the Athlon XP "Palomino" were very popular in the early days of 2003. Now in 2004, Palomino is getting a little long in the tooth, so it's interesting to know whether or not an upgrade may be worthwhile. Our old system also contains a GeForce Ti 4200 and 512 MB of DDR266 (PC2100) memory. We will upgrade the CPU (to the Athlon 4 3400+) and memory (to DDR400 CAS 2) and compare that upgrade with one that simply upgrades the video card. As mentioned previously, we've done this before in many of our Gamer's Upgrade Guides. However, the gaming industry is not sitting still, and we are moving from hybrid DirectX 7/8 games to DirectX 8/9 games, which - as you will see - behave quite differently. The games you'll see tested in detail today are Halo 1.03, Return to Castle Wolfenstein: Enemy Territory, and X²- The Threat. -

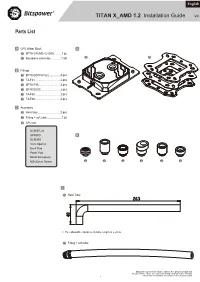

Titan X Amd 1.2 V4 Ig 20210319

English TITAN X_AMD 1.2 Installation Guide V4 Parts List A CPU Water Block A A-1 BPTA-CPUMS-V2-SKA ..........1 pc A-1 A-2 A-2 Backplane assembly ..............1 set B Fittings B-1 BPTA-DOTFH1622 ...............4 pcs B-2 TA-F61 ...................................2 pcs B-3 BPTA-F95 ..............................2 pcs B-4 BP-RIGOS5 ...........................2 pcs B-5 TA-F60 ..................................2 pcs B-6 TA-F40 ..................................2 pcs C Accessory C-1 Hard tube ..............................2 pcs C-2 Fitting + soft tube ....................1 pc C-3 CPU set SCM3FL20 SPRING B SCM3F6 1mm Spacer Back Pad Paste Pad Metal Backplane M3x32mm Screw B-1 B-2 B-3 B-4 B-5 B-6 C C-1 Hard Tube ※ The allowable variance in tube length is ± 2mm C-2 Fitting + soft tube Bitspower reserves the right to change the product design and interpretations. These are subject to change without notice. Product colors and accessories are based on the actual product. — 1 — I. AMD Motherboard system 54 AMD SOCKET 939 / 754 / 940 IN 48 AMD SOCKET AM4 AMD SOCKET AM3 / AM3+ AMD SOCKET AM2 / AM2+ AMD SOCKET FM1 / FM2+ Bitspower Fan and DRGB RF Remote Controller Hub (Not included) are now available at microcenter.com DRGB PIN on Motherboard or other equipment. 96 90 BPTA-RFCHUB The CPU water block has a DRGB cable, which AMD SOCKET AM4 AMD SOCKET AM3 AM3+ / AMD SOCKET AM2 AM2+ / AMD SOCKET FM1 / FM2+ can be connected to the DRGB extension cable of the radiator fans. Fan and DRGB RF Remote Motherboard Controller Hub (Not included) OUT DRGB LED Do not over-tighten the thumb screws Installation (SCM3FL20). -

Direct Memory Access Components Verification System

ТРУДЫ МФТИ. — 2012. — Том 4, № 1 Frolov P. V. et al. 1 УДК 004.052.42 P. V. Frolov, V. N. Kutsevol, A. N. Meshkov, N. Yu. Polyakov, M. P. Ryzhov AO «MCST» PAO «INEUM» Direct Memory Access components verification system A method of direct memory access subsystem verification used for Elbrus series micro- processors has been described. A peripheral controller imitator has been developed in order to reduce verification overhead. The model of imitator has been included into the functional machine simulator. A pseudorandom test generator for verification of the direct memory access subsystem has been based on the simulator. Ключевые слова: system verification, functional model, direct memory access, pseu- dorandom test generation. Direct Memory Access components verification system 1. Introduction Modern computer systems require very intensive data exchange between the peripheral de- vices and the random-access memory. In the most cases this exchange is performed by the direct memory access (DMA) subsystem. The increasing demands for the performance of the subsys- tem lead to an increase in its complexity, therefore requiring development of effective approaches to DMA subsystem verification [1,2]. This article is based on a result of a comprehensive project than combined implementation of a there co-designed verification techniques based on the consecutive investigation of theDMA subsystem employing one the three models: 1) a functional model written in C++ that corre- sponds to behaviour of the subsystem in the environment determined by a real computer system configuration, 2) RTL model in Verilog and 3) FPGA-based prototype. This article describesthe first method that enables verifying correctness of the design at an early stage of the verification and eliminate a large quantity of bugs using simple tests. -

VIA RAID Configurations

VIA RAID configurations The motherboard includes a high performance IDE RAID controller integrated in the VIA VT8237R southbridge chipset. It supports RAID 0, RAID 1 and JBOD with two independent Serial ATA channels. RAID 0 (called Data striping) optimizes two identical hard disk drives to read and write data in parallel, interleaved stacks. Two hard disks perform the same work as a single drive but at a sustained data transfer rate, double that of a single disk alone, thus improving data access and storage. Use of two new identical hard disk drives is required for this setup. RAID 1 (called Data mirroring) copies and maintains an identical image of data from one drive to a second drive. If one drive fails, the disk array management software directs all applications to the surviving drive as it contains a complete copy of the data in the other drive. This RAID configuration provides data protection and increases fault tolerance to the entire system. Use two new drives or use an existing drive and a new drive for this setup. The new drive must be of the same size or larger than the existing drive. JBOD (Spanning) stands for Just a Bunch of Disks and refers to hard disk drives that are not yet configured as a RAID set. This configuration stores the same data redundantly on multiple disks that appear as a single disk on the operating system. Spanning does not deliver any advantage over using separate disks independently and does not provide fault tolerance or other RAID performance benefits. If you use either Windows® XP or Windows® 2000 operating system (OS), copy first the RAID driver from the support CD to a floppy disk before creating RAID configurations. -

ATX-945G Industrial Motherboard in ATX Form Factor with Intel® 945G Chipset

ATX-945G Industrial Motherboard in ATX form factor with Intel® 945G chipset Supports Intel® Core™2 Duo, Pentium® D CPU on LGA775 socket 1066/800/533MHz Front Side Bus Intel® Graphics Media Accelerator 950 Dual Channel DDR2 DIMM, maximum 4GB Integrated PCI Express LAN, USB 2.0 and SATA 3Gb/s ATX-945G Product Overview The ATX-945G is an ATX form factor single-processor (x8) and SATA round out the package for a powerful industrial motherboard that is based on the Intel® 945G industrial PC. I/O features of the ATX-945G include a chipset with ICH7 I/O Controller Hub. It supports the Intel® 32-bit/33MHz PCI Bus, 16-bit/8MHz ISA bus, 1x PCI Express Core™2 Duo, Pentium® D, Pentium® 4 with Hyper-Threading x16 slot, 2x PCI Express x1 slots, 3x PCI slots, 1x ISA slot Technology, or Celeron® D Processor on the LGA775 socket, (shared w/ PCI), onboard Gigabit Ethernet, LPC, EIDE Ultra 1066/800/533MHz Front Side Bus, Dual Channel DDR2 DIMM ATA/100, 4 channels SATA 3Gb/s, Mini PCI card slot, UART 667/533/400MHz, up to 4 DIMMs and a maximum of 4GB. The compatible serial ports, parallel port, floppy drive port, HD Intel® Graphic Media Accelerator 950 technology with Audio, and PS/2 Keyboard and Mouse ports. 2048x1536x8bit at 75Hz resolution, PCI Express LAN, USB 2.0 Block Diagram CPU Core™2 Duo Pentium® D LGA775 package 533/800/1066MHz FSB Dual-Core Hyper-Threading 533/800/1066 MHz FSB D I M Northbridge DDR Channel A M ® x Intel 945G GMCH 2 DDRII 400/533/667 MHz D I CRT M M DB-15 DDR Channel B x 2 Discrete PCIe x16 Graphics DMI Interface 2 GB/s IDE Device -

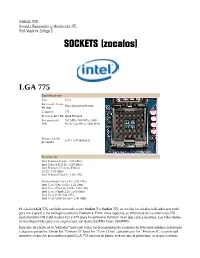

SOCKETS (Zocalos)

Instituto ITES Armado, Reparación y Mantención PC. Prof: Vladimir Zúñiga C. SOCKETS (zocalos) LGA 775 Especificaciones Tipo LGA Factores de forma Flip-chip land grid array del chip Contactos 775 Protocolo del FSB Quad-Pumped Frecuencia del 533 MT/s, 800 MT/s, 1066 FSB MT/s, 1333 MT/s, 1600 MT/s Dimesiones del 1.47 × 1.47 inches[1] procesador Procesadores Intel Pentium 4 (2.66 - 3.80 GHz) Intel Celeron D (2.53 - 3.60 GHz ) Intel Pentium 4 Extreme Edition (3.20 - 3.73 GHz) Intel Pentium D (2.66 - 3.60 GHz) Pentium Dual-Core (1.40 - 2.80 GHz) Intel Core 2 Duo (1.60 - 3.33 GHz) Intel Core 2 Extreme (2.66 - 3.20 GHz) Intel Core 2 Quad (2.33 - 3.00 GHz) Intel Xeon (1.86-3.40 GHz) Intel 'Core' Celeron (1.60 - 2.40 GHz) El zócalo LGA 775, también conocido como Socket T o Socket 775, es uno de los zócalos utilizados por Intel para dar soporte a los microprocesadores Pentium 4. Entre otros aspectos, se diferencia de los anteriores 370 (para Pentium III) y del Socket 423 y 478 (para los primeros Pentium 4) en que carece de pines. Las velocidades de bus disponibles para esta arquitectura van desde 533Mhz hasta 1600MHz. Este tipo de zócalo es el "estándar" para casi todos los procesadores de consumo de Intel para equipos sobremesa y algunos portátiles. Desde los "Celeron D" hasta los "Core 2 Duo", pasando por los "Pentium D", su principal atractivo es que los procesadores para LGA 775 carecen de pines; es decir que la placa base es la que contiene los contactos para comunicarse con el procesador. -

Get More out of the Intel Foxhollow Platform

Get More Out Of the Intel Foxhollow Platform Akber Kazmi, Marketing Director, PLX Technology Introduction As being reported by the mainstream technology media, Intel is leveraging the technology from its latest server-class Nehalem CPU to offer the Lynnfield CPU, targeted for high-end desktop and entry-level servers. This platform is codenamed “Foxhollow “. Intel is expected to launch this new platform sometime in the second half of 2009. This entry-level uni-processor (UP) server platform will feature two to four cores as Intel wants to pack a lot of processing power in all its platforms. The Foxhollow platform is quite different from the previous Desktops and UP servers in that it reduces the solution from three chips to two chips by eliminating the northbridge and replacing the southbridge with a new device called the Platform Controller Hub (or PCH) code named Ibexpeak (5 Series Chipset). As Intel has moved the memory controller and the graphics function into the CPU, there's no need for an MCH (Memory Controller Hub), so Intel has simplified its chipset design to keep costs down in the entry-level and mainstream segments. The PCH chip interfaces with the CPU through Intel’s DMI interconnect. The PCH will support eight PCIe lanes, up to four PCI slots, the GE MAC, display interface controllers, I/O controllers, RAID controllers, SATA controllers, USB 2.0 controllers, etc. Foxhollow Motherboards Foxhollow motherboards are being offered in two configurations, providing either two or three x8 PCIe ports for high performance I/Os. However, motherboard vendors can use an alternate configuration that provides one more PCIe x8 port with no significant burden and instead offers 33% more value than the three port solution and 50% more value than the two port solution. -

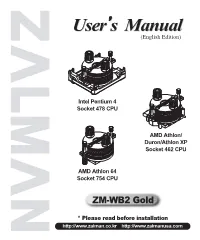

User's Manual User's Manual

User’s Manual (English Edition) Intel Pentium 4 Socket 478 CPU AMD Athlon/ Duron/Athlon XP Socket 462 CPU AMD Athlon 64 Socket 754 CPU ZM-WB2 Gold * Please read before installation http://www.zalman.co.kr http://www.zalmanusa.com 1. Features 1) Gold plated pure copper base maximizes cooling performance and prevents CPU blocks from galvanic corrosion 2) Intel Pentium 4 (Socket 478), AMD Athlon/Duron/Athlon XP (Socket 462),Athlon 64 (Socket 754) compatible design for broad compatibility. 3) Three types of compression fitting are offered for use with water tubes (8X10mm,8X11mm,10X13mm) * Zalman Tech. Co., Ltd. is not responsible for any damage resulting from CPU OVERCLOCKING. 2. Specifications Part No Part name Q’ ty Weight (g) Use 1 CPU block 1 447.0 CPU mountimg 2 Hand screw 2 8.0 Clip mountimg 3 Thermal grease 1 1.8 Apply to cpu core 4 Clip 1 9.6 CPU block mountimg 5 User’s manual 1 6 Clip supports 2 8.2 Socket 478 7 Clip supports A 2 5.0 Socket 462 8 Clip supports B 2 5.0 Socket 462 9 Bolts 4 0.8 Clip supports, A, B-type 10 Paper washer 1 set 7, 8 mountimg 11 Nipple 2 6.2 Socket 754 mountimg 12 Back plate 60.0 Socket 754 mountimg Fitting to 13 Fitting 3 set 8 x 10mm, 8 x 11mm, 10 x 13mm tubes NOTE 1) The maximum weight for the cooler is specified as 450g/450g/300g for socket 478/754/462 respectively. Special care should be taken when moving a computer equipped with a cooler which exceeds the relevant weight limit. -

Thermal and Electrical Specification of AMD Semprontm Processors

Thermal and Electrical Specification of AMD SempronTM Processors Thermal and Electrical Specification of AMD SempronTM Processors 27 September 2004 Page 1/5 Thermal and Electrical Specification of AMD SempronTM Processors ©2004 Advanced Micro Devices Inc. All rights reserved. The contents of this document are provided in connection with Advanced Micro Devices, Inc. (“AMD”) products and are for information purposes only. AMD makes no representations or warranties with respect to the accuracy or completeness of the contents of this publication and reserves the right to make changes to specifications and product descriptions at any time without notice. No license, whether express, implied, arising by estoppels or otherwise, to any intellectual property rights are granted by this publication. Except as set forth in AMD’s Standard Terms and Conditions of Sale, AMD assumes no liability whatsoever, and disclaims any express or implied warranty, relating to its products including, but not limited to, the implied warranty of merchantability, fitness for a particular purpose, or infringement of any intellectual property right. AMD MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE CONTENTS HEREOF AND ASSUMES NO RESPONSIBILITY FOR ANY INACCURACIES, ERRORS OR OMISSIONS THAT MAY APPEAR IN THIS INFORMATION. AMD SPECIFICALLY DISCLAIMS ANY IMPLIED WARRANTIES OF MERCHANTABILITY OR FITNESS FOR ANY PARTICULAR PURPOSE. IN NO EVENT WILL AMD BE LIABLE TO ANY PERSON FOR ANY DIRECT, INDIRECT, SPECIAL OR OTHER CONSEQUENTIAL DAMAGES ARISING FROM THE USE OF ANY INFORMATION CONTAINED HEREIN OR FOR THE PERFORMANCE OR OPERATION OF ANY PERSON’S SYSTEM, INCLUDING, WITHOUT LIMITATION, ANY LOST PROFITS, BUSINESS INTERRUPTION, DAMAGE TO OR DESTRUCTION OF PROPERTY, OR LOSS OF PROGRAMS OR OTHER DATA, EVEN IF AMD IS EXPRESSLY ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. -

Double-Data Rate DDR Memory Review

International Journal of Advanced Engineering and Nano Technology (IJAENT) ISSN: 2347-6389, Volume-2 Issue-2, January 2015 Double-Data Rate DDR Memory Review Ahmed Shamil Mustafa, Mohammed Jabbar Mohammed, Muthana Najim Abdulleh technique became DDR. The technology, synchronous Abstract —Computer is one most important twenty-first century dynamic random access memory (SDRAM) was discovered technology, the large volume of data and store it makes of old in the beginning 1990s to make the computer more powerful, memories are not enough. In this paper we offer a historical in that time was used Traditional DRAM an asynchronous overview of Double Data Rate (DDR) memory being play a key interface it means work independently of the processor. With role in the development of computer with also who passed him in the end of the nineties of the last century and the beginning of addition to the basics of their work and develop in the future. 2000s, specifically in 2000 became a priority for developers Index Terms —Double-Data Rate DDR, Synchronous Dynamic and manufacturers is to produce or something development Random Access Memory (SDRAM) new to increase the performance of the computer, DDR double data rate ( also called DDR 1) is a new interface I. INTRODUCTION method was developed, this made data transfer on both the In the twenty-first century with technology developments, rising and falling edges of the clock signal it has the ability to the entry of the computer at all areas of scientific and social transfer data twice faster than earlier versions, such as life. With the increased demand for computer and the large SDRAM, the had used lower clock rate (100-200MHz), less volume of data has become the task of manufacturing power (2.5v) and high speed(1600-3200 MB/s). -

AMD Multi-Core Processors Providing Multiple Benefits for the Future

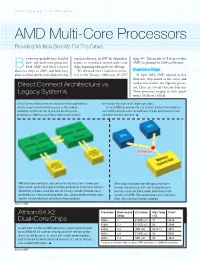

hard hat area | white paper AMD Multi-Core Processors Providing Multiple Benefits For The Future y now you probably have heard of variations this year. In 2007 the chipmakers (page 50). This month, we’ll focus on what dual- and multi-core processors. expect to introduce several multi-core AMD has planned for 2006 and beyond. B Both AMD and Intel released chips, beginning with quad-core offerings. dual-core chips in 2005, and both have We discussed Intel’s multi-core proces- Dual-Core Chips plans to release dozens more dual-core chip sors in the January 2006 issue of CPU In April 2005, AMD released its first dual-core chip aimed at the server and workstation market, the Opteron proces- Direct Connect Architecture vs. sor. There are several Opteron dual-core Legacy Systems 90nm processors ranging in clock speeds from 1.6GHz to 2.4GHz. Direct Connect Architecture lives up to its name by providing a for the past few years in its single-core chips. direct connection between the processor, the memory But now AMD has extended the use of Direct Connect Architecture to controller, and the I/O area to improve overall system connect the cores on a dual- or multi-core chip die and to connect each performance. AMD has used Direct Connect Architecture core to its memory controller. ▲ With multi-core architecture, each core on the chip has its own memory con- When using a dual-processor x86 legacy architecture, troller, which significantly improves memory performance. Using Direct Connect however, two processors then have to share the same Architecture to make a connection with the memory controller eliminates most memory control hub, which creates bottlenecks in data bottlenecks and makes multitasking easier. -

Technical Note Is to Provide an Figure 9: DQS WRITE Postamble and Preamble

TN-46-05 GENERAL DDR SDRAM FUNCTIONALITY TECHNICAL GENERAL DDR SDRAM NOTE FUNCTIONALITY INTRODUCTION The migration from single data rate synchronous Table of Contents DRAM (SDR) to double data rate synchronous DRAM DDR vs. SDR Functionality ............................... 2 (DDR) memory is upon us. Although there are many Table 1: SDR to DDR Quick Reference ................. 1 similarities, DDR technology also provides notable Figure 1: Functional Block Diagram .................... 2 product enhancements. Figure 4: Example of DDR Command Bus .......... 3 In general, double data rate memory provides 2n-Prefetch Architecture ................................. 3 source-synchronous data capture at a rate of twice the Figure 2: Block Diagram 2n-Prefetch READ ........ 3 clock frequency. Therefore, a DDR266 device with a Figure 3: Block Diagram 2n-Prefetch WRITE ....... 3 clock frequency of 133 MHz has a peak data transfer rate of 266 Mb/s or 2.1 GB/s for a x64 DIMM. This is Minimum Time Slots ........................................ 3 accomplished by utilizing a 2n-prefetch architecture Figure 5: 2n-Prefetch READ Slot Timing ............. 4 where the internal data bus is twice the width of the Figure 6: 2n-Prefetch WRITE Slot Timing ............ 5 external data bus and data capture occurs twice per Figure 7: READ Command Slots ........................... 6 clock cycle. To provide high-speed signal integrity, the Strobe-Based Data Bus ..................................... 4 DDR SDRAM utilizes a bidirectional data strobe, Preamble and Postamble ................................. 7 SSTL_2 interface with differential inputs and clocks. Figure 8: DQS READ Postamble and Preamble ... 7 The objective of this technical note is to provide an Figure 9: DQS WRITE Postamble and Preamble . 8 overview of the 2n-prefetch architecture, a strobe-based SSTL_2 Interface ..............................................