Moving to Altium Designer from Eagle

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Using the ELECTRIC VLSI Design System Version 9.07

Using the ELECTRIC VLSI Design System Version 9.07 Steven M. Rubin Author's affiliation: Static Free Software ISBN 0−9727514−3−2 Published by R.L. Ranch Press, 2016. Copyright (c) 2016 Static Free Software Permission is granted to make and distribute verbatim copies of this book provided the copyright notice and this permission notice are preserved on all copies. Permission is granted to copy and distribute modified versions of this book under the conditions for verbatim copying, provided also that they are labeled prominently as modified versions, that the authors' names and title from this version are unchanged (though subtitles and additional authors' names may be added), and that the entire resulting derived work is distributed under the terms of a permission notice identical to this one. Permission is granted to copy and distribute translations of this book into another language, under the above conditions for modified versions. Electric is distributed by Static Free Software (staticfreesoft.com), a division of RuLabinsky Enterprises, Incorporated. Table of Contents Chapter 1: Introduction.....................................................................................................................................1 1−1: Welcome.........................................................................................................................................1 1−2: About Electric.................................................................................................................................2 1−3: Running -

Eagle Tutorial

EAGLE EASILY APPLICABLE GRAPHICAL LAYOUT EDITOR Tutorial Version 5 Schematic – Layout – Autorouter for Linux® Mac® Windows® CadSoft Computer www.cadsoftusa.com 6th Edition 005175100 Copyright © 2010 CadSoft Computer All Rights Reserved CadSoft Computer is a trading division of Newark Corporation. If you have any questions please feel free to contact us: USA and other countries: Phone: +1 (954) 237 0932 Fax: +1 (954) 237 0968 Internet: www.cadsoftusa.com Email: [email protected] Germany and other European countries: Phone: +49 (0)8635 6989-10 Hotline: +49 (0)8635 6989-30 Fax: +49 (0)8635 6989-40 Internet: www.cadsoft.de Email: [email protected] And remember that we offer a free hotline for our customers! Copyright 2010 CadSoft Computer. All rights reserved worldwide. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, scanning, digitizing, or otherwise, without the prior consense of CadSoft Computer. Printing this tutorial for your personal use is allowed. Windows is a registered trademark of Microsoft Corporation. Linux is a registered trademark of Linus Torvalds. Mac is a registered trademark of Apple Computer Inc. Table Of Contents 1 What to expect from this Tutorial...............................................................6 2 Features of EAGLE.......................................................................................7 System Requirements...............................................................................7 -

A Fedora Electronic Lab Presentation

Chitlesh GOORAH Design & Verification Club Bristol 2010 FUDConBrussels 2007 - [email protected] [ Free Electronic Lab ] (formerly Fedora Electronic Lab) An opensource Design and Simulation platform for Micro-Electronics A one-stop linux distribution for hardware design Marketing means for opensource EDA developers (Networking) From SPEC, Model, Frontend Design, Backend, Development boards to embedded software. FUDConBrussels 2007 - [email protected] Electronic Designers Problems Approx. 6 month design development cycle Tackling Design Complexity Lower Power, Lower Cost and Smaller Space Semiconductor Industry's neck squeezed in 2008 Management (digital/analog) IP Portfolio FUDConBrussels 2007 - [email protected] FUDConBrussels 2007 - [email protected] A basic Design Flow FUDConBrussels 2007 - [email protected] TIP: Use verilator to lint your verilog files. Most of the Veripool tools are available under FEL. They are in sync with Wilson Snyder's releases. FUDConBrussels 2007 - [email protected] FUDConBrussels 2007 - [email protected] GTKWaveGTKWave Don'tDon't forgetforget itsits TCLTCL backendbackend WidelyWidely usedused togethertogether withwith SystemCSystemC FUDConBrussels 2007 - [email protected] Tools Standard Cell libraries FUDConBrussels 2007 - [email protected] BackendBackend designdesign Open Circuit Design, Electric FUDConBrussels 2007 - [email protected], Toped gEDA/gafgEDA/gaf Well known and famous. A very good example of opensource -

Electronic Circuit Simulation and PCB Design

COURSE CODE COURSE TITLE L T P C ELECTRONICS CIRCUIT SIMULATION AND PCB 1152EC239 1 0 4 3 DESIGN a. Course Category: Program Elective b. Preamble: The course is aimed at making the students to understand electronic circuit simulation process for better understanding and designing of cost effective Printed Circuit Boards. Emphasizing the students to understand how to design a PCB layout of given circuit using available circuit simulation and PCB layout design CAD tools (free or licensed) .This course helps the student to simulate the circuit, develop the complete hardware circuit on PCB and assemble the components using SMD soldering technique c. Prerequisite Courses: Nil d. Related Courses: Analog Electronics, Linear Integrated Circuits e. Course Outcomes : Upon the successful completion of the course, students will be able to: Skill Level CO Course Outcomes (Based on Dave’s Nos. Taxonomy) Simulate and perform various analysis for the given Electronic CO1 S3 Circuit. CO2 Design a PCB Layout for the given circuit S4 CO3 Fabricate the PCB and assemble the components. S2 f. Correlation of COs with POs PO1 PO2 PO3 PO4 PO5 PO6 PO7 PO8 PO9 PO10 PO11 PO12 PSO1 PSO2 CO1 L M H - H - - - M - - M H H CO2 L M H - H - - - M - - M H H CO3 L M H - H - - - M - - M H H g. Examination scheme Examination Scheme for practical dominated course Internal evaluation Semester end evaluation (40M) (60M) Laboratory experiment Model laboratory test Part-A Part-B (15M) (25M) (20M) (40M) Performa Result Viv Reco Performa Result Viv Theory Performa Result Viv nce in and a rd nce in and a questions nce in and a- conductin analys Voc (4) conductin analys Voc to evaluate conductin analys Voc g is e g is e the g is e experime (3 ) ( 3) experime (5) ( 5) knowledge experime (10) (5) nt nt and nt ( 5 ) ( 15 ) understand (25) ing (20) h. -

Metadefender Core V4.12.2

MetaDefender Core v4.12.2 © 2018 OPSWAT, Inc. All rights reserved. OPSWAT®, MetadefenderTM and the OPSWAT logo are trademarks of OPSWAT, Inc. All other trademarks, trade names, service marks, service names, and images mentioned and/or used herein belong to their respective owners. Table of Contents About This Guide 13 Key Features of Metadefender Core 14 1. Quick Start with Metadefender Core 15 1.1. Installation 15 Operating system invariant initial steps 15 Basic setup 16 1.1.1. Configuration wizard 16 1.2. License Activation 21 1.3. Scan Files with Metadefender Core 21 2. Installing or Upgrading Metadefender Core 22 2.1. Recommended System Requirements 22 System Requirements For Server 22 Browser Requirements for the Metadefender Core Management Console 24 2.2. Installing Metadefender 25 Installation 25 Installation notes 25 2.2.1. Installing Metadefender Core using command line 26 2.2.2. Installing Metadefender Core using the Install Wizard 27 2.3. Upgrading MetaDefender Core 27 Upgrading from MetaDefender Core 3.x 27 Upgrading from MetaDefender Core 4.x 28 2.4. Metadefender Core Licensing 28 2.4.1. Activating Metadefender Licenses 28 2.4.2. Checking Your Metadefender Core License 35 2.5. Performance and Load Estimation 36 What to know before reading the results: Some factors that affect performance 36 How test results are calculated 37 Test Reports 37 Performance Report - Multi-Scanning On Linux 37 Performance Report - Multi-Scanning On Windows 41 2.6. Special installation options 46 Use RAMDISK for the tempdirectory 46 3. Configuring Metadefender Core 50 3.1. Management Console 50 3.2. -

Alexis Rodriguez Jr

Alexis Rodriguez Jr. 701 SW 62nd Blvd - Apt 104 - Gainesville - FL - 32604 Cell: 305-370-8334 Email: [email protected] Education: University of Florida Gainesville, FL Current M.S. Computer and Electrical Engineering University of Florida Gainesville, FL 2018 B.S. Electrical Engineering - Cum Laude Miami Dade College Miami, FL 2013 A.A. Engineering - Computer Projects: FPGA Networking Research Current Nallatech 385a Communication Research Current Glove Controlled Drone Design 2 Fall 2017 32-bit ARM Cortex (TI MSP432) used to interpret hand gestures via sensors for drone flight, transmit user intended controls to the drone via RF communication, and detect and display communication errors and react accordingly for safety 32-bit MIPS Emulated Processor Digital Design Spring 2017 Altera Cyclone-III FPGA used to emulate MIPS processor via VHDL Guitar Tuner Design 1 Spring 2017 Microchip PIC18F4620 microcontroller and discrete analog components used to determine correct input frequency via analog filtering and DSP techniques Employment: University of Florida - ARC Lab Gainesville, FL Current Research Assistant - FPGA ❖ Research systems integration of Nallatech 385a FPGA card and its components including the Intel Arria 10 FPGA, Intel’s Avalon bus, and PCIe communication via Linux ❖ Create partial reconfiguration region for Nallatech 385a for general use in research lab ❖ Research cloud and network implementations of FPGAs Intel San Jose, CA Summer 2019/2020 Programmable Solutions Group Intern ❖ Assisted with Agilex Linux driver development ❖ ITU G spec testing compliance and characterization for IEEE 1588 on Intel N3000 ❖ Developed automated tools for ITU network timestamp testing ❖ System validation of IEEE 1588 for Wireless 5G technology and communicated need and data across many teams ❖ Developed Arduino workshop for hobbyists Alexis Rodriguez Jr. -

Altium's Journey and Its Vision of Industry Transformation

A Winning Strategy for Value-Creation ALTIUM’S JOURNEY AND ITS VISION OF INDUSTRY TRANSFORMATION 18 June 2021 Agenda 1 Altium’s Journey of Transformation 2 Uniqueness of Altium in the Engineering Software Ecosystem 3 Altium’s Confidence in its Ability to Execute 4 Our Flight Path to Dominance Outstanding Value-Creation Track-Record Over Time ALU Set in 2019 and confident of achieving $500M * Stock Price Revenue Target Set in 2016 and fell short with COVID, $189M ** Delivering Value for our Shareholders $200M is a Hallmark of Altium… Revenue Target • A history of setting and over-achieving Set in 2014 and overachieved, $110M $100M aggressive long-term financial targets Revenue Target • Eight consecutive years of double-digit revenue growth & expanding margin ? • Focused execution with the “ingenuity of and” A$41.60 delivering strong operating leverage A$10.15 • Transparency for stakeholders and all-in reporting (no capitalization of R&D expenses) A$4.36 • Value creation at every stage from leadership to dominance to industry transformation A$0.76 Performing Leading Dominating Transforming 2012 2015 2017 2020 2025 * The target revenue of $500M may include 10-20% from future acquisitions. 3 ** Three months out analysts’ consensus pointed to a revenue target of $208M for FY2020 Pursuing Dominance and Transformation from a Position of Strength Financial Altium Designer Altium 365 Performance Dominance Adoption Altium is the fastest growing EDA company Altium Designer is the most widespread The world’s first digital platform for with 8 consecutive -

Getting Started with PCB Design

Getting Started with PCB Design This introductory tutorial is designed to give you an overview Summary of how to create a schematic, update the design information to a PCB and generate manufacturing output files. It also Tutorial investigates the concept of projects and integrated libraries TU0117 (v2.0) February 12, 2008 and provides a summary of the 3D PCB environment and creating 3D bodies for component footprints. Welcome to the world of Altium Designer – a complete electronic product development environment. This tutorial will get you started with creating a PCB project based on an astable multivibrator design. If you are new to Altium Designer then you might like read the guide Welcome to the Altium Designer Environment for an explanation of the interface, information on how to use panels and managing design documents. Creating a New PCB Project A project in Altium Designer consists of links to all documents and setups related to a design. A project file, eg. xxx.PrjPCB, is an ASCII text file that lists which documents are in the project and related output setups, eg. for printing and CAM. Documents that are not associated with a project are called ‘free documents’. Links to schematic sheets and a target output, eg. PCB, FPGA, embedded (VHDL) or library package, are added to a project. Once the project is compiled, design verification, synchronization and comparison can take place. Any changes to the original schematics or PCB, for example, are updated in the project when compiled. The process of creating a new project is the same for all project types. -

Bridging the Gap Between Precise RT-Level Power/Timing Estimation and Fast High-Level Simulation

Fakultät II – Informatik, Wirtschafts- und Rechtswissenschaften Department für Informatik Bridging the Gap between Precise RT-Level Power/Timing Estimation and Fast High-Level Simulation A method for automatically identifying and characterising combinational macros in synchronous sequential systems at register-transfer level and subsequent executable high-level model generation with respect to non-functional properties Dissertation zur Erlangung des Grades eines Doktors der Ingenieurwissenschaften von Dipl.-Inform. Kai Hylla Gutachter: Prof. Dr. Wolfgang Nebel Prof. Dr. Wolfgang Rosenstiel Tag der Disputation: 13. Januar 2014 Abstract Knowing a system’s power dissipation and timing behaviour is mandatory for today’s system development and key to an effective design space exploration. Not only does battery lifetime or design of the power supply directly depend on the power dissipation of the system. Second-order effects such as thermal behaviour or degradation effects that are directly or indirectly affected by the power dissipation must be considered, too. Various techniques for power estimation exist at different levels of abstraction. Low-level approaches provide accurate estimation results but require a lot of computational effort. High- level approaches however, allow fast and early estimates, but lack of a deeper knowledge and understanding of the hardware, implementing the behaviour. Therefore, they can only give rough estimates. What is missing is an approach allowing fast and early estimates with respect to as many relevant hardware artefacts and physical properties as possible. This doctoral thesis tackles the problem of a fast, yet accurate power and timing estimation of embedded hardware modules at a high-level of abstraction. A comparatively time consuming low-level estimation is performed once in order to obtain an accurate estimate. -

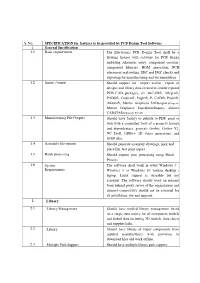

S. No. SPECIFICATION for Features to Be Provided by PCB Design Tool

S. No. SPECIFICATION for features to be provided by PCB Design Tool Software 1 General Specification 1.1 Basic requirements The Electronics PCB Design Tool shall be a floating license with software for PCB design including schematic entry, component creation, component libraries, BOM generation, PCB placement and routing, ERC and DRC checks and exporting for manufacturing and documentation. 1.2 Import / export Should support for import and/or export of designs and library data created in similar reputed PCB CAD packages, viz. OrCAD®, Allegro®, PADS®, Cadstar®, Eagle®, P- CAD®, Protel®, Altium®, Mentor Graphics® DxDesigner®(Import), Mentor Graphics® Expedition(Import), Zuken® CADSTAR®(Import), P-CAD 1.3 Manufacturing File Outputs Should have facility to publish to PDF, print or web with a controlled view of a project's history and dependencies, generate Gerber, Gerber X2, NC Drill, ODB++ 3D video animations, and STEP files. 1.4 Assembly file outputs Should generate assembly drawings, pick and place file, test point report. 1.5 Batch processing Should support post processing using Batch Process 1.6 System The software shall work in 64bit Windows 7 , Requirements Windows 8 or Windows 10 version desktop / laptop. Linux support is desirable but not essential. The software should work on intranet from behind proxy server of the organization and internet connectivity should not be essential for its installation, use and upgrade. 2 Library 2.1 Library Management Should have unified library management based on a single data source for all component models and linked data including 3D models, data sheets and supplier links. 2.2 Library Should have library of major components from reputed manufacturers with provision to download files and work offline. -

Module 11: PCB Design Flow, Transferring a Design and Navigation

Module 11: PCB Design Flow, Transferring a Design and Navigation Module 11: PCB Design Flow, Transferring a Design and Navigation 11.1 PCB design process....................................................................... 11-1 11.2 Transferring design information to the PCB.................................... 11-3 11.2.1 Design synchronization ................................................................................11-3 11.2.2 Resolving synchronization errors .................................................................11-4 11.2.3 Exercise – Transferring the design ..............................................................11-5 11.3 Using the PCB Panel ...................................................................... 11-7 11.3.1 PCB Panel....................................................................................................11-7 11.3.2 PCB Rules and Violations ..........................................................................11-14 11.3.3 Exercise – Browsing a PCB document ......................................................11-15 11.4 Project Navigation and Cross Probing ....................................... 11-16 11.4.1 Compiling the PCB project .........................................................................11-16 11.4.2 Navigating ..................................................................................................11-16 11.4.3 Cross probing from the schematic to the PCB...........................................11-17 11.4.4 Exercise — Navigation and Cross Probing................................................11-18 -

Tutorial and Design of Printed Circuit Board ”Big Blinky”

Paper ID #31292 An Electronics Lab Project—Tutorial and Design of Printed Circuit Board ”big blinky” Dr. Rod Blaine Foist, California Baptist University Rod Foist Professor (and IEEE student club advisor), Electrical and Computer Engineering, Gordon & Jill Bourns College of Engineering, California Baptist University, [email protected]. Dr. Foist received his B.S. and M.S. degrees in Electrical Engineering from the University of Washington in 1982 and 1989, respectively. He earned his Ph.D. degree in Electrical and Computer Engineering from the University of British Columbia in 2011, specializing in signal processing of spectroscopy data with secondary emphasis in system-on-chip implementation. His on-going research interests involve embedded processing using FPGAs and hardware acceleration of algorithms. In the fall of 2011, Dr. Foist joined the College of Engineering at California Baptist University. He is a U.S. Navy veteran who still strives to serve God and country. He has been happily married for 42 years and has four adult children and two grandchildren. Dr. John Butler, California Baptist University Dr. John Butler is currently an Assistant Professor in the department of Electrical and Computer En- gineering at California Baptist University. He received his B.S., M.S., and Ph.D. degrees in Electrical Engineering from the University of California, Riverside, in 2009, 2011, and 2014, respectively. In the fall of 2018 Dr. Butler joined the Gordon and Jill Bourns College of Engineering at California Baptist University as an Assistant Professor. Prior to this, he served as an Adjunct Professor since 2014. His re- search background includes nanoscale fabrication and characterization, particularly of magnetic thin films for data storage and logic devices.