SMPTE Standard 370M-2002

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

VC-1 Compressed Video Bitstream Format and Decoding Process

_________________________________________________________________ SMPTE 421M-2006 SMPTE STANDARD VC-1 Compressed Video Bitstream Format and Decoding Process _________________________________________________________________ Intellectual property notice Copyright 2003-2006 THE SOCIETY OF MOTION PICTURE AND TELEVISION ENGINEERS 3 Barker Ave. White Plains, NY 10601 +1 914 761 1100 Fax +1 914 761-3115 E-mail [email protected] Web http://www.smpte.org The user’s attention is called to the possibility that compliance with this document may require use of inventions covered by patent rights. By publication of this document, no position is taken with respect to the validity of these claims or of any patent rights in connection therewith. The patent holders have, however, filed statements of willingness to grant a license under these rights on fair, reasonable and nondiscriminatory terms and conditions to applicants desiring to obtain such a license. Contact information may be obtained from the SMPTE. No representation or warranty is made or implied that these are the only licenses that may be required to avoid infringement in the use of this document. © SMPTE 2003-2006 – All rights reserved Approved 24-February-2006 i Foreword SMPTE (the Society of Motion Picture and Television Engineers) is an internationally-recognized standards developing organization. Headquartered and incorporated in the United States of America, SMPTE has members in over 80 countries on six continents. SMPTE’s Engineering Documents, including Standards, Recommended Practices and Engineering Guidelines, are prepared by SMPTE’s Technology Committees. Participation in these Committees is open to all with a bona fide interest in their work. SMPTE cooperates closely with other standards-developing organizations, including ISO, IEC and ITU. -

Digital Video Quality Handbook (May 2013

Digital Video Quality Handbook May 2013 This page intentionally left blank. Executive Summary Under the direction of the Department of Homeland Security (DHS) Science and Technology Directorate (S&T), First Responders Group (FRG), Office for Interoperability and Compatibility (OIC), the Johns Hopkins University Applied Physics Laboratory (JHU/APL), worked with the Security Industry Association (including Steve Surfaro) and members of the Video Quality in Public Safety (VQiPS) Working Group to develop the May 2013 Video Quality Handbook. This document provides voluntary guidance for providing levels of video quality in public safety applications for network video surveillance. Several video surveillance use cases are presented to help illustrate how to relate video component and system performance to the intended application of video surveillance, while meeting the basic requirements of federal, state, tribal and local government authorities. Characteristics of video surveillance equipment are described in terms of how they may influence the design of video surveillance systems. In order for the video surveillance system to meet the needs of the user, the technology provider must consider the following factors that impact video quality: 1) Device categories; 2) Component and system performance level; 3) Verification of intended use; 4) Component and system performance specification; and 5) Best fit and link to use case(s). An appendix is also provided that presents content related to topics not covered in the original document (especially information related to video standards) and to update the material as needed to reflect innovation and changes in the video environment. The emphasis is on the implications of digital video data being exchanged across networks with large numbers of components or participants. -

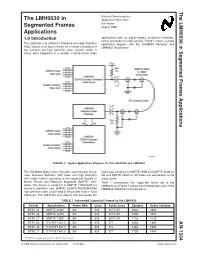

Application Note 1334 the LMH0030 in Segmented Frames Applications

The LMH0030 in Segmented Frames Applications AN-1334 National Semiconductor The LMH0030 in Application Note 1334 Kai Peters Segmented Frames August 2006 Applications 1.0 Introduction applications such as digital routers, production switchers, format converters or video servers. Figure 1 shows a typical The LMH0030 and LMH0031 Standard and High Definition application diagram with the LMH0030 Serializer and Video chipset is an ideal solution for a variety of products in LMH0031 Deserializer. the standard and high definition video systems realm. It allows easy integration in a number of professional video 20108501 FIGURE 1. Typical Application Diagram for the LMH0030 and LMH0031 The LMH0030 Digital Video Serializer automatically recog- video data compliant to SMPTE 259M and SMPTE 344M for nizes Standard Definition (SD) video and High Definition SD and SMPTE 292M for HD Video and serialization to the (HD) video formats according to the respective Society of output ports. Motion Picture and Television Engineers (SMPTE) stan- Table 1 summarizes the supported frame set of the dards. The device is compliant to SMPTE 125M/267M for LMH0030 and Figure 2 shows the simplified data path of the standard definition and SMPTE 260M/274M/295M/296M LMH0030 SD/HD Encoder/Serializer. high definition video as provided to the parallel 10bit or 20bit interfaces. The LMH0030 auto-detects and processes the TABLE 1. Automated Supported Frames by the LMH0030 Format Apecification Frame Rate Lines Active Lines Samples Active Samples SDTV, 54 SMPTE 344M 60I 525 507/1487 3432 2880 SDTV, 36 SMPTE 267M 60I 525 507/1487 2288 1920 SDTV, 27 SMPTE 125M 60I 525 507/1487 1716 1440 SDTV, 54 ITU-R BT 601.5 50I 625 577 3456 2880 SDTV, 36 ITU-R BT 601.5 50I 625 577 2304 1920 SDTV, 27 ITU-R BT 601.5 50I 625 577 1728 1440 PHYTER® is a registered trademark of National Semiconductor. -

Bit-Serial Digital Interface for High-Definition Television Systems

ANSI/SMPTE 292M-1996 SMPTE STANDARD for Television ---- Bit-Serial Digital Interface for High-Definition Television Systems Page 1 of 9 pages 1 Scope ANSI/SMPTE 274M-1995, Television ---- 1920 × 1080 Scanning and Interface This standard defines a bit-serial digital coaxial and fiber-optic interface for HDTV component signals ANSI/SMPTE 291M-1996, Television ---- Ancillary operating at data rates in the range of 1.3 Gb/s to 1.5 Data Packet and Space Formatting Gb/s. Bit-parallel data derived from a specified source format are multiplexed and serialized to form the serial SMPTE RP 184-1995, Measurement of Jitter in Bit- data stream. A common data format and channel Serial Digital Interfaces coding are used based on modifications, if necessary, to the source format parallel data for a given high- IEC 169-8 (1978), Part 8: R.F. Coaxial Connectors with definition television system. Coaxial cable interfaces Inner Diameter of Outer Conductor 6.5 mm (0.256 in) are suitable for application where the signal loss does with Bayonet Lock ---- Characteristic Impedance 50 not exceed an amount specified by the receiver manu- Ohms (Type BNC), and Appendix A (1993) facturer. Typical loss amounts would be in the range of up to 20 dB at one-half the clock frequency. Fiber IEC 793-2 (1992), Optical Fibres, Part 2: Product optic interfaces are suitable for application at up to 2 Specifications km of distance using single-mode fiber. IEC 874-7 (1990), Part 7: Fibre Optic Connector Several source formats are referenced and others Type FC operating within the covered data rate range may be serialized based on the techniques defined by this 3 Definition of terms standard. -

Presentation Title Sub-Title / Date

Review of HDTV (production) standards Hans Hoffmann Senior Engineer Technical Department, EBU [email protected] Overview HDTV basics Interfaces Compression HD-Ready, HDTV-Ready, EBU Demos @ IBC2005 1080p/50 Summary Uncompromised quality of Sound and Video Details (for advertisements) “Bad” HDTV more annoying than “bad” SDTV High-Definition Television Design Viewing Distance: max. 3h on a 50inch display Preferred Viewing Distance: Line or pixel structure Picture width pw [m] ] c/pw [m ph Line density Ld [m] not visible gh h ] e hi D [m ur c/p nal ago s] ct Di che Pi [in 1' (1/ . 60° ) View in g Dista [m] n ce d α Definitions • SDTV: – 625-line TV = active 576 lines, “576i/25” – 525-line TV = active 480 lines, “480i/29.94” • HDTV: – 1080i/25 – 1080p/25 or 1080p/24 – 720p/50 – 1080p/50 •Interlaced or progressive scan HDTV – Options in the Signal Chain Creation Production Encoder Distribution Decoder Interfacing Display What did we learn from theSat. SDTV debate on interfaces and compression?DTT. IP etc. • The wholeSig. Process.signal chain determines STBthe final qualityDisplay at theCompression consumer Decoder Studio-InterfacesHDTV is muchSignal Processimoreng sensitiveContribution to technicalNew STBand Display HD-SDI (1.485Gb) P/I still MPEG-2 (VC-1, H264) HD-Ready HD-SDI (3Gb) artistical1080i/25 errors. 422P@HL HDTV Ready 720p/50-60 10 Gb? 1080p/25 Emission format (720p/50 1080i/25-30 HD-SDTI • We 1080p/24need to be moreH.264-AcarefulVC and have1080i/25)to provide 720p/50 prop. SMPTE VC1 Impact of sufficient1080p/50 quality 720p/50headroom in the studio. -

Multi-Rate Serial Digital Interface Physical Layer User’

ispLever TM CORECORE Multi-Rate Serial Digital Interface Physical Layer IP Core User’s Guide January 2012 ipug70_01.2 Multi-Rate Serial Data Interface Physical Layer Lattice Semiconductor IP Core User’s Guide Introduction Serial Digital Interface (SDI) is the most popular raw video link standard used in television broadcast studios and video production facilities. Field Programmable Gate Arrays (FPGAs) with SDI interface capability can be used for acquisition, mixing, storage, editing, processing and format conversion applications. Simpler applications use FPGAs to acquire SDI data from one or more standard definition (SD) or high definition (HD) sources, perform sim- ple processing and retransmit the video data in SDI format. Such applications require an SDI physical layer (PHY) interface and some basic processing blocks such as a color space converter and frame buffer. In more complex applications, the acquired video receives additional processing, such as video format conversion, filtering, scaling, graphics mixing and picture-in-picture display. FPGA devices can also be used as a bridge between SDI video sources and backplane protocols such as PCI Express or Ethernet, with or without any additional video processing. In an FPGA-based SDI solution, the physical interface portion is often the most challenging part of the solution. This is because the PHY layer includes several device-dependent components such as high speed I/Os (inputs/outputs), serializer/deserializer (SERDES), clock/data recovery, word alignment and timing signal detection logic. Video processing, on the other hand, is algorithmic and is usually achieved using proprietary algorithms developed by in-house teams. The Lattice Multi-Rate SDI PHY Intellectual Property (IP) Core is a complete SDI PHY interface that connects to the high-speed SDI serial data on one side and the formatted parallel data on the other side. -

Understanding HD and 3G-SDI Video Poster

Understanding HD & 3G-SDI Video EYE DIGITAL SIGNAL TIMING EYE DIAGRAM The eye diagram is constructed by overlaying portions of the sampled data stream until enough data amplitude is important because of its relation to noise, and because the Y', R'-Y', B'-Y', COMMONLY USED FOR ANALOG COMPONENT ANALOG VIDEO transitions produce the familiar display. A unit interval (UI) is defined as the time between two adjacent signal receiver estimates the required high-frequency compensation (equalization) based on the Format 1125/60/2:1 750/60/1:1 525/59.94/2:1, 625/50/2:1, 1250/50/2:1 transitions, which is the reciprocal of clock frequency. UI is 3.7 ns for digital component 525 / 625 (SMPTE remaining half-clock-frequency energy as the signal arrives. Incorrect amplitude at the Y’ 0.2126 R' + 0.7152 G' + 0.0722 B' 0.299 R' + 0.587 G' + 0.114 B' 259M), 673.4 ps for digital high-definition (SMPTE 292) and 336.7ps for 3G-SDI serial digital (SMPTE 424M) sending end could result in an incorrect equalization applied at the receiving end, thus causing Digital video synchronization is provided by End of Active Video (EAV) and Start of Active Video (SAV) sequences which start with a R'-Y' 0.7874 R' - 0.7152 G' - 0.0722 B' 0.701 R' - 0.587 G' - 0.114 B' as shown in Table 1. A serial receiver determines if the signal is “high” or “low” in the center of each eye, and signal distortions. Overshoot of the rising and falling edge should not exceed 10% of the waveform HORIZONTAL LINE TIMING unique three word pattern: 3FFh (all bits in the word set to 1), 000h (all 0’s), 000h (all 0’s), followed by a fourth “XYZ” word whose B'-Y' -0.2126 R' - 0.7152 G' + 0.9278 B' -0.299 R' - 0.587 G' + 0.886 B' detects the serial data. -

Multi-Rate Serial Digital Interface (SDI) Physical Layer IP Core Is an Ipexpress User-Configurable Core and Can Be Used to Generate Any Allowable Configuration

ispLever TM CORECORE Multi-Rate Serial Digital Interface Physical Layer IP Core User’s Guide January 2012 ipug70_01.2 Multi-Rate Serial Data Interface Physical Layer Lattice Semiconductor IP Core User’s Guide Introduction Serial Digital Interface (SDI) is the most popular raw video link standard used in television broadcast studios and video production facilities. Field Programmable Gate Arrays (FPGAs) with SDI interface capability can be used for acquisition, mixing, storage, editing, processing and format conversion applications. Simpler applications use FPGAs to acquire SDI data from one or more standard definition (SD) or high definition (HD) sources, perform sim- ple processing and retransmit the video data in SDI format. Such applications require an SDI physical layer (PHY) interface and some basic processing blocks such as a color space converter and frame buffer. In more complex applications, the acquired video receives additional processing, such as video format conversion, filtering, scaling, graphics mixing and picture-in-picture display. FPGA devices can also be used as a bridge between SDI video sources and backplane protocols such as PCI Express or Ethernet, with or without any additional video processing. In an FPGA-based SDI solution, the physical interface portion is often the most challenging part of the solution. This is because the PHY layer includes several device-dependent components such as high speed I/Os (inputs/outputs), serializer/deserializer (SERDES), clock/data recovery, word alignment and timing signal detection logic. Video processing, on the other hand, is algorithmic and is usually achieved using proprietary algorithms developed by in-house teams. The Lattice Multi-Rate SDI PHY Intellectual Property (IP) Core is a complete SDI PHY interface that connects to the high-speed SDI serial data on one side and the formatted parallel data on the other side. -

Alpha HD Capture and Playback (1+1 Or 0+2) HD/SD-SDI PCI-E Card

Professional broadcast solutions Alpha HD Capture and playback (1+1 or 0+2) HD/SD-SDI PCI-e card Description Stream Alpha HD is a PCI-Express card for overlay and YEAR output of computer graphics. It can be used as a basis for WARRANTY creation of on-air graphic design systems (CG-systems) and broadcasting video servers. Features Free SDK/Tools/Drivers • Works with 8 and 10-bit component serial 3G-SDI signal • Windows 7,8,10,Server 2008/12 (32 and 64 bit) , HD-SDI, SD-SDI, DVB-ASI in accordance with ITU-R.601, • Stream Labs API SMPTE 424m, SMPTE 292m, SMPTE 274m, SMPTE 259m • Direct Show Filter и DVB-ASI standards; • Examples for integration in SW and Tools for HW • Automatic activation of video signal relay bypass mode tests upon computer power loss; • Support V4L2 and ALSA • Synchronization from input SDI/HD/3G-SDI signal • Free Sources for C programming language or analog Black burst/tri-level signal. When external • Medialooks SDK synchronization is lacking internal synchronizing generator is applied; • Digital key signal (alpha-channel) output for use with external mixer that has a DSK (Down Stream Key) input. Key signal delay relative to output graphics has a software controlled wide adjustments range; • 16-channels SDI/HD/3G-SDI embedded audio input/ output; • Error control in incoming SDI signals with check total count according to EDH method. EDH packets on the output are formed anew in accordance with SMPTE165 standard. www.stream-labs.com Connection DIAGRAM Specifications Video Input Connector 75-Ohm BNC HDMI Audio Output 1 -

LMH0030 SMPTE 292M/259M Digital Video Serializer with Video And

Integrated Cable Driver LMH0030 SMPTE 292M/259M Digital Video Serializer with Video and Ancillary Data FIFOs and August 2006 LMH0030 SMPTE 292M/259M Digital Video Serializer with Video and Ancillary Data FIFOs and Integrated Cable Driver General Description The LMH0030’s internal circuitry is powered from +2.5V and the I/O circuitry from a +3.3V supply. Power dissipation is The LMH0030 SMPTE 292M/259M Digital Video Serializer typically 430mW at 1.485 Gbps including two 75Ω AC- with Ancillary Data FIFO and Integrated Cable Driver is a coupled and back-matched output loads. The device is pack- monolithic integrated circuit that encodes, serializes and aged in a 64-pin TQFP. transmits bit-parallel digital video data conforming to SMPTE 125M and 267M standard definition, 10-bit wide component video and SMPTE 260M, 274M, 295M and 296M high- Features definition, 20-bit wide component video standards. The n SDTV/HDTV serial digital video standard compliant LMH0030 operates at SMPTE 259M serial data rates of n Supports 270 Mbps, 360 Mbps, 540 Mbps, 1.4835Gbps 270 Mbps, 360 Mbps, the SMPTE 344M serial data rate of and 1.485 Gbps SDV data rates with auto-detection 540 Mbps, and the SMPTE 292M serial data rates of 1483.5 n Low output jitter: 125ps max, 85ps typical and 1.485 Gbps. The serial data clock frequency is internally n Low power: typically 430mW generated and requires no external frequency setting, trim- n No external serial data rate setting or VCO filtering ming or filtering components. components required* The LMH0030 performs functions which include: parallel-to- n Fast PLL lock time: < 150µs typical at 1.485 Gbps serial data conversion, SMPTE standard data encoding, n Adjustable depth video FIFO for timing alignment NRZ to NRZI data format conversion, serial data clock gen- n Built-in self-test (BIST) and video test pattern generator eration and encoding with the serial data, automatic video (TPG)* rate and format detection, ancillary data packet manage- n Automatic EDH/CRC word and flag generation and ment and insertion, and serial data output driving. -

3G SDI Time Division Multiplexer/De-Multiplexer

datasheet FLASHLINK SDI-TD-3GMX-5 / SDI-TD-3GDX-5 3G SDI time division multiplexer/de-multiplexer This Flashlink 3G-SDI time division Key features multiplexer offers transport of • 4 x SD-SDI + 1 x HD-SDI or 2 x HD into 3G-SDI synchronous or asynchronous SD-/HD-SDI • Transport of 8 x SD-SDI over 3G-SDI when combined signals over an 3G-SDI infrastructure. with HD-TDM The 3G-SDI TDM signal is a fully compliant SMPTE 1080p • Fully SMPTE compliant 3G-SDI TDM link level B signal stream. The card can be configured to • On-board optical transmitter and receiver multiplex two HD-SDI signals into one 3G-SDI, or four SD- SDI and one HD-SDI signals into 3G-SDI. Transport eight SD-SDI signals over one 3G-SDI link by combining these new modules with the existing SDI-TD-MUX/SDI-TD- DMUX. On board optional optics for different transport schemes are available. R1514 nevion.com Equalizer Equalizer HD-SDI/SD-SDI Reclocker Reclocker HD-SDI/SD-SDI Optical 3G-SDI Output Optical 3G-SDI Input Equalizer Equalizer Optical Transmitter Optical Receiver HD-SDI/SD-SDI Reclocker Reclocker HD-SDI/SD-SDI Equalizer Equalizer 2x1 SD-SDI Reclocker TDM-MUX 3G-SDI3G-SDI Change- TDM-DMUX Reclocker SD-SDI InInfrfrasastructurtructuree over Equalizer Equalizer SD-SDI Reclocker Reclocker SD-SDI Electrical 3G-SDI Output Electrical 3G-SDI Input Equalizer Equalizer SD-SDI Reclocker Reclocker SD-SDI Microcontroller Remote Remote Control Microcontroller Control SDI-TD-3GMX-5 SDI-TD-3GDX-5 Common specifications General Power MUX +5V / 5.0W +15V / 1.5W Power DMUX +5 V / 3.9W +15 V / -

Smpte Standard

Rec. ITU-R BT.1616 1 RECOMMENDATION ITU-R BT.1616 Data stream format for the exchange of DV-based audio, data and compressed video over interfaces complying with Recommendation ITU-R BT.1381 (Question ITU-R 12/6) (2003) The ITU Radiocommunication Assembly, considering a) that applications within professional television production and post-production have been identified where DV-based video compression can offer operational and economic advantages when compared to serial digital interface (SDI)-based operations; b) that three data rates have been proposed within the same compression family to serve different applications (25 Mbit/s, 50 Mbit/s and 100 Mbit/s); c) that the sampling rasters for each of the three applications are different; d) that audio, auxiliary data and metadata elements are integral parts of these applications; e) that these elements are multiplexed into a single data stream for transport and further processing; f) that information exchange will be effected through interfaces complying with Recommendation ITU-R BT.1381 for further post-processing and storage; g) that for interconnection of standard definition and high definition equipment ITU-R recommends the use of Recommendations ITU-R BT.656 and ITU-R BT.1120 respectively; h) that for this purpose, the complex data stream must be formatted before injection into the above interface; j) that this format must also describe the parameters needed for the transmission in faster than real-time modes, recommends 1 that for applications in professional television production and post-production using DV-based compression, the elements contained be formatted according to SMPTE 321M-2002 “Data Stream Format for the Exchange of DV-Based Audio, Data and Compressed Video over a Serial Data Transport Interface”.