4/Zzzzzzzz4 70

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Study of Nickel Silicide Processes for Advanced CMOS Applications

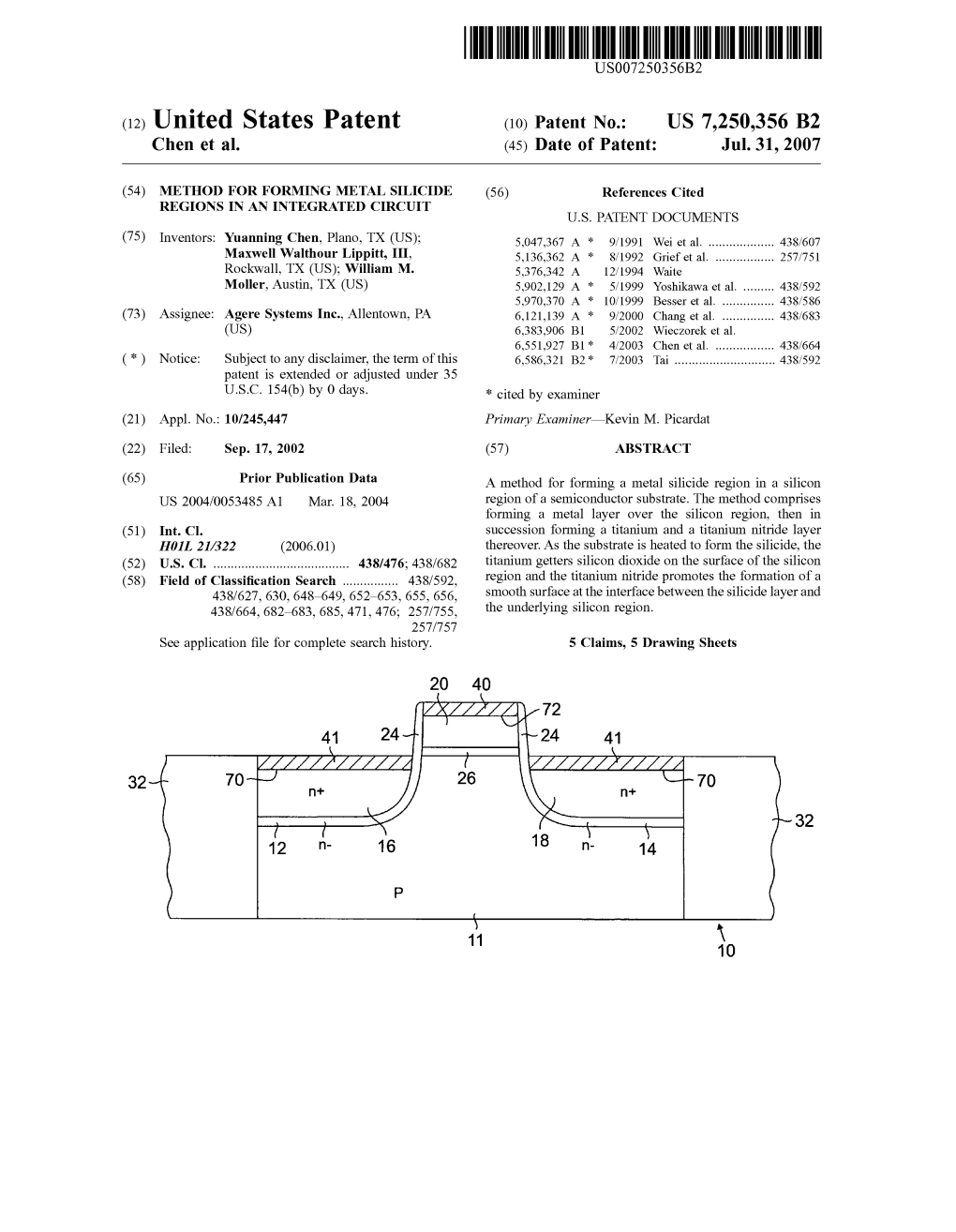

Curanovi~, Branislav 2 ~ Annual Microelectronic Engineering Conference, May 2003 Study of Nickel Suicide Processes for Advanced CMOS Applications Branislav Curanovid, Student Member, IEEE PMOS transistors. In general, today’s CMOS processes Abstract—A study has been performed to determine have many uses for silicides, and are predicted by the critical mechanisms involved in formation of nickel International Technology Roadmap for Semiconductors suicides. The process parameters under investigation were (ITRS) [11 to be very important and relevant for several silicidation temperature, presilicide N5~ implant, and the years into the future. presence of a titanium capping layer. Contact sheet The choice of metals for suicide formation is resistance phosphorous-implanted silicon was measured and determined to degrade with high silicidation becoming crucial, as certain metals have started to temperature. Titanium capping was found to improve approach physical limits associated with their properties. contact resistance and compensate for the effects of high There are three metals that are most frequently used in temperature treatment for polycides. The nitrogen modern suicide formation: titanium, cobalt, and nickel. incorporation via implant shows a degradation in Titanium suicide (TiSi2) has been a long-time resistivity for both silicides and polycides. dominant suicide technology, but has reached extinction in modern deep sub-micrometer CMOS applications. Index Terms—Ni silicidation, nitrogen implant, RTP Although it offers low resistivity when properly formed, TiSi2 exhibits several critical failures. One such failure is the silicon-diffusion dominated formation of silicides I. INTRODUCTION that can lead to problems of bridging. Secondly, TiSi2 exhibits a strong narrow-line effect due to incomplete S microelectronicILICIDES haveindustrybeen usedto forcircumventmany yearsthe inhighthe transition from a high-resistivity C49 phase to the low- resistivity seen when contacting metal to poly gates and resistivity C50 phase. -

Microfabrication and Microfluidics for 3D Brain-On-Chip

Microfabrication and microfluidics for 3D brain-on-chip Bart Schurink Microfabrication and microfluidics for 3D brain-on-chip Bart Schurink i Members of the committee: Chairman Prof. dr. ir. J.M.W. Hilgenkamp (voorzitter) Universiteit Twente Promotor Prof. dr. J.G.E. Gardeniers Universiteit Twente Co-promotor/supervisor Dr. R. Luttge Universiteit Eindhoven Members Prof. dr. J.C.T. Eijkel University of Twente Prof. dr. H.B.J. Karperien University of Twente Prof. dr. A.S. Holmes Imperial College London Prof. dr. ir. J.M.J. den Toonder Technical University of Eindhoven Prof. dr. ir. R. Dekker Delft University of Technology The work in this thesis was carried out in the Mesoscale Chemical Systems group and MESA+ Institute for Nanotechnology, University of Twente. It is part of the MESOTAS project financially supported by ERC, Starting Grant no. 280281 Title: Microfabrication and microfluidics for 3D brain-on-chip Author: Bart Schurink ISBN: 978-90-365-4142-8 DOI: 10.3990/1.9789036541428 Publisher: Gildeprint, Enschede, The Netherlands Copyright © 2016 by Bart Schurink, Enschede, The Netherlands. No part of the this book may be copied, photocopied, reproduced, translated or reduced to any electronic medium or machine-readable form, in whole or in part, without specific permission of the author. ii Microfabrication and microfluidics for 3D brain-on-chip PROEFSCHRIFT ter verkrijging van de graad van doctor aan de Universiteit Twente, op gezag van de rector magnificus, Prof. dr. H. Brinksma, volgens besluit van het College voor Promoties in het openbaar te verdedigen op donderdag 23 juni 2016 door Bart Schurink Geboren op 6 november 1982 te Oldenzaal, Nederland iii Dit proefschrift is goedgekeurd door de promotor: Prof. -

Electrical Characterization of Ni Silicide Formed by Ni Reaction with Scaled Si Nanowires

2013 Master thesis Electrical characterization of Ni Silicide formed by Ni reaction with scaled Si nanowires Department of Electronics and Applied Physics Interdisciplinary Graduate School of Science and Engineering Tokyo Institute of Technology 11M36402 Kazuki Matsumoto Supervisor Prof. Akira Nishiyama and Hiroshi Iwai Abstract of Master Thesis Electrical characterization of Ni Silicide formed by Ni reaction with scaled Si nanowires Supervisor:Prof. Akira Nishiyama and Hiroshi Iwai Department of Electronics and Applied Physics Interdisciplinary Graduate School of Science and Engineering Tokyo Institute of Technology 11M36402 Kazuki Matsumoto February, 2013 Nickel salicide (self-aligned silicide) have been widely used in ULSIs to reduce the parasitic resistance at source and drain regions of MOSFETs. This technology may be continuously used for highly scaled device such as Si nanowire field effect transistors (Si NW FETs) and FinFETs. As source and drain regions become extremely narrow and the amount of Si reacting with Ni is limited in these structures, this may lead to the silicide different from the case of the silicidation of the bulk silicon. On the other hand, it has been reported that the narrow metal lines, for example copper narrow lines, suffer from the increase in effective resistivity due to higher probability of the surface scattering of the electrons. In this study, in order to apply Ni silicide to high scale device, the impact of size effect in Ni silicide nanowires is investigated. Silicidation was performed using Ni thin films and Si nanowire with the line width down to 10 nm. The Ni silicide line width is in the range from 80 nm to 15 nm. -

Stress Modeling of Nanoscale Mosfet

STRESS MODELING OF NANOSCALE MOSFET By NIRAV SHAH A THESIS PRESENTED TO THE GRADUATE SCHOOL OF THE UNIVERSITY OF FLORIDA IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF MASTER OF SCIENCE UNIVERSITY OF FLORIDA 2005 Copyright 2005 by Nirav Shah This work is dedicated to my parents for their unconditional love and support, and without whom, I could not have achieved what I have. ACKNOWLEDGMENTS First and foremost, I would like to thank my advisor, Dr. Scott E. Thompson, for all the support, encouragement and assistance he has given me throughout my graduate studies, and for the opportunity to work with him in the SWAMP group. Despite being really busy, he always found time for his students to discuss research and other technical deliberations. I will always adore his innovative thinking and diligent commitment to research, which I tried to imbibe during my work tenure. I am also very grateful to Dr. Mark E. Law and Dr. William R. Eisenstadt for supporting my research activities and for their guidance and support as my supervisory committee. This research could not have been completed without the financial support of the Semiconductor Research Corporation and Applied Materials Inc. I would like to thank the University of Florida and Department of Electrical and Computer Engineering for giving me an opportunity to explore the wide horizons of the technical arena. I would like to thank the SWAMP group and all its members for their warm support during my research. I appreciate the efforts of Teresa Stevens for being an excellent program assistant. I am grateful to Russ Robison for his assistance to get me acquainted with FLOOPS and his continuous support thereafter. -

CMOS Fabrication

Chapter 7 CMOS Fabrication This chapter presents a brief overview of CMOS process integration. Process integration refers to the well-defined collection of semiconductor processes required to fabricate CMOS integrated circuits starting from virgin silicon wafers. This overview is intended to give the reader a fundamental understanding of the processes required in CMOS integrated circuit fabrication. Moreover, there are strong interactions between circuit design and process integration. For instance, the typical design rule set is determined in large part by the limitations in the fabrication processes. Hence, circuit designers, process engineers, and integration engineers are required to communicate effectively. To this end, we first examine the fundamental processes, called unit processes, required for CMOS fabrication. The primary focus is the qualitative understanding of the processes with limited introduction of quantitative expressions. The unit processes are combined in a deliberate sequence to fabricate CMOS. Additionally, the unit processes are typically repeated numerous times in a given process sequence. Here we present a representative modern CMOS process sequence, also called a process flow. 7.1 CMOS Unit Processes In this section we introduce each of the major processes required in the fabrication of CMOS integrated circuits. We first discuss wafer production. Although wafer production is not a unit process, it is nonetheless important to present the production method which is used by wafer manufacturers. All subsequent discussions are focused on the unit processes incorporated by fabrication facilities to produce integrated circuits. The unit processes are grouped by functionality. Thermal oxidation, doping processes, photolithography, thin-film removal, and thin-film deposition techniques are presented. -

Integration of Metallic Source/Drain Contacts in MOSFET Technology

Integration of Metallic Source/Drain Contacts in MOSFET Technology Doctoral Thesis By Jun Luo Stockholm, Sweden 2010 Integrated Devices and Circuits, School of Information and Communication Technology (ICT), Royal Institute of Technology (KTH) Integration of metallic source/drain contacts in MOSFET technology A dissertation submitted to Kungliga Tekniska Högskolan (KTH), Stockholm, Sweden, in partial fulfillment of the requirements for the degree of Teknologie Doktor (Doctor of Philosophy) TRITA-ICT/MAP AVH Report 2010:06 ISSN 1653-7610 ISRN KTH/ICT-MAP/AVH-2010:06-SE ISBN 978-91-7415-680-5 © Jun Luo, 2010 Cover SEM image: SB-FinFET (Courtesy Valur Gudmundsson) ii Jun, Luo: Integration of metallic source/drain contacts in MOSFET technology, Integrated Devices and Circuits, School of Information and Communication Technology (ICT), Royal Institute of Technology (KTH), Stockholm, Sweden, 2010. TRITA-ICT/MAP AVH Report 2010:06, ISSN 1653-7610, ISRN KTH/ICT-MAP/AVH- 2010:06-SE, ISBN 978-91-7415-680-5 Abstract The continuous and aggressive downscaling of conventional CMOS devices has been driving the vast growth of ICs over the last few decades. As the CMOS downscaling approaches the fundamental limits, novel device architectures such as metallic source/drain Schottky barrier MOSFET (SB-MOSFET) and SB-FinFET are probably needed to further push the ultimate downscaling. The ultimate goal of this thesis is to integrate metallic Ni1-xPtx silicide (x=0∼1) source/drain into SB-MOSFET and SB-FinFET, with an emphasis on both material and processing issues related to the integration of Ni1-xPtx silicides towards competitive devices. First, the effects of both carbon (C) and nitrogen (N) on the formation and on the Schottky barrier height (SBH) of NiSi are studied. -

DIRECT OBSERVATIONS of NICKEL SILICIDE FORMATION on (100) Si and Si0.75Ge0.25 SUBSTRATES USING IN-SITU TRANSMISSION ELECTRON MICROSCOPY

DIRECT OBSERVATIONS OF NICKEL SILICIDE FORMATION ON (100) Si AND Si0.75Ge0.25 SUBSTRATES USING IN-SITU TRANSMISSION ELECTRON MICROSCOPY RAMESH NATH S/O PREMNATH (B.Sc.(Hons.), NUS) A THESIS SUBMITTED FOR THE DEGREE OF MASTER OF SCIENCE DEPARTMENT OF MATERIALS SCIENCE NATIONAL UNIVERSITY OF SINGAPORE 2004 Acknowledgements I would like to express my utmost gratitude and thanks to my supervisor Professor Mark Yeadon for this project accomplishment. Without his patient guidance, this work will not have been possible. From my early days of ignorance, he had been there to provide knowledge, mentorship and assistance whenever difficulties are encountered. I am also grateful for Prof. Yeadon’s invaluable coaching in the handling of his precious transmission electron microscope and the knowledge of the operating techniques and little tricks here and there that he transferred to the me. It is a joy to work with him in the laboratory and get to know him as a friend. I am also deeply indebted to Dr. Christopher Boothroyd for his mentorship and guidance in helping me better understand the principles of the transmission electron microscope and the Gatan Image Filter. The long discussions we had over tea have definitely helped shaped me to be a better microscopist. I would also like to thank Dr. Lap Chan (CSM) for being an excellent teacher and facilitator who has helped to put this project together. I must particularly express my most sincere gratitude to my colleagues and also my friends, Dr. Foo Yong Lim and Soo Chi Wen, for their advice, understanding and help along the way. -

Final Report and Periodic Project Report (Year 3 - 2003)

INFORMATION SOCIETY TECHNOLOGIES (IST) PROGRAMME Future and Emerging Technologies (FET) SODAMOS - project IST-2000-26475 (SOurce Drain Architecture for Advanced MOS technology) Final Report and Periodic Project Report (Year 3 - 2003) Consortium: IEMN/ISEN - CNRS - UC LOUVAIN - ST Microelectronics - IET Operative Commencement date: January 1st, 2001 Duration: 3 years Coordination: E. DUBOIS, IEMN/ISEN, Cité Scientifique, Avenue Poincaré, BP 69 59652 Villeneuve d’Ascq, France [email protected] General Introduction - page -2 SODAMOS - project IST-2000-26475 (SOurce Drain Architecture for Advanced MOS technology) Final Report and Periodic Project Report (Year 3 - 2003) Contents Chapter 0 General Introduction Chapter 1 Material Engineering (Workpackage 1) Chapter 2 Simulation (Workpackage 2) Chapter 3 Device fabrication and characterization (Workpackage 3) Chapter 4 Assessment of the silicide process in industrial environment (Workpackage 4) Chapter 5 General Conclusion General Introduction - page -1 Chapter 0 General Introduction Content page 0.1 Recall of the project objectives 1 0.1.1 Background 1 0.1.2 Position of the problem to solve 1 0.1.3 Solution studied in the frame of the SODAMOS project 3 0.1.4 Goals and organization of the research 4 0.2 Organization of this report 5 0.2.1 Chapter 1: Material engineering (WP1) 5 0.2.2 Chapter 2: Simulation (WP2) 6 0.2.3 Chapter 3: Device fabrication and characterization (WP3) 6 0.2.4 Chapter 4: Assessment of the silicide process in industrial 7 environment (WP4) 0.3 Summary on management and consortium exchanges 8 0.4 Dissemination / publications 9 0.5 Status of deliverables 11 0.6 References of general introduction 14 General Introduction - page 0 Chapter 0 General Introduction 0.1 Recall of the project objectives 0.1.1 Background Normal operation of MOSFETs with ultra-thin gate oxide and effective channel length below 50 nm has been reported in the literature [1][2]. -

Development of Nickel Silicide for Integrated Circuit Technology

Rochester Institute of Technology RIT Scholar Works Theses 2-2006 Development of nickel silicide for integrated circuit technology Phu H. Do Follow this and additional works at: https://scholarworks.rit.edu/theses Recommended Citation Do, Phu H., "Development of nickel silicide for integrated circuit technology" (2006). Thesis. Rochester Institute of Technology. Accessed from This Thesis is brought to you for free and open access by RIT Scholar Works. It has been accepted for inclusion in Theses by an authorized administrator of RIT Scholar Works. For more information, please contact [email protected]. Development of Nickel Silicide for Integrated Circuit Technology A thesis submitted in partial fulfillment of the requirements for the degree of Master of Science in Materials Science & Engineering By PhuDo Materials Science & Engineering Department Rochester Institute of Technology February 2006 Dr. Sean L. Rommel Sean L. Rommel Date: (Thesis Advisor) Santosh K. Kurinec Dr. Santosh Kurinec Date: 0$ (J2f 10 , (Committee Member) , Dr. Surendra K. Gupta S. K. Gupta Date: C.3 I ~2/0-6 (Committee Member) Dr. K.S.V. Santhanam Santhanam KSV Date: !i~i ~ a (Department Head) PhuDo MS Thesis Development of Nickel Silicide for Integrated Circuit Technology By PhuH. Do I, Phu H. Do, hereby grant pennission to the Wallace Memorial Library of the Rochester Institute of Technology to reproduce this document in whole or in part that any reproduction will not be for commercial use or profit. Phu H. Do March 23, 2006 First M. Last Month Day, Year 11 Phu Do MS Thesis Acknowledgement First, I like to thank my thesis advisor, Dr. -

Silicides and Local Interconnections for High- Performance Vlsl Applications

by R. W. Mann L. A. Clevenger Silicides P. D. Agnello and local F. R. White interconnections for high- performance VLSl applications As the minimum VLSl feature sizecontinues reduction through linear "shrinking" of ground rules and to scale down to the 0.1-0.2-pm regime, the device scaling, both common industry practices, places an need for low-resistance local interconnections increased demand on the tolerable limits of interconnection will become increasingly critical. Although resistance. Likewise, the shrinking feature size and circuit reduction in the MOSFET channel length packing density heighten the sensitivity of performance to will remain the dominant factor in achieving the resistivity of circuit conductors and the dielectric higher circuit performance, existing local constants of associated insulators. This has led to an interconnection materials will impose greater increase in the use of silicides with resistivity inherently than acceptable performance limitations. superior to that of degenerately doped silicon in order to We review the state-of-the-art salicide and alleviate the resistance increase associated with reduced polycide processes, with emphasis on work at feature size [l-31. IBM, and discuss the limitations that pertain to While silicides have been introduced to preserve future implementations in high-performance performance, local interconnections have been proposed VLSl circuit applications. A brief review of primarily for density improvement. Local interconnection various silicide-based and tungsten-based approaches involving one additional mask level such as approaches for forming local interconnections HPSAC (high-performance silicided amorphous-silicon is presented, along with a more detailed contact and interconnection technology) [4] and the use description of a tungsten-based "damascene" of a patterned TiN layer [5] were first proposed in 1985.