Silicides and Local Interconnections for High- Performance Vlsl Applications

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Study of Nickel Silicide Processes for Advanced CMOS Applications

Curanovi~, Branislav 2 ~ Annual Microelectronic Engineering Conference, May 2003 Study of Nickel Suicide Processes for Advanced CMOS Applications Branislav Curanovid, Student Member, IEEE PMOS transistors. In general, today’s CMOS processes Abstract—A study has been performed to determine have many uses for silicides, and are predicted by the critical mechanisms involved in formation of nickel International Technology Roadmap for Semiconductors suicides. The process parameters under investigation were (ITRS) [11 to be very important and relevant for several silicidation temperature, presilicide N5~ implant, and the years into the future. presence of a titanium capping layer. Contact sheet The choice of metals for suicide formation is resistance phosphorous-implanted silicon was measured and determined to degrade with high silicidation becoming crucial, as certain metals have started to temperature. Titanium capping was found to improve approach physical limits associated with their properties. contact resistance and compensate for the effects of high There are three metals that are most frequently used in temperature treatment for polycides. The nitrogen modern suicide formation: titanium, cobalt, and nickel. incorporation via implant shows a degradation in Titanium suicide (TiSi2) has been a long-time resistivity for both silicides and polycides. dominant suicide technology, but has reached extinction in modern deep sub-micrometer CMOS applications. Index Terms—Ni silicidation, nitrogen implant, RTP Although it offers low resistivity when properly formed, TiSi2 exhibits several critical failures. One such failure is the silicon-diffusion dominated formation of silicides I. INTRODUCTION that can lead to problems of bridging. Secondly, TiSi2 exhibits a strong narrow-line effect due to incomplete S microelectronicILICIDES haveindustrybeen usedto forcircumventmany yearsthe inhighthe transition from a high-resistivity C49 phase to the low- resistivity seen when contacting metal to poly gates and resistivity C50 phase. -

Bandgap Engineering of Titanium Based Oxynitride Thin Films and Molybdenum Disulfide Thin Films for Photovoltaic Applications

FROESCHLE, MICHAEL R., M.S. Bandgap Engineering of Titanium Based Oxynitride Thin Films and Molybdenum Disulfide Thin Films for Photovoltaic Applications. (2019) Directed by Dr. Hemali P. Rathnayake. 70 pp. The purpose of this project was to investigate the potential of two different material systems for the improvement of solar cell efficiency; one based on a titanium oxynitride system and the other molybdenum disulfide. Both phases of the project utilized different fabrication methods and approach in designing the photovoltaic devices. For the titanium based system (TiNO), thin films were formed using pulsed laser deposition, a phase vapor deposition (PVD) technique. The photovoltaic cells deposited on ITO coated glass with copper electrodes yielded an average power conversion efficiency (PCE) of 4.47%, with a fill factor (FF) of 0.246, open circuit 2 voltage (Voc) of 0.18 V, and a short circuit current density (Jsc) of 58.43 mA/cm . XRD and XPS results provide insight into the materials composition and give evidence of multiple bandgap mediated transfer of charge carriers. For the molybdenum based device, monolayer molybdenum disulfide was incorporated into a current organic-based solar cell (OSC) as an electron transport layer. The active layer consists of a blend of donor Poly(3-hexylthiophene-2,5- diyl) and acceptor PCBM. MoS2 incorporated devices showed improved PCE, at 0.88% compared to that of the control samples which yielded a PCE of 0.22%. BANDGAP ENGINEERING OF TITANIUM BASED OXYNITRIDE THIN FILMS AND MOLYBDENUM DISULFIDE THIN FILMS FOR PHOTOVOLTAIC APPLICATIONS by Michael R. Froeschle A Thesis Submitted to the Faculty of The Graduate School at The University of North Carolina at Greensboro in Partial Fulfillment of the Requirements for the Degree Master of Science Greensboro 2019 Approved by _______________________________ Committee Chair APPROVAL PAGE This thesis written by Michael R. -

Structural and Dynamical Trends in Alkali-Metal

Article pubs.acs.org/JPCC Structural and Dynamical Trends in Alkali-Metal Silanides Characterized by Neutron-Scattering Methods † ‡ † § ∥ † ∥ Wan Si Tang,*, , Mirjana Dimitrievska,*, , Jean-Noel̈ Chotard, Wei Zhou, Raphael̈ Janot, ⊥ † Alexander V. Skripov, and Terrence J. Udovic † NIST Center for Neutron Research, National Institute of Standards and Technology, Gaithersburg, Maryland 20899-6102, United States ‡ Department of Materials Science and Engineering, University of Maryland, College Park, Maryland 20742-2115, United States § National Renewable Energy Laboratory, Golden, Colorado 80401, United States ∥ Laboratoire de Reactivité ́et Chimie des Solides (LRCS), UMR 7314 CNRS, Universitéde Picardie Jules Verne, 33 rue Saint-Leu, 80039 Amiens Cedex, France ⊥ Institute of Metal Physics, Ural Branch of the Russian Academy of Sciences, Ekaterinburg 620990, Russia *S Supporting Information ABSTRACT: Structural, vibrational, and dynamical properties of the mono- and mixed-alkali silanides (MSiH3, where M = K, Rb, Cs, K0.5Rb0.5,K0.5Cs0.5, and Rb0.5Cs0.5) were investigated by various neutron experiments, including neutron powder diffraction (NPD), neutron vibrational spectroscopy (NVS), neutron- scattering fixed-window scans (FWSs), and quasielastic neutron scattering (QENS) measurements. Structural characterization showed that the mixed compounds exhibit disordered (α) and ordered (β) phases for temperatures above and below about 200− 250 K, respectively, in agreement with their monoalkali correspondents. Vibrational and dynamical properties are strongly influenced by the cation environment; in particular, there is a red shift in the band energies of the librational and bending modes with increasing lattice size as a result of changes in the bond lengths and force constants. Additionally, slightly broader spectral features are observed in the case of the mixed compounds, indicating the presence of structural disorder caused by the random distribution of the alkali-metal cations within the lattice. -

Doping Effects on Transition-Metal Silicides: Crystal Structures and Physical Properties of Aluminium Doped Rhenium Silicide

BearWorks MSU Graduate Theses Summer 2020 Doping Effects on Transition-Metal Silicides: Crystal Structures and Physical Properties of Aluminium Doped Rhenium Silicide Victoria DeCocq Missouri State University, [email protected] As with any intellectual project, the content and views expressed in this thesis may be considered objectionable by some readers. However, this student-scholar’s work has been judged to have academic value by the student’s thesis committee members trained in the discipline. The content and views expressed in this thesis are those of the student-scholar and are not endorsed by Missouri State University, its Graduate College, or its employees. Follow this and additional works at: https://bearworks.missouristate.edu/theses Part of the Inorganic Chemistry Commons, and the Materials Chemistry Commons Recommended Citation DeCocq, Victoria, "Doping Effects on Transition-Metal Silicides: Crystal Structures and Physical Properties of Aluminium Doped Rhenium Silicide" (2020). MSU Graduate Theses. 3563. https://bearworks.missouristate.edu/theses/3563 This article or document was made available through BearWorks, the institutional repository of Missouri State University. The work contained in it may be protected by copyright and require permission of the copyright holder for reuse or redistribution. For more information, please contact [email protected]. DOPING EFFECTS ON TRANSITION-METAL SILICIDES: CRYSTAL STRUCTURES AND PHYSICAL PROPERTIES OF ALUMINIUM DOPED RHENIUM SILICIDE A Master’s Thesis -

Appendix a of Final Environmental Impact Statement for a Geologic Repository for the Disposal of Spent Nuclear Fuel and High-Lev

Appendix A Inventory and Characteristics of Spent Nuclear Fuel, High-Level Radioactive Waste, and Other Materials Inventory and Characteristics of Spent Nuclear Fuel, High-Level Radioactive Waste, and Other Materials TABLE OF CONTENTS Section Page A. Inventory and Characteristics of Spent Nuclear Fuel, High-Level Radioactive Waste, and Other Materials ................................................................................................................................. A-1 A.1 Introduction .............................................................................................................................. A-1 A.1.1 Inventory Data Summary .................................................................................................... A-2 A.1.1.1 Sources ......................................................................................................................... A-2 A.1.1.2 Present Storage and Generation Status ........................................................................ A-4 A.1.1.3 Final Waste Form ......................................................................................................... A-6 A.1.1.4 Waste Characteristics ................................................................................................... A-6 A.1.1.4.1 Mass and Volume ................................................................................................. A-6 A.1.1.4.2 Radionuclide Inventories ...................................................................................... A-8 A.1.1.4.3 -

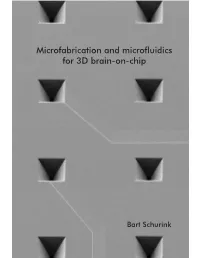

Microfabrication and Microfluidics for 3D Brain-On-Chip

Microfabrication and microfluidics for 3D brain-on-chip Bart Schurink Microfabrication and microfluidics for 3D brain-on-chip Bart Schurink i Members of the committee: Chairman Prof. dr. ir. J.M.W. Hilgenkamp (voorzitter) Universiteit Twente Promotor Prof. dr. J.G.E. Gardeniers Universiteit Twente Co-promotor/supervisor Dr. R. Luttge Universiteit Eindhoven Members Prof. dr. J.C.T. Eijkel University of Twente Prof. dr. H.B.J. Karperien University of Twente Prof. dr. A.S. Holmes Imperial College London Prof. dr. ir. J.M.J. den Toonder Technical University of Eindhoven Prof. dr. ir. R. Dekker Delft University of Technology The work in this thesis was carried out in the Mesoscale Chemical Systems group and MESA+ Institute for Nanotechnology, University of Twente. It is part of the MESOTAS project financially supported by ERC, Starting Grant no. 280281 Title: Microfabrication and microfluidics for 3D brain-on-chip Author: Bart Schurink ISBN: 978-90-365-4142-8 DOI: 10.3990/1.9789036541428 Publisher: Gildeprint, Enschede, The Netherlands Copyright © 2016 by Bart Schurink, Enschede, The Netherlands. No part of the this book may be copied, photocopied, reproduced, translated or reduced to any electronic medium or machine-readable form, in whole or in part, without specific permission of the author. ii Microfabrication and microfluidics for 3D brain-on-chip PROEFSCHRIFT ter verkrijging van de graad van doctor aan de Universiteit Twente, op gezag van de rector magnificus, Prof. dr. H. Brinksma, volgens besluit van het College voor Promoties in het openbaar te verdedigen op donderdag 23 juni 2016 door Bart Schurink Geboren op 6 november 1982 te Oldenzaal, Nederland iii Dit proefschrift is goedgekeurd door de promotor: Prof. -

Low Temperature Chemical Vapor Deposition and Method for Depositing a Tungsten Silicide Film with Improved Uniformity and Reduced Fluorine Concentration

Europaisches Patentamt 19 European Patent Office Office europeen des brevets © Publication number : 0 591 086 A2 12 EUROPEAN PATENT APPLICATION © Application number : 93480132.5 © int. ci.5: H01L 21/3205, C23C 16/44, C23C 16/42, H01L 21/285 @ Date of filing : 10.09.93 The application is published incomplete as filed @ Inventor : Gow, Thomas Richard (Article 93 (2) EPC). The points in the 4 Lyman Drive description at which the omission obviously Williston, VT 05495 (US) occurs have been left blank. Inventor : Lebel, Richard John Box 2255A RD1 © Priority : 30.09.92 US 954783 Sheldon, VT 05483 (US) @ Date of publication of application : @ Representative : Klein, Daniel Jacques Henri 06.04.94 Bulletin 94/14 Compagnie IBM France Departement de Propriete Intellectuelle @ Designated Contracting States : F-06610 La Gaude (FR) DE FR GB © Applicant : International Business Machines Corporation Old Orchard Road Armonk, N.Y. 10504 (US) © Low temperature chemical vapor deposition and method for depositing a tungsten silicide film with improved uniformity and reduced fluorine concentration. © A tungsten silicide (WSix) film is formed by GROWTH RATE ( mg/m i n ) chemical vapor deposition using the reduction of tungsten hexafluoride (WF6) with dichlorosi- O — ro lane (SiH2CI2) referred to as DCS and a reduc- ing agent comprising silane (SiH4), hydrogen, or a mixture thereof. According to the method of the present invention, the WSix film is formed in a CVD reactor operating at a low pressure and at a wafer temperature between about 300 and 550°C. In the preferred embodiment, a thin nucleation layer is deposited before the WSix film. -

Tailoring of Transition Metal Silicides As Protective Thin Films On

THESIS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY Tailoring of Transition Metal Silicides as Protective Thin Films on Austenitic Stainless Steel PUI LAM TAM Department of Materials and Manufacturing Technology CHALMERS UNIVERSITY OF TECHNOLOGY Gothenburg, Sweden 2011 Tailoring of Transition Metal Silicides as Protective Thin Films on Austenitic Stainless Steel PUI LAM TAM ISBN 978-91-7385-560-0 © PUI LAM TAM 2011 Doktorsavhandlingar vid Chalmers tekniska högskola Ny series nr 3241 ISSN 0346-718X Department of Materials and Manufacturing Technology Chalmers University of Technology SE-412 96 Gothenburg Sweden Tel: +46 (0)31-772 1000 Fax: +46 (0)31-772 1310 www.chalmers.se Printed by Chalmers Reproservice Göteborg, Sweden 2011 Abstract Transition metal silicide is an important material used in microelectronic devices and a possible candidate for high temperature application. The objective of this study is trying to make use of this material in a new way as protective thin films on engineering materials. The brittle nature of the silicides can thus be compensated by the ductile bulk material and the surface corrosion resistance can be improved. The choices of thin film constituents are targeted at the transition metal elements including titanium (Ti, Z = 22), chromium (Cr, Z = 24), iron (Fe, Z = 26) and nickel (Ni, Z = 28) in combination with silicon (Si, Z = 14) to form the binary-component intermetallic compounds by means of ion-beam sputter deposition, which was carried out in an ultrahigh vacuum (UHV) chamber at 10 -6 Pa. The chosen substrate material is AISI 304 stainless steel. Thin film characterisations were conducted by means of surface analysing instruments: X-ray photoelectron spectrometer (XPS) and grazing incidence X-ray diffractometer (GIXRD). -

The Mechanism Behind the Calcium Aluminum Silicide Ternary Structural Preference and the Origin of Its Semimetal Behavior

THE MECHANISM BEHIND THE CALCIUM ALUMINUM SILICIDE TERNARY STRUCTURAL PREFERENCE AND THE ORIGIN OF ITS SEMIMETAL BEHAVIOR by Torey Elizabeth Semi A thesis submitted to the Faculty and the Board of Trustees of the Colorado School of Mines in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Applied Physics). Golden, Colorado Date Signed: Torey Elizabeth Semi Signed: D.M. Wood Thesis Advisor Golden, Colorado Date Signed: Dr. Thomas Furtak Professor and Head Department of Engineering ii ABSTRACT CaAl2Si2 is the prototype of the CaAl2Si2 class of Zintl structures established to be useful as thermoelectrics. We propose that CaAl2Si2 be interpreted as an ordinary covalently bonded, tetrahedrally coordinated quasi-semiconductor consisting of a large distortion of the wurtzite structure with the almost fully ionized Ca inserted at an interstitial site. We support this interpretation via a structural mapping and calculations for both a charged binary primitive cell and a Si4 primitive cell. Our intent is to explain the unusual structure of the CaAl2Si2 class of semiconductors, the origin of its semimetallic behavior, the basis for its stability and the effect of substituting other column II atoms for Ca on these properties. To be clear, this work does not examine the nature of the true band gap, or the transport coefficients of CaAl2Si2. GW corrections are not discussed, in view of the focus on the origins of stability of this peculiar structure. iii TABLE OF CONTENTS ABSTRACT . iii LIST OF FIGURES . vi LIST OF TABLES . xi ACKNOWLEDGMENTS . xii CHAPTER 1 INTRODUCTION . 1 1.1 Thermoelectric Materials . 2 1.2 Thermoelectric Efficiency . -

Critical Issues in the Heteroepitaxial Growth of Alkaline-Earth Oxides on Silicon J

Critical issues in the heteroepitaxial growth of alkaline-earth oxides on silicon J. Lettieri, J. H. Haeni, and D. G. Schlom Citation: Journal of Vacuum Science & Technology A 20, 1332 (2002); doi: 10.1116/1.1482710 View online: http://dx.doi.org/10.1116/1.1482710 View Table of Contents: http://scitation.aip.org/content/avs/journal/jvsta/20/4?ver=pdfcov Published by the AVS: Science & Technology of Materials, Interfaces, and Processing Articles you may be interested in Theoretical investigation of the alkaline-earth dihydrides from relativistic all-electron, pseudopotential, and density-functional study J. Chem. Phys. 126, 104307 (2007); 10.1063/1.2437213 Interface formation during molecular beam epitaxial growth of neodymium oxide on silicon J. Appl. Phys. 99, 074105 (2006); 10.1063/1.2188051 Hetero-epitaxy of perovskite oxides on GaAs ( 001 ) by molecular beam epitaxy Appl. Phys. Lett. 85, 1217 (2004); 10.1063/1.1783016 In situ observation of epitaxial growth of [Au/Co/Cu] and [Cu/Co/Au] superlattices and their magnetic interface anisotropies J. Appl. Phys. 90, 5104 (2001); 10.1063/1.1413230 Stranski-Krastanov growth of Al on Cr layers during molecular-beam epitaxial growth and its influence on the structure of epitaxial (001) Al/Cr superlattices J. Appl. Phys. 87, 159 (2000); 10.1063/1.371838 Redistribution subject to AVS license or copyright; see http://scitation.aip.org/termsconditions. Download to IP: 128.84.143.26 On: Tue, 16 Jun 2015 17:57:48 Critical issues in the heteroepitaxial growth of alkaline-earth oxides on silicon J. Lettieri, J. H. Haeni, and D. -

Njit-Etd2000-029

Copyright Warning & Restrictions The copyright law of the United States (Title 17, United States Code) governs the making of photocopies or other reproductions of copyrighted material. Under certain conditions specified in the law, libraries and archives are authorized to furnish a photocopy or other reproduction. One of these specified conditions is that the photocopy or reproduction is not to be “used for any purpose other than private study, scholarship, or research.” If a, user makes a request for, or later uses, a photocopy or reproduction for purposes in excess of “fair use” that user may be liable for copyright infringement, This institution reserves the right to refuse to accept a copying order if, in its judgment, fulfillment of the order would involve violation of copyright law. Please Note: The author retains the copyright while the New Jersey Institute of Technology reserves the right to distribute this thesis or dissertation Printing note: If you do not wish to print this page, then select “Pages from: first page # to: last page #” on the print dialog screen The Van Houten library has removed some of the personal information and all signatures from the approval page and biographical sketches of theses and dissertations in order to protect the identity of NJIT graduates and faculty. ABSTRACT SYNTHESIS AND CHARACTERIZATION OF LOW PRESSURE CHEMICALLY VAPOR DEPOSITED BORON NITRIDE AND TITANIUM NITRIDE FILMS by Narahari Ramanuj a This study has investigated the interrelationships governing the growth kinetics, resulting compositions, and properties of boron nitride (B-C-N-H) and titanium nitride (Ti-N-CI) films synthesized by low pressure chemical vapor deposition (LPCVD) using ammonia (NH3)/triethylamine-borane and NH 3/titanium tetrachloride as reactants, respectively. -

1.3.2 MOS Capacitor Phase Shifter

SILICON ELECTRO-OPTIC MODULATOR Fengqiao Dong A Thesis Submitted for the Degree of MPhil at the University of St. Andrews 2011 Full metadata for this item is available in Research@StAndrews:FullText at: http://research-repository.st-andrews.ac.uk/ Please use this identifier to cite or link to this item: http://hdl.handle.net/10023/2532 This item is protected by original copyright Silicon Electro-optic Modulator Fengqiao Dong This thesis is submitted in partial fulfilment for the degree of MPhil at the University of St Andrews September 2011 For my parents i 1. Candidate’s declarations: I, Fengqiao Dong, hereby certify that this thesis, which is approximately 19 000 words in length, has been written by me, that it is the record of work carried out by me and that it has not been submitted in any previous application for a higher degree. I was admitted as a research student in September, 2007 and as a candidate for the degree of MPhil in September, 2007; the higher study for which this is a record was carried out in the University of St Andrews between 2007 and 2011. Date ………… signature of candidate ……… 2. Supervisor’s declaration: I hereby certify that the candidate has fulfilled the conditions of the Resolution and Regulations appropriate for the degree of MPhil in the University of St Andrews and that the candidate is qualified to submit this thesis in application for that degree. Date ………… signature of supervisor ……… 3. Permission for electronic publication: In submitting this thesis to the University of St Andrews I understand that I am giving permission for it to be made available for use in accordance with the regulations of the University Library for the time being in force, subject to any copyright vested in the work not being affected thereby.